SÍLABO

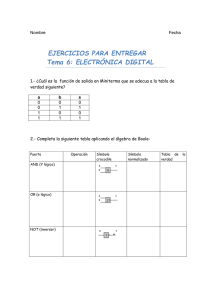

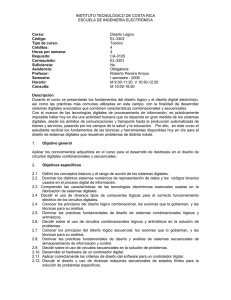

Anuncio

FACULTAD DE INGENIERÍAS Y ARQUITECTURA ESCUELA ACADÉMICO PROFESIONAL DE INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES SISTEMAS DIGITALES I SÍLABO I.-DATOS GENERALES CARRERA PROFESIONAL CÓDIGO CARRERA PROFESIONAL ASIGNATURA CÓDIGO DE ASIGNATURA CÓDIGO DE SÍLABO Nº DE HORAS TOTALES Nº DE HORAS TEORÍA Nº DE HORAS PRÁCTICA Nº DE CRÉDITOS CICLO PRE-REQUISITO TIPO DE CURSO DURACIÓN DEL CURSO CURSO REGULAR EXAMEN SUSTITUTORIO : INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES : 29 : SISTEMAS DIGITALES I : 2902-29213 : 2921330072014 : 5 HORAS SEMANALES : 1 HORAS SEMANALES : 4 HORAS SEMANALES : 3 CRÉDITOS POR CICLO : IV : 2902-29205 : OBLIGATORIO : 18 SEMANAS EN TOTAL : 17 SEMANAS : 1 SEMANA II.-DESCRIPCIÓN DE LA ASIGNATURA Conceptos introductorios. Análisis de circuitos lógicos mediante el uso de álgebra booleana. Diseño de circuitos lógicos. Simplificación de funciones de Boole. Sistemas numéricos y códigos. Circuitos aritméticos. Circuitos lógicos para el manejo de datos. FlipFlops. Introducción a los sistemas secuenciales. Laboratorio. III.-OBJETIVOS ESPECÍFICOS Proporcionar técnicas de análisis y diseño de Circuitos Combinacionales y Secuenciales básicos. Desarrollar el razonamiento lógico para resolver los problemas mediante las técnicas digitales. CICLO IV SISTEMAS DIGITALES I Página 1 de 5 FACULTAD DE INGENIERÍAS Y ARQUITECTURA ESCUELA ACADÉMICO PROFESIONAL DE INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES SISTEMAS DIGITALES I El alumno al término del curso podrá realizar el diseño de circuitos combinacionales y secuenciales síncronos básicos como alternativa de solución a problemas electrónicos, para ello realizará circuitos en laboratorio y simulación con ayudas IV.-METODOLOGÍA El curso teórico se complementará con talleres de laboratorio, trabajos de investigación y visitas guiadas. V.-EVALUACIÓN Asistencia: Obligatoria NF = 30% EP + 30% EF + 40% PP Donde: NF = Nota Final EP = Examen Parcial EF = Examen Final PP = Prácticas Calificadas VI.- CONTENIDO * Semana 01: UNIDAD I: LÓGICA DIGITAL Y SISTEMAS DE NUMERACIÓN Introducción. Sistemas de numeración: binario, decimal, hexadecimal. Conversión entre sistemas. Operaciones binarias: suma, resta, complemento. Otros códigos binarios: BCD, GRAY, EXCESO 3, 4221, JOHNSON. Semana 02: UNIDAD 2 (02 semanas): COMPUERTAS, FUNCIONES Y FAMILIAS LOGICAS Compuertas lógicas: AND, OR, XOR, NOT, NAND, NOR, XNOR. Descripción, símbolos, tablas de verdad y circuitos integrados. Propiedades fundamentales. Funciones lógica. Implementación. Compuertas universales. CICLO IV SISTEMAS DIGITALES I Página 2 de 5 FACULTAD DE INGENIERÍAS Y ARQUITECTURA ESCUELA ACADÉMICO PROFESIONAL DE INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES SISTEMAS DIGITALES I Semana 03: Famílias lógicas: TTL, CMOS, ECL, MOS, CMOS, I2L. Características. Escalas de integración. Fabricantes de circuitos integrados. Series de la familia TTL. Parámetros de funcionamiento de las familias lógicas. Comparación entre las series de la familia TTL. Semana 04: UNIDAD 3 (03 semanas) : REDUCCION DE FUNCIONES LOGICAS Simplificación de funciones por el Método del Mapa de Karnaugh. Términos Irrelevantes. Semana 05: Método de Implicantes Primos. Semana 06: Simplificación de producto de sumas y suma de productos. Semana 07: UNIDAD 4 (05 semanas): SISTEMAS LÓGICOS COMBINACIONALES Análisis y Diseño de Circuitos Combinacionales. Lógica MSI: Sumador medio, sumador completo, sumador paralelo binario, sumador decimal (BCD). Semana 08: Comparadores, Codificadores. Decodificadores. Manejadores de siete segmentos. Semana 09: EXAMEN PARCIAL Semana 10: Multiplexores. Demultiplexores. Comparadores. Generadores y detectores de paridad. Semana 11: Memorias ROM. Dispositivos lógicos programables (PLDs). CICLO IV SISTEMAS DIGITALES I Página 3 de 5 FACULTAD DE INGENIERÍAS Y ARQUITECTURA ESCUELA ACADÉMICO PROFESIONAL DE INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES SISTEMAS DIGITALES I Semana 12: Proyectos en sistemas digitales. Semana 13: UNIDAD 5 ( 04 SEMANAS): LOGICA SECUENCIAL Circuitos secuenciales. Conceptos. Modos: nivel, flanco, reloj. Concepto de Flip-Flop. Semana 14: Lógica secuencial. Tipos de circuitos secuenciales. Latchs y flip-flops. Latch asíncrono tipo RS con compuertas NOR. Latch asíncrono tipo RS con compuertas NAND. Latch síncrono tipo RS. Latch síncrono tipo D. Latch síncrono tipo JK. Semana 15: Latch síncrono tipo T. Latch tipo RS maestro-esclavo. Latch JK maestro-esclavo. Flip-flop tipo D por flanco positivo. Entradas asíncronas. Semana 16: Entradas Asíncronas y Síncronas de Flip-Flop. Diagramas de tiempo. Contadores. Definición. Tipos: Asíncronos, síncronos. Diseco de contadores. Diagramas de tiempo de contadores. Registros. Definición. Tipos. Semana 17: EXAMEN FINAL Semana 18: EXAMEN SUSTITUTORIO VII.- BIBLIOGRAFÍA BIBLIOGRAFÍA BÁSICA Lógica Digital y Diseño de Computadoras, M. MORRIS MANO, Prentice Hall, México. Warkerly, jhon f. : “Diseño digital; principios y prácticas” CICLO IV SISTEMAS DIGITALES I Página 4 de 5 FACULTAD DE INGENIERÍAS Y ARQUITECTURA ESCUELA ACADÉMICO PROFESIONAL DE INGENIERÍA ELECTRÓNICA Y TELECOMUNICACIONES SISTEMAS DIGITALES I Pearson education inc. - 4ta. Edic. – 2005 BIBLIOGRAFÍA COMPLEMENTARIA Digital Computer Design Fundamentals, YAOHAN CHU, McGraw Hill, USA. EJERCICIOS BÁSICOS DE SISTEMAS DIGITALES. García Zubía, J. Ed. Universidad de Deusto, 2005. Circuitos digitales, JORGE Y JUAN GARCIA VILLARREAL, Ceiu Principios de diseño lógico digital Norman baladanian y Bradley Carlson BIBLIOGRAFÍA ELECTRÓNICA CICLO IV http// WWW.COMUNIDAD DE ELECTRONICOS.COM http// WWW. ELECTRÓNICA FACIL.COM http// WWW.ROMALO.COM SISTEMAS DIGITALES I Página 5 de 5