ARQUITECTURAS ESPECIALES

Anuncio

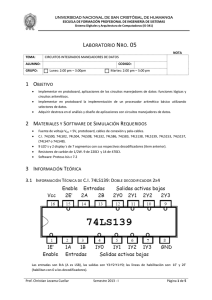

DECODIFICADORES EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 1 ARQUITECTURAS ESPECIALES DECODIFICADORES DECODIFICADOR EL - 3307 Diseño Lógico • Es un circuito combinacional, cuya función es la de convertir un código binario de entrada (natural, BCD, etc.) de “N” bits de entrada a “M” líneas de salida (N puede ser cualquier entero y M es un entero menor o igual a 2N), tales que cada línea de salida será activada para una sola de las combinaciones posibles de entrada. • Estos circuitos, normalmente, se suelen encontrar como decodificador / demultiplexor. • Esto es debido a que un demultiplexor puede comportarse como un decodificador. Ing. José Alberto Díaz García Página 2 http://es.wikipedia.org/wiki/Decodificador DECODIFICADORES CODIFICADORES n entradas . . . Codificador binario . . . m = 2n salidas EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 3 Solo una salida puede estar activa en un mismo instante DECODIFICADORES Ejemplos de Decodificadores EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 4 • Decodificador de 1 a 2 líneas A D0 D1 D0 5 A 0 1 1 0 (a) 0 1 D1 5 A A (b) DECODIFICADORES Ejemplo de decodificadores EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 5 • Decodificador de 2 a 4 líneas A0 A1 A0 D0 D1 D2 D3 A1 0 0 1 1 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 D0 5 A1 A0 D1 5 A1 A0 (a) D2 5 A1 A0 Note that the 2-4-line made up of 2 1-to-2line decoders and 4 AND gates. D3 5 A1 A0 (b) DECODIFICADORES Estructura de los decodificadores EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 6 • Los decodificadores son circuitos lógicos con dos niveles de compuertas, y una lógica de control. – Un primer nivel donde se generan las señales de entrada, normalmente se compone de inversores, esto es compuertas NOT. – Un segundo nivel con compuertas del tipo AND o NAND, que generan los términos de salida. • La lógica de control permite colocar varios decodificadores en cascada o seleccionarlo en el momento oportuno DECODIFICADORES Estructura de los decodificadores EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 7 Primer nivel de compuertas Lógica de control Segundo nivel de compuertas DECODIFICADORES Decodificador 74LS138 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 8 • El 74LS138 es un decodificador de tres entradas que produce ocho salidas activas en nivel bajo, con tres entradas de control. • Es un circuito integrado muy utilizado en la selección de dispositivos. • La tabla de verdad se muestra a continuación • Como se puede observar las funciones de salida solo dependen de un mintérmino, no de un conjunto de ellos. DECODIFICADORES Diagrama lógico del 74LS138 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 9 DECODIFICADORES Expansión del decodificador EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 10 • ¿Que sucede si queremos utilizar un decodificador de 16 líneas de salida si solo contamos con circuitos integrados 74LS138?. • Lo primero es que las señales de entrada se incrementan en una variables. • Se necesitan más de un decodificador 74LS138, por lo menos dos. • Se deben utilizar las señales de control con el fin de seleccionar los diferentes circuitos integrados, esto es una lógica para la selección de los diferentes decodificadores DECODIFICADORES Múltiples decodificadores 1 2 3 A B C D 1 2 1 2 3 6 4 5 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 11 6 4 5 Lógica de selección A B C G1 G2A G2B A B C G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 15 14 13 12 11 10 9 7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 Y10 Y11 Y12 Y13 Y14 Y15 DECODIFICADORES Múltiples decodificadores EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 12 • Si se quiere diseñar un decodificador de 32 salidas utilizando varios 74LS138 • Se debe agregar dos variables más, y utilizar por lo menos cuatro 74LS138. • Respecto a la lógica de control se puede utilizar otro 74LS138 con el fin de reducir la cantidad de componentes en el proceso de selección de los decodificadores Múltiples decodificadores DECODIFICADORES VCC EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 13 1 2 3 A B C 6 4 5 VCC D E 1 2 3 6 4 5 A B C G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 1 2 3 6 4 5 1 2 3 6 4 5 Lógica de selección 1 2 3 6 4 5 A B C G1 G2A G2B A B C G1 G2A G2B A B C G1 G2A G2B A B C G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 15 14 13 12 11 10 9 7 15 14 13 12 11 10 9 7 15 14 13 12 11 10 9 7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 Y10 Y11 Y12 Y13 Y14 Y15 Y16 Y17 Y18 Y19 Y20 Y21 Y22 Y23 Y24 Y25 Y26 Y27 Y28 Y29 Y30 Y31 DECODIFICADORES EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 14 Decodificador de siete segmentos • Este circuito descodifica la información de entrada en binario para producir las señales necesarias para encender LED colocados en un arreglo como el que se muestra. • Normalmente este decodificador es el 7447 o 7448, depende de si el arreglo de los LEDs es de ánodo común o de cátodo común. DECODIFICADORES Decodificador de 7 segmentos 74LS47 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 15 • Es un decodificador de BCD a 7 segmentos. • Sus salidas son activas en nivel bajo, cero voltios. • Normalmente se utiliza con una pantalla de siete segmentos en configuración de ánodo común. DECODIFICADORES Tabla de verdad del 74LS47 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 16 Circuito interno del 74LS47 Minterminos DECODIFICADORES Entradas EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 17 Lógica de control Compuertas OR de salida DECODIFICADORES 7447 Manejando un display de siete segmentos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 18 DECODIFICADORES Aplicación EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 19 • Pantalla para cuatro dígitos decimales implementada con 4 dígitos de siete segmentos. DECODIFICADORES Implementación de funciones lógicas EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 20 • Normalmente las funciones lógicas expresadas en mintérminos tienen dos niveles de compuertas: un primer nivel de compuertas AND que corresponden a los mínterminos presentes en la solución de la función de salida, y un nivel de compuertas OR que corresponden a la unión de todos los mintérminos presentes en la función de salida. • Como los decodificadores tienen una estructura de compuertas AND en la etapa de salida, correspondientes a todos los mintérminos que genera el posible código, estos se podrían utilizar para implementar cualquier función lógica que los necesite. • Entonces los decodificadores con ayuda de compuertas lógicas externas, se pueden utilizar para implementar configuraciones de funciones lógicas. DECODIFICADORES Ejemplo EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 21 • Este ejemplo pretende mostrar la utilización de un decodificador en la generación de funciones booleanas • Consiste del diseño de un circuito combinacional con dos variables de entrada activas en nivel alto que producen cuatro salidas activas en nivel alto. A B Sistema lógico combinacional S0 S1 S2 S3 DECODIFICADORES Ejemplo EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 22 • La siguiente tabla de verdad muestra el comportamiento del sistema de dos variables de entrada y cuatro funciones de salida ENTRADAS SALIDAS A B S3 S2 S1 S0 0 0 1 1 1 0 0 1 1 1 0 1 1 0 1 0 1 1 1 1 0 1 1 1 DECODIFICADORES Ejemplo de funciones lógicas (Cont.) EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 23 • Entonces tenemos los siguientes modelos lógicos para las salidas: S 3 = A B + A B + AB S 2 = A B + A B + AB S1 = A B + AB + AB S 0 = A B + AB + AB DECODIFICADORES Modelos lógicos EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 24 • Entonces los modelos lógicos son: S 3 = ∑ (0,1,2) S 2 = ∑ (0,1,3) S1 = ∑ (0,2,3) S 0 = ∑ (1,2,3) DECODIFICADORES CIRCUITO DEL DECODIFICADOR S3 00 S2 01 10 11 S0 EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 25 S1 A B DECODIFICADORES Utilizando un decodificador EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 26 U2A 1 2 13 VCC U1 A B 1 2 3 6 4 5 A B C G1 G2A G2B 12 U2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 3 4 5 74LS10 6 U2C 9 10 11 74LS10 8 74LS10 U3A 74LS138 1 2 13 12 74LS10 DECODIFICADORES Ejemplo EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 27 • Implementar f(Q,X,P) = ∑(0,1,4,6,7) = ∏ (2,3,5) 0 P X Q A 1 B 2 C 3 0 P X f(Q, X, P) Q A 1 B 2 C 3 4 4 5 5 6 6 7 7 (a) f(Q, X, P) (b) DECODIFICADORES Continuación EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 28 0 0 P X Q A 1 B 2 C 3 P X f(Q, X, P) Q A 1 B 2 C 3 4 4 5 5 6 6 7 7 (c) f(Q, X, P) (d) • Todos los casos anteriores son equivalentes DECODIFICADORES Aplicaciones EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 29 • La memoria de un Microprocesador – Selección de diferentes bancos de memoria. • Sistemas de entrada/salida del microprocesador – Selección de diferentes dispositivos • Decodificación de instrucciones en un microprocesador – Habilitar diferentes unidades funcionales • Chips de memoria – Habilita diferentes filas de memoria dependiendo de la dirección. • Otras aplicaciones DECODIFICADORES Aplicaciones EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 30 • Su función principal es la de direccionar espacios de memoria. Un descodificador de N entradas puede direccionar 2N espacios de memoria. • Para poder direccionar 1KB de memoria necesitaría 10 bits, ya que la cantidad de salidas seria 210, igual a 1024. • De esta manera: Con 20 bits => 220 = 1Mb; Con 30 bits => 230 = 1Gb, etc. DECODIFICADORES BIBLIOGRAFIA EL - 3307 Diseño Lógico Ing. José Alberto Díaz García Página 31 • http://es.wikipedia.org/wiki/Codificad or, consultado el 16 de julio del 2007 • http://www.ti.com/, consultado el 2 de setiembre del 2007 • Fletcher, William I. An Engineering approach to digital design, Prentince Hall, Inc. Primera edición, USA, 1980