Práctico 2

Anuncio

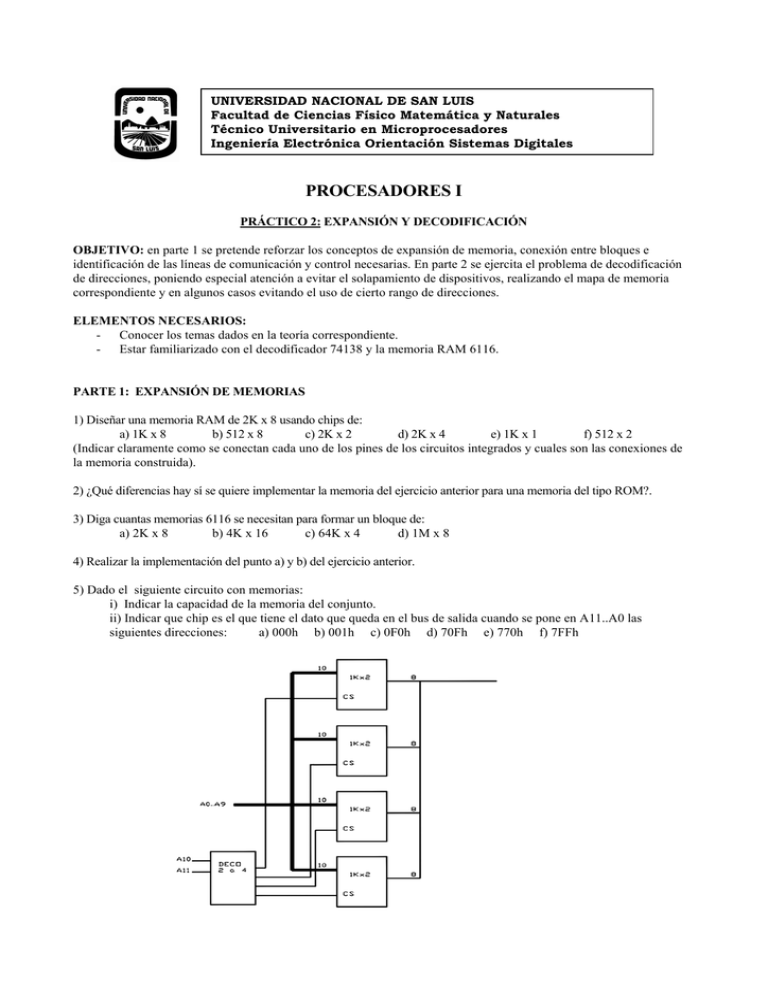

UNIVERSIDAD NACIONAL DE SAN LUIS Facultad de Ciencias Físico Matemática y Naturales Técnico Universitario en Microprocesadores Ingeniería Electrónica Orientación Sistemas Digitales PROCESADORES I PRÁCTICO 2: EXPANSIÓN Y DECODIFICACIÓN OBJETIVO: en parte 1 se pretende reforzar los conceptos de expansión de memoria, conexión entre bloques e identificación de las líneas de comunicación y control necesarias. En parte 2 se ejercita el problema de decodificación de direcciones, poniendo especial atención a evitar el solapamiento de dispositivos, realizando el mapa de memoria correspondiente y en algunos casos evitando el uso de cierto rango de direcciones. ELEMENTOS NECESARIOS: - Conocer los temas dados en la teoría correspondiente. - Estar familiarizado con el decodificador 74138 y la memoria RAM 6116. PARTE 1: EXPANSIÓN DE MEMORIAS 1) Diseñar una memoria RAM de 2K x 8 usando chips de: a) 1K x 8 b) 512 x 8 c) 2K x 2 d) 2K x 4 e) 1K x 1 f) 512 x 2 (Indicar claramente como se conectan cada uno de los pines de los circuitos integrados y cuales son las conexiones de la memoria construida). 2) ¿Qué diferencias hay sí se quiere implementar la memoria del ejercicio anterior para una memoria del tipo ROM?. 3) Diga cuantas memorias 6116 se necesitan para formar un bloque de: a) 2K x 8 b) 4K x 16 c) 64K x 4 d) 1M x 8 4) Realizar la implementación del punto a) y b) del ejercicio anterior. 5) Dado el siguiente circuito con memorias: i) Indicar la capacidad de la memoria del conjunto. ii) Indicar que chip es el que tiene el dato que queda en el bus de salida cuando se pone en A11..A0 las siguientes direcciones: a) 000h b) 001h c) 0F0h d) 70Fh e) 770h f) 7FFh UNIVERSIDAD NACIONAL DE SAN LUIS Facultad de Ciencias Físico Matemática y Naturales Técnico Universitario en Microprocesadores Ingeniería Electrónica Orientación Sistemas Digitales PARTE 2: DECODIFICACIÓN DE DIRECCIONES 6) Diseñar un decodificador de direcciones, que se conectará a un microprocesador, cuyo bus de direcciones es de 16 bits y cuyo bus de datos es de 8 bit, este decodificador deberá seleccionar 6 bloques de memoria ROM de 256x8 cada una y 4 bloques de memoria RAM de 256x8, realizar el decodificador usando CI 74138 (pueden usarse varios 74138). G1 L X X H H H H H H H H /G2A X H X L L L L L L L L /G2B X X H L L L L L L L L A X X X 0 0 0 0 1 1 1 1 B X X X 0 0 1 1 0 0 1 1 C X X X 0 1 0 1 0 1 0 1 E0 E1 E2 E3 E4 E5 E6 E7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 7) Diseñar un decodificador de direcciones, que se conectará a un microprocesador, cuyo bus de direcciones es de 12 bits y cuyo bus de datos es de 8 bit, este decodificador deberá seleccionar: - 6 bloques de memoria ROM de 256x4 - 4 bloques de memoria RAM de 256x4 - 1 entradas de 2x8 - 1 salida de 4x8 Realizar el decodificador usando CI 74138 (pueden usarse varios 74138). Está permitido acceder en mas de una dirección a cualquiera de los dispositivos conectados. 8) Implementar un decodificador, usando decodificadores 74138 e inversores, que permita conectar a un microprocesador de 16 bits de direcciones y 8 bits de datos lo siguiente: - una ROM de 512 x 8 - una RAM de 1K x 8 - una RAM de 4K x 8 - una salida de 8bits - 8 entradas de 8 bits cada una, todas ellas manejadas por un mismo C.I. UNIVERSIDAD NACIONAL DE SAN LUIS Facultad de Ciencias Físico Matemática y Naturales Técnico Universitario en Microprocesadores Ingeniería Electrónica Orientación Sistemas Digitales 9) Realizar una unidad de cómputo con un microprocesador de 16 bits de direcciones y 8 bits de datos y con señales de control READ y WRITE separadas que contenga los siguiente elementos: - 1 μProcesador - 2 memorias ROM de 512 x 8 - 1 RAM de 1K x 8 - 1 RAM de 2K x 8 - 1 chip con 8 entradas de 8 bits c/u. - 2 chips con 4 puertos de salida de 8 bits c/u. a) Realizar un esquema de conexión indicando claramente todas las líneas que ingresan a cada chip (direcciones, datos, read, write). b) Diseñar el decodificador con 74138 y inversores (no usar compuertas lógicas). c) Realizar el mapa de memoria. NOTA: NO SE PUEDEN USAR LAS DIRECCIONES desde la 1000h a la 3FFFh, ni desde la A000h a la CFFFh. 10) Idem al ejercicio anterior pero ahora las memorias a conectar son: - 3 ROM de 1K x 8 - 2 RAM de 512 x 8 - 4 RAM de 1K x 4 NOTA: las DIRECCIONES NO PERMITIDAS son desde la 0000h a la 0400h y desde la B000h a la DFFFh. BIBLIOGRAFÍA: - Diseño Digital Principios y Prácticas - John Wakerly (Capítulo 7). Memory Data Book - National. Series 8000 Microprocessor Family Handbook - National Semiconductor. Nonvolatile Memory - Atmel Algunas hojas de datos en http://linux0.unsl.edu.ar/~mpasi