136 Desarrollo de Subsistemas para Prototipado Rápido de

Anuncio

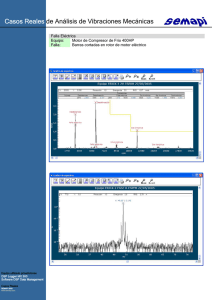

DESARROLLO DE SUBSISTEMAS PARA PROTOTIPADO RÁPIDO DE EQUIPOS DIGITALES José A. Rapallini Antonio A. Quijano Martín P. Argoitía Alejandro H. Manzo Centro de Técnicas Analógico Digitales (CeTAD) - Codiseño HW / SW Facultad de Ingeniería. Universidad Nacional de La Plata josrap@ing.unlp.edu.ar quijano@ing.unlp.edu.ar martinargoitia@yahoo.com.ar amanzo@infovia.com.ar RESUMEN 1. INTRODUCCIÓN Al utilizar herramientas informáticas combinadas con sistemas de desarrollo electrónico, con el objetivo de obtener un diseño en un lapso de tiempo acotado, con su correspondiente evaluación, implementación y pruebas de campo, se observa que normalmente no es posible obtenerlas fácilmente desde el mercado y mas aún, como en nuestro caso, cuando se tiene como fin último el desarrollo de componentes tipo ASIC. Para suplir estos problemas se presenta, como diagrama de bloques, la solución utilizada en el CeTAD (Fig. 1) y los detalles particulares del subsistema utilizado para procesadores digitales de señales (DSP), comentándose los pasos realizados y los ensayos de laboratorio para la demostración de funcionalidad. Cuando se intenta realizar un diseño electrónico de cierta complejidad y con características heterogéneas, es necesario contar con herramientas que auxilien al diseñador en la realización de las mismas en tiempo y forma. Una buena solución para realizar esta tarea es trabajar con la metodología de Codiseño Hardware / Software [14]. Al abordarla, el equipo de trabajo se enfrenta a distintas necesidades: programas para la simulación funcional, herramientas de particionamiento, sistemas de desarrollo tanto para hardware como para software, etc. Partiendo de ambientes EDA, se trata de potenciarlos, incorporando subsistemas que permiten resolver un diseño electrónico en forma integral. En el esquema de la Fig. 1 se pueden observar los distintos bloques que constituyen el siste- Entorno de desarrollo de Codiseño HS Salida de simulación funcional (VHDL, C) Partición y Selección de componentes Interfaces de adaptación y comunicación Fig. 1: Esquema para el diseño de prototipos de sistemas digitales heterogéneos. Placas y entornos de desarrollo para ADQ [1] Entorno de desarrollo National Instruments [5] Placas y entornos de desarrollo para EPL / FPGA [2] Entorno de desarrollo Altera [6] Placas y entornos de desarrollo para procesadores [3], [9] Entorno de desarrollo comercial Motorola [7] Placa programación para DSP [4] Entorno de desarrollo del DSP [8] ma general planteado; en él se pueden observar partes correspondientes a sistemas ya conocidos en la metodología de codiseño HS, que se resuelven con herramientas como a) Ptolemy [16], que se utiliza para el modelado, simulación, y diseño de sistemas embebidos en tiempo real en forma concurrente, b) PeaCE (Ptolemy extension as Codesign Environment) [20][21] el cual es un ambiente de codiseño para la realización rápida de un desarrollo de sistemas digitales heterogéneos, en particular para microsistemas (system-on-chip SOC), basado en el Núcleo de Ptolemy y, desarrollado en el ‘Laboratory of Seoul National University’, en el cual a través del Dominio SPDF (Synchronous Piggybacked Dataflow), introduce una modificación de la semántica SDF (Synchronous Dataflow) original de Ptolemy, c) Metropolis (Ambiente de diseño para sistemas heterogeneos) [13], [14] y otros bloques (ENTORNOS) con soluciones dadas por fabricantes de componentes o sistemas como: Motorola[7], Altera[6], Microchip[3], National Instruments [5], etc, material de uso típico en los laboratorios de electrónica digital. Gracias a este esquema para el diseño de prototipos de sistemas digitales heterogéneos, se pudo lograr en los últimos años en el CeTAD, una serie de trabajos concatenados y con partes reutilizables, que dieron origen a proyectos de graduación que fueron realizados y completados en tiempo y forma [1], [2], [3], [4], [9], [10] y [11]. Con la intención de incrementar la potencialidad de diseño, en el caso particular de esta presentación, se incorpora un sub-sistema de desarrollo con Procesadores de Señales (DSP). Es conocida, la existencia de placas de evaluación y emulación comerciales para desarrollo con DSP, las que normalmente tienen costos excesivos o están preparadas para un tipo de tarea particular, limitando el diseño a un entorno especifico. Desde este punto de vista, se desarrollo este proyecto, que conecta el dispositivo DSP a través de una ‘placa zócalo’, a una placa del tipo multipropósito ‘placa de programación’, la cual se intercomunica a través de interfaces de hardware y software (Interfaces de adaptación y comunicación) al resto del sistema como se indica en la Fig. 1. 2. DESARROLLO DEL TRABAJO En la primera etapa del proyecto, se realizo la selección y estudio de un DSP particular, que permita el desarrollo de sistemas embebidos y resuelva algoritmos en tiempo real típicos como por ejemplo, filtros digitales, Transformada Rápi- da de Fourier (FFT), etc. Se estudiaron y compararon, componentes de Motorola - 56xxx [17] , Analog Devices - ADSP21xxx [18] y Texas Instruments – TMS320Cxx [19], De estos se eligió el TMS320VC33-150, por tener instrucciones de punto flotante, reducida cantidad de pines, espacio de RAM importante y buena velocidad. El mismo tiene una arquitectura interna clásica de tipo Harvard que le permite realizar, simultáneamente y en un único ciclo de máquina, operaciones de multiplicación y suma, así como operaciones con enteros o flotantes de punto flotante. Cuenta además con: temporizadores programables de 32 bits (Timers), periférico de control y gestión de interrupciones que hace este proceso transparente a la CPU, periféricos de control de acceso a memoria, puertos serie sincrónicos, etc. Para realizar el estudio del componente, se diseñó y construyó un circuito impreso (placa zócalo) que incorporó las características necesarias para la utilización del dispositivo en forma apropiada, contando con planos de tierra, desacoples de alimentación, oscilador principal, etc., permitiendo versatilidad en el uso del mismo al realizar pruebas de funcionamiento efectuadas con el generador – analizador lógico HP 16500. Otro aspecto que se tuvo en cuenta fue la obtención de un simulador del dispositivo por software, que permitió entrenarse en la programación [8]. Para realizar la interconexión con una computadora personal (PC) a través del puerto serie del DSP se implementó la placa de programación, cargándose programas y observando los resultados experimentales. Por último, se hicieron programas de características más complejas, para probar la potencialidad del DSP en el ambiente propuesto, como un algoritmo que realiza un filtro coseno; y para comprobar su funcionalidad se obtuvieron señales de salida a través del bus de datos observando los resultados con osciloscopio digital y/o analizador lógico. 3. CONCLUSIONES Se lograron cumplir las perspectivas de potenciar nuestros sistemas de diseño con componentes DSP, no soportados hasta el momento, con el fin de realizar sistemas embebidos que puedan procesar algoritmos en tiempo real. Se diseñó e implementó una placa zócalo cuya función fue manejar fácilmente al componente; se realizó la conexión entre el DSP y la placa prototipo por la cual se ingresan al dispositivo progra- mas desde los entornos de programación de alto y bajo nivel. Por lo tanto se logró realizar un dispositivo versátil para el desarrollo en Codiseño HS, pudiéndose utilizar también en forma independiente cuando la complejidad del sistema a diseñar no es muy elevada. Las pruebas realizadas permiten asegurar la fiabilidad del mismo y abre expectativas interesantes para su utilización en proyectos del CeTAD. 4. REFERENCIAS [1] Gastaldi, G. G., Diseño e implementación de un equipo para la medición de impedancia a tiempo real, Trabajo Final Ing. Electrónica N° 497. Dpto. De Electrotecnia, Fact Ing. UNLP. 15/03/02. [2] Requena, J, Diseño e implementación de Filtros Digitales, Trabajo Final Ing. Electrónica N° 591. Dpto. De Electrotecnia, Fact Ing. UNLP. 17/12/04. [3] Teves, C., Microcontroladores PIC´s , Trabajo Final Ing. Electrónica N° 366. Dpto. De Electrotecnia, Fact Ing. UNLP. 17/11/98. [4] Argoitía, M. - Manzo, A., Diseño de un equipo de desarrollo para DSP , Trabajo Final Ing. Electrónica N° 579. Dpto. De Electrotecnia, Fact. Ing. UNLP. 25/06/04. [5] National Instruments, www.ni.com [6] http://altera.com/products/prd-index.html [7]Microcontroladores Motorola 68 /11/05/08, www.motorola.com [8] Alonso Alejandre - Cubillo Arribas, Simulador del TMS320C3X v.1.0 . Univ. de Valladolid. 2002 [9] Otonello, J. Digitalización de señales y calculo de su FFT con el MC68000.Trabajo Final Ing. Electrónica N° 554. Dpto. De Electrotecnia, Fact Ing. UNLP. 12/09/03 [10] Trataldi, H.; Pando, D., Estudio e implementación de un desplazador en frecuencia para aplicaciones musicales. Trabajo Final Ing. Electrónica N°487. Dpto. De Electrotecnia, Fact. Ing. UNLP. 7/12/01. [11] Gomez, D.; Martinez, S.; Llave electrónica para seguridad de Software, Trabajo Final Ing. Electrónica N° 576. Dpto. De Electrotecnia, Fact Ing. UNLP, 23/04/04. [12] Sangiovanni-Vincentelli, A., Martín, G., Platafrm-Based Desing and Software Desing Methodology for Embedded Systems,Nov-Dic 2003, IEEE [13] Balarin, F y otros, Metropolis: An Integrated Electronic System Desing Enviroment, IEEE Computer Society. Abril 2003. [14]http://embedded.eecs.berkeley.edu/metropolis /methodologies.html [15] Gupta, Pallav, Hardware-software codesign, IEEE Potentials, Enero 2002. [16] UC Berkeley, Department of EECS, The Ptolemy Project, http://ptolemy.eecs.berkeley.edu/ [17] Motorola - 56xxx, www.motorola.com [18] Analog Devices-ADSP21X www.analog.com [19]Texas Instruments –TMS320Cxx www.ti.com [20]PeaCE: Codesign Environment. http:// peace.snu.ac.kr [21] User´s Manual: PeaCE User´s Manual, Version 1.0, Linux, CAP Laboratory of Seoul National University and the Pringet corporation, may 28, 2003.