Final de Junio - Universitat de les Illes Balears

Anuncio

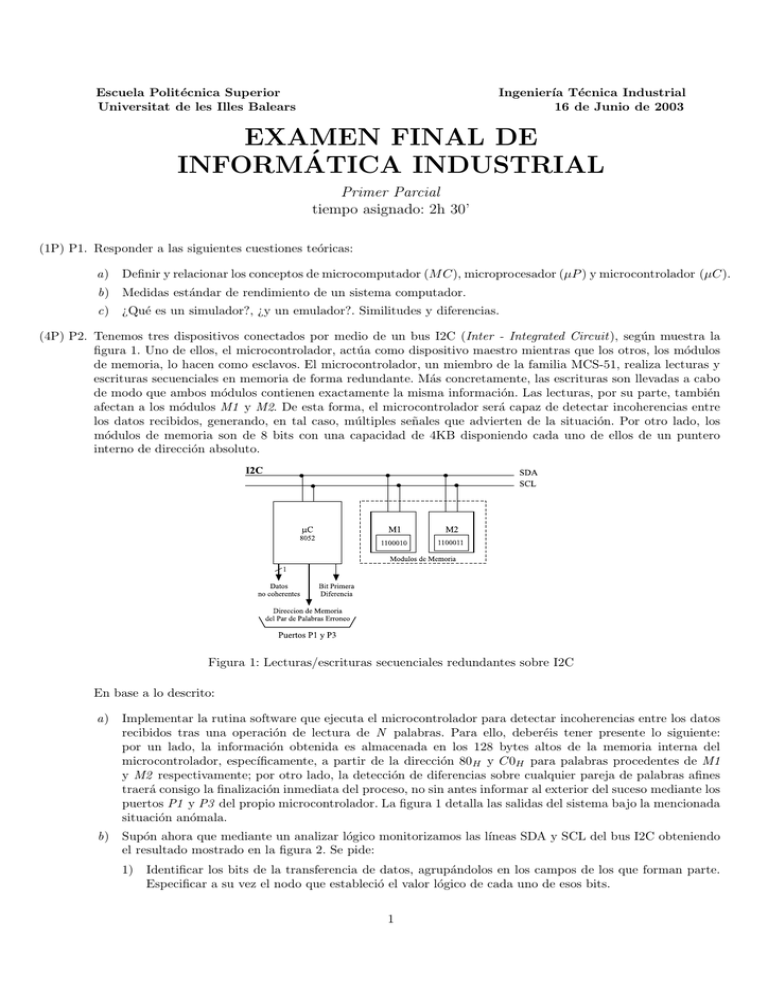

Escuela Politécnica Superior Universitat de les Illes Balears Ingenierı́a Técnica Industrial 16 de Junio de 2003 EXAMEN FINAL DE INFORMÁTICA INDUSTRIAL Primer Parcial tiempo asignado: 2h 30’ (1P) P1. Responder a las siguientes cuestiones teóricas: a) Definir y relacionar los conceptos de microcomputador (M C), microprocesador (µP ) y microcontrolador (µC). b) Medidas estándar de rendimiento de un sistema computador. c) ¿Qué es un simulador?, ¿y un emulador?. Similitudes y diferencias. (4P) P2. Tenemos tres dispositivos conectados por medio de un bus I2C (Inter - Integrated Circuit), según muestra la figura 1. Uno de ellos, el microcontrolador, actúa como dispositivo maestro mientras que los otros, los módulos de memoria, lo hacen como esclavos. El microcontrolador, un miembro de la familia MCS-51, realiza lecturas y escrituras secuenciales en memoria de forma redundante. Más concretamente, las escrituras son llevadas a cabo de modo que ambos módulos contienen exactamente la misma información. Las lecturas, por su parte, también afectan a los módulos M1 y M2. De esta forma, el microcontrolador será capaz de detectar incoherencias entre los datos recibidos, generando, en tal caso, múltiples señales que advierten de la situación. Por otro lado, los módulos de memoria son de 8 bits con una capacidad de 4KB disponiendo cada uno de ellos de un puntero interno de dirección absoluto. Figura 1: Lecturas/escrituras secuenciales redundantes sobre I2C En base a lo descrito: a) Implementar la rutina software que ejecuta el microcontrolador para detectar incoherencias entre los datos recibidos tras una operación de lectura de N palabras. Para ello, deberéis tener presente lo siguiente: por un lado, la información obtenida es almacenada en los 128 bytes altos de la memoria interna del microcontrolador, especı́ficamente, a partir de la dirección 80H y C0H para palabras procedentes de M1 y M2 respectivamente; por otro lado, la detección de diferencias sobre cualquier pareja de palabras afines traerá consigo la finalización inmediata del proceso, no sin antes informar al exterior del suceso mediante los puertos P1 y P3 del propio microcontrolador. La figura 1 detalla las salidas del sistema bajo la mencionada situación anómala. b) Supón ahora que mediante un analizar lógico monitorizamos las lı́neas SDA y SCL del bus I2C obteniendo el resultado mostrado en la figura 2. Se pide: 1) Identificar los bits de la transferencia de datos, agrupándolos en los campos de los que forman parte. Especificar a su vez el nodo que estableció el valor lógico de cada uno de esos bits. 1 2) 3) 4) Explicar el significado y la función de cada campo y de cada bit. ¿Qué tipo de operación se está llevando a cabo?. Dar el máximo número de detalles. Completar la transferencia de datos con los bits que no aparecen en la figura. Figura 2: Monitorización de las señales que circulan a través de las lı́neas SDA y SCL de un bus I2C c) Un nuevo microcontrolador ha sido conectado al bus I2C en cuestión. En un momento dado, los dos microcontroladores inician una transferencia de datos de forma prácticamente simultánea: el microcontrolador 1 se adelanta 2 ns con respecto a su competidor. Conociendo las caracterı́sticas de las señales de reloj generadas por ambos dispositivos (ver figura 3), explicar detalladamente cómo se lleva a cabo el proceso de sincronización de dichas señales. ¿Cuál es la duración del ciclo alto y bajo de la señal de reloj resultante?. Figura 3: Caracterı́sticas de las señales de reloj generadas por dos microcontroladores 2 Escuela Politécnica Superior Universitat de les Illes Balears Ingenierı́a Técnica Industrial 16 de Junio de 2003 EXAMEN FINAL DE INFORMÁTICA INDUSTRIAL Segundo Parcial tiempo asignado: 2h 30’ (3,5P) P3. Considerar la jerarquı́a de memoria de dos niveles mostrada en la figura 4. Por un lado, ésta consta de una memoria cache asociativa por conjuntos de 4 vı́as (K = 4) con bloques de 8 palabras, polı́tica de sustitución LRU (Least Recently Used ), polı́tica de escritura directa (write through) y una capacidad de 1Kb. Por otro lado, tenemos una memoria principal de 32 bits entrelazada con una capacidad útil de 8Mb. Notar que el factor de entrelazado de dicha memoria es de 2 y que todos los bancos hacen uso de módulos de memoria SIMM (Single In-line Memory Module) de 30 contactos. Se pide: a) De forma genérica, justificar el uso de las jerarquı́as de memoria frente a componentes individuales. b) Esquematizar la estructura/organización de la memoria cache. En realidad, ¿cuál es su función de correspondencia?. c) Calcular el tiempo medio de acceso a memoria sabiendo que la tasa de aciertos (Hit rate) de la cache es del 85 % con un tiempo de acierto de 1 ciclo de reloj y que su penalización de fallos en un sistema con una organización de memoria principal ancha de 4 palabras es de 20 ciclos de reloj. Suponer en este caso que tanto el envı́o de una dirección como el de esas 4 palabras de datos a través del bus requieren 1 ciclo de reloj. d ) Los módulos de memoria (SIMMs) han sido diseñados utilizando chips DRAM de tamaño 8K × 4 bits. La verificación de la integridad de los datos sobre cada uno de ellos se lleva a cabo mediante un código SEC, detector y corrector de errores simples, basado en la codificación propuesta por Richard Hamming. Recordad que la relación entre el tamaño M del dato almacenado en el SIMM y la longitud K del código viene dada por la expresión 2k − 1 ≥ M + K. De este modo, ¿cuál es la capacidad real de la memoria principal?. Detallar la estructura/organización de los chips DRAM, de los módulos y los bancos de memoria ası́ como de toda la memoria principal respetando el presente orden. Hacer hincapié en la estructura lógica de la dirección de memoria, es decir, en la forma en la que el controlador de memoria deberı́a interpretar una dirección. e) La ejecución de un determinado programa genera la siguiente secuencia de accesos a memoria tanto en lectura (R) como en escritura (W): 00000H (W), 0000AH (R), 00006H (R), 0001BH (R), 00005H (W), 00029H (W), 0002EH (R), 00042H (W), 00049H (R), 0002AH (W), 00033H (R), 00002H (W), 0003BH (R), 0000DH (R), 00035H (W), 0002EH (W) Teniendo en cuenta que la polı́tica de fallo en escritura de la cache es No Ubicar en Escritura indicar qué accesos son aciertos y cuáles son fallos, ası́ como el tipo de fallo, junto con el contenido parcial y final de la cache. Notar a su vez que la implementación del algoritmo de sustitución LRU debe basarse en la técnica matricial descrita en clase de problemas y que cada actualización en memoria principal debe quedar perfectamente definida. Figura 4: Jerarquı́a de memoria de dos niveles con memoria entrelazada 3 Examen Final de Junio Informática Industrial (1,5P) P4. Responder a las siguientes cuestiones teóricas: a) Existen diferentes técnicas para llevar a cabo operaciones de E/S. Explicar cada una de las alternativas junto con sus ventajas e inconvenientes. b) Definir los conceptos de Watchdog, RTC, coprocesador y PWM. ¿Cuáles son sus principales funcionalidades?. c) Explicar la metodologı́a de diseño de sistemas vista en clase. 4