C13

Anuncio

1

Capítulo 13

Bloques básicos secuenciales.

13.1. Contadores.

Es una de las componentes más utilizada en el diseño de máquinas digitales.

En los diagramas de estados de contadores, no suelen anotarse las entradas, el cambio de estado

se produce con el canto del reloj; es decir, se cuentan los cantos del reloj.

La asignación de estados se elige de tal manera que el estado refleje la cuenta; debido a esto son

máquinas de Moore.

Los diseños pueden efectuarse con JK, y también con D. Las ecuaciones con flip-flops de tipo D

pueden implementarse directamente con lógica programable.

Pueden clasificarse según la forma de contar en contadores binarios, bcd, o en contadores con

secuencias especiales. También pueden ser progresivos o regresivos, si cuentan en forma

ascendente o descendente respectivamente.

Según el tipo de implementación pueden clasificarse en sincrónicos o asincrónicos. En los

primeros, el estado de todos los flip-flops cambia con el reloj; en los segundos todos los flipsflops no cambian simultáneamente con el reloj. Las señales de clear y reset también pueden ser

sincrónicas con el reloj o asincrónicas.

Se verán a continuación algunos contadores sincrónicos binarios ascendentes módulo potencia

de dos.

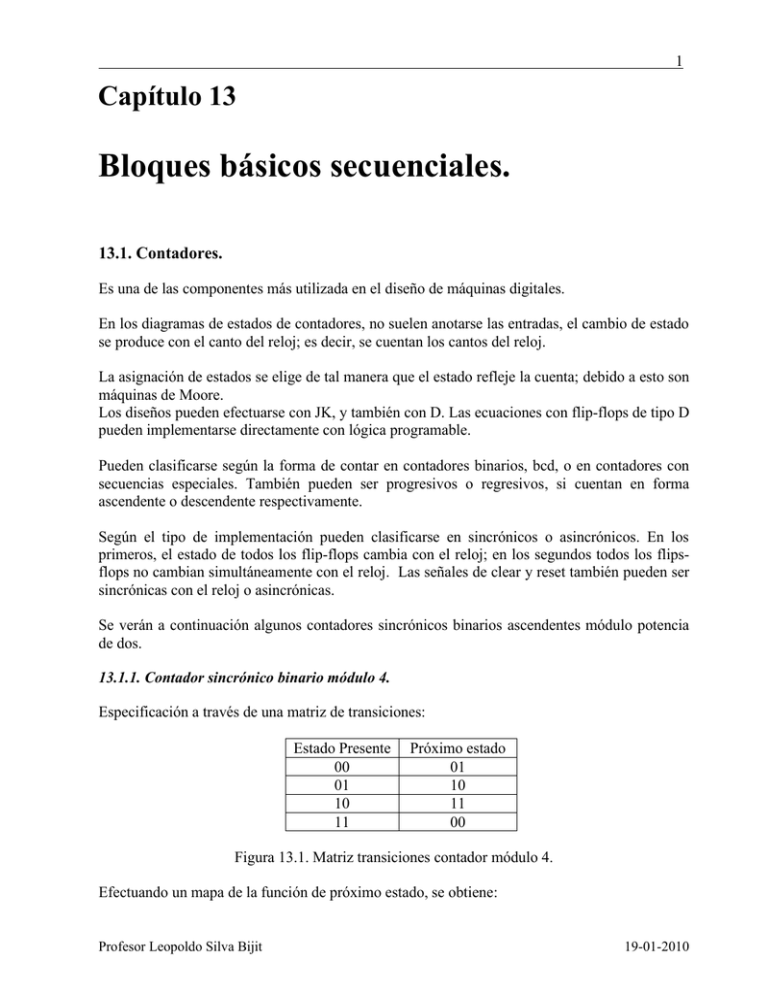

13.1.1. Contador sincrónico binario módulo 4.

Especificación a través de una matriz de transiciones:

Estado Presente

00

01

10

11

Próximo estado

01

10

11

00

Figura 13.1. Matriz transiciones contador módulo 4.

Efectuando un mapa de la función de próximo estado, se obtiene:

Profesor Leopoldo Silva Bijit

19-01-2010

2

Sistemas Digitales

Q1

0

Q0

0

01

1

10

1

0

11

2

1

3

00

Q1+ Q0+

Figura 13.2. Matriz de transiciones contador módulo 4.

Si la cifra menos significativa es Q0 y la más significativa es Q1, se tienen:

Q1+ = Q0Q1' + Q0'Q1 = J1Q1' +K1'Q1 = D1

Q0+ = Q0'

= J0Q0' +K0'Q0 = D0

Las que implican, para flip-flops JKs:

J1 = Q0

K1 = Q0

J0 = 1

K0 = 1

Las ecuaciones anteriores representan al siguiente circuito:

+Vcc

reset’

rst

J Q0

rst

J Q1

K

K

clk

clk

clk

Figura 13.2.a. Esquemático contador módulo 4.

Y para flip-flops Ds, se obtienen:

D1 = Q0Q1' + Q0'Q1

D0 = Q0'

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

3

13.1.2. Contador sincrónico binario módulo 8.

Puede especificarse mediante la siguiente matriz de transiciones:

Estado Presente

000

001

010

011

100

101

110

111

Próximo estado

001

010

011

100

101

110

111

000

Figura 13.3. Matriz de transiciones contador módulo 8.

Si la cifra menos significativa es Q0 y la más significativa es Q2, se tienen:

reset

000

Q2Q1

00

Q0

01

0

0

001

1

010

1

011

100

11

2

3

111

10

6

111

7

000

Q2+ Q1+ Q0+

101

110

001

4

5

010

110

101

011

100

Figura 13.4. Matriz de transiciones y diagrama de estados para contador módulo 8.

Notar que en el diagrama de estados, no hay señal de entrada asociada a las transiciones. El

cambio de estado se produce con el canto del reloj. La salida es el estado, y el diagrama

corresponde a un modelo de Moore.

Resultan:

Q2+ = Q1Q0Q2' + Q2(Q1' + Q0') = J2Q2' +K2'Q2 = D2

Q1+ = Q0Q1' + Q0'Q1

= J1Q1' +K1'Q1 = D1

Q0+ = 1Q0' + 0 Q0

= J0Q0' +K0'Q0 = D0

Profesor Leopoldo Silva Bijit

19-01-2010

4

Sistemas Digitales

En el caso de emplear flip-flops de tipo D, los programas resultan por simple lectura del mapa

de la matriz de transiciones, ya que: Di = Qi+

Para diseño con JKs, conviene leer los mapas buscando los factores de Qi y Qi'. Y luego

comparar los coeficientes de las ecuaciones características para encontrar los Ji y Ki'.

Se logran:

J2 = Q1Q0

J1 = Q0

J0 = 1

K2 = Q1Q0

K1 = Q0

K0 = 1

Usando flip-flops JKs, el diseño puede representarse por el esquemático de la Figura 13.5:

+Vcc

reset’

rst

J Q0

rst

J Q1

rst

J Q2

K

K

K

clk

clk

clk

clk

Figura 13.5. Esquemático contador módulo 8 mediante JK.

Notar que los flip-flops operan con el canto de bajada del reloj.

Se destaca un reset asincrónico: cuando la señal reset' (de lógica negativa) tiene un canto de

bajada, se activa. Entonces, en ese momento, todos los flip-flops van a cero (ver marcador 1 en

la Figura 13.6), y se tiene al contador en el estado inicial. Permanece en ese estado hasta que se

desactiva la señal reset'; es decir cuando reset' = 1, luego de lo cual, en el próximo canto de

bajada del reloj, se pasará al próximo estado 001. El pequeño círculo que está en la entrada de

reset, indica que es una señal de lógica negativa; y es convencional describirla con el nombre

negado: reset'.

Las formas de ondas muestran el tiempo de propagación de los flip-flops (ver marcador tf en la

Figura 13.6); es decir el tiempo que transcurre desde el canto hasta que se tiene nivel estable en

las salidas Q de los flip-flops.

Nótese que todas las salidas cambian en el mismo momento, y que permanecen estables entre

cantos de bajada del reloj.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

5

rst'

clk

Q2

Q1

Q0

1

tf

Figura 13.6. Formas de ondas contador módulo 8.

13.1.3. Contador sincrónico binario módulo 16.

Si la cifra menos significativa es Q0 y la más significativa es Q3, se tienen:

Q3Q2

Q1Q0

00

01

0

00 0001

1

01 0010

11 0100

10 0011

3

2

11

4

0101

0110

1000

0111

10

12

1101

5

7

13

1110

15

0000

6

14

1111

8

1001

1010

9

11

1100

10

1011

Q3+ Q2+ Q1+ Q0+

Figura 13.7. Matriz de transiciones contador módulo 16.

Resultan:

Q3+ = Q1Q0Q2Q3' + (Q2'+ Q1' + Q0') Q3 = J3Q3' +K3'Q3 = D3

Q2+ = Q1Q0Q2' + Q2(Q1' + Q0')

= J2Q2' +K2'Q2 = D2

Q1+ = Q0Q1' + Q0'Q1

= J1Q1' +K1'Q1 = D1

Q0+ = Q0'

= J0Q0' +K0'Q0 = D0

Las que implican los programas de los flip-flops JK:

J3 = Q2Q1Q0

K3 = Q2Q1Q0

J2 = Q1Q0

K2 = Q1Q0

J1 = Q0

K1 = Q0

J0 = 1

K0 = 1

Profesor Leopoldo Silva Bijit

19-01-2010

6

Sistemas Digitales

El esquema siguiente ilustra el diseño sincrónico. Debe notarse que aumentan las cargas de Q0 y

que se requiere una compuerta de mayor fan-in en la entrada del flip-flop más significativo.

Con tf, el tiempo de propagación desde el flanco del reloj hasta la salida; tc tiempo de

propagación a través de la compuerta; tsu tiempo de set-up del flip-flop, el período mínimo del

reloj queda dado por: (tf + tc + tsu + tskew), el cual es determinado por los flip-flops Q2 y Q3;

los requerimientos de período del reloj de los flip-flops Q0 y Q1 son menos exigentes.

El requerimiento de hold, de los flip-flops Q0 y Q1, se satisface si el tiempo de propagación,

desde el canto del reloj hasta la salida, es mayor que el tiempo de sostenimiento requerido; los

flip-flops Q2 y Q3 tienen exigencias menores de sostenimiento, ya que existe un tiempo de

propagación de una compuerta. Recuérdese que los requerimientos de hold se evalúan en un

mismo canto del reloj; y los de setp-up, entre dos cantos adyacentes.

+Vcc

reset’

rst

J Q0

rst

J Q1

rst

J Q2

rst

J Q3

K

K

K

K

clk

clk

clk

clk

clk

Figura 13.8. Esquemático contador módulo 8 mediante JK.

Las formas de ondas de Q0, Q1, Q2, Q3, clk y rst se ilustran a continuación:

Q0

Q1

Q2

Q3

clk

rst

Figura 13.9. Formas de ondas contador módulo 16.

Si los períodos del reloj, de Q0, Q1, Q2 y Q3 son: Tc, T0, T1, T2 y T3 respectivamente, se

tienen:

Tc

Profesor Leopoldo Silva Bijit

T0

2

T1

4

T2

8

T3

16

19-01-2010

Capítulo 13. Bloques básicos secuenciales

7

Puede variarse el diseño, liberando tener un flip-flop (el menos significativo) con mayor fanout, y una compuerta de mayor fan-in en la entrada del flip-flop más significativo, del modo

siguiente:

+Vcc

reset’

rst

J Q0

rst

J Q1

rst

J Q2

rst

J Q3

K

K

K

K

clk

clk

clk

clk

clk

Figura 13.10. Disminución fan-out.

Este diseño, sigue siendo sincrónico, pero aumenta el período mínimo que puede tener el reloj

para el funcionamiento correcto de Q3. Ahora se tiene que el período mínimo queda dado por:

(tf +2 tc + tsu+ tskew), el cual implica una frecuencia máxima menor que la del diseño anterior.

13.1.4. Contador binario de ripple, con salida asincrónica.

El siguiente diseño, basado en la experiencia e intuición, es el contador que requiere menos

hardware.

Los flip-flops JK están conectados simulando un flip-flop T, y se emplea la capacidad de este

flip-flop de dividir por dos la frecuencia del reloj. Se muestra un esquema a continuación:

+Vcc

+Vcc

+Vcc

+Vcc

reset’

rst

J Q0

rst

J Q1

rst

J Q2

rst

J Q3

K

clk

K

clk

K

clk

K

clk

clk

Figura 13.11 Contador ondulado o de ripple.

Debido a que las entradas no cambian, se cumplen automáticamente los requerimientos de

sostenimiento y set-up, para los cuatro flip-flops. La propagación de la transición de la cuenta

15 a la cuenta cero, limita el período mínimo del reloj. Ya que en este caso, como se ilustra en la

Figura 13.12 se tiene el menor valor de tiempo en el cual en contador está en una cuenta dada.

Profesor Leopoldo Silva Bijit

19-01-2010

8

Sistemas Digitales

Entonces se tiene para el mínimo período: (4tf +t0min), lo cual implica que la duración del tiempo

en cuenta cero será igual a t0min.

A continuación se muestran las formas de ondas. Los tiempos en que este contador permanece

en cada estado no son regulares.

clk

Q0

Q1

Q2

Q3

rst'

Figura 13.12. Formas de ondas contador ripple.

13.1.5. Contador de anillo (ring counter).

El siguiente esquema ilustra un registro de desplazamiento a la derecha, máquina secuencial que

se verá más adelante, que se emplea como contador.

reset’

set

J Q0

rst

J Q1

rst

J Q2

rst

J Q3

K

clk

K

clk

K

clk

K

clk

clk

Figura 13.13. Contador de anillo.

Debe notarse que el primer flip-flop requiere un set asincrónico para iniciar el funcionamiento

del contador. Además, como puede observarse en las formas de ondas, los estados por los que

pasa el contador están restringidos a una secuencia determinada. Pasa para la configuración de

la Figura 13.13, por: 0001, 0010, 0100, 1000.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

9

Q0

Q1

Q2

Q3

clk

rst

Figura 13.14. Formas de ondas contador de anillo.

Una variación, que permite duplicar los estados del "ring counter", es el contador de Johnson.

13.1.6. Contador de Johnson.

Debe notarse que Q3 se conecta a K0, y que Q3' se conecta a J0. Este contador pasa por ocho

estados:

0000, 0001, 0011, 0111, 1111, 1110, 1100, 1000.

El contador de anillo y el de Johnson tienen salidas sincrónicas. El contador de Johnson tiene

señal de reset común, y no requiere del inicio especial del contador de anillo. Para ambos se

tiene que el período mínimo queda dado por (tf + tsu). Logrando mayores frecuencias de

operación que los contadores anteriores.

reset’

rst

J Q0

rst

J Q1

rst

J Q2

rst

J Q3

K

clk

K

clk

K

clk

K

clk

clk

Figura 13.15. Contador de Johnson.

Con las siguientes formas de ondas:

Profesor Leopoldo Silva Bijit

19-01-2010

10

Sistemas Digitales

Q0

Q1

Q2

Q3

clk

rst

Figura 13.16. Formas de ondas contador Johnson.

13.1.7. Contador integrado 74163.

En la familia TTL existen diversos tipos de contadores. Uno muy versátil es el 74163, que tiene

señales de carga y clear sincrónicas. Lo cual permite cargar un valor de cuenta inicial y también

dejar en cero en forma sincrónica con el reloj. También se dispone de una señal que está alta

cuando se está en el estado más alto; es decir cuando el contador pasa al estado 1111, la señal se

denomina RCO (ripple carry output).

Los controles anteriores permiten diseñar contadores especiales. Por ejemplo uno que cuente

desde un valor inicial hasta 1111 (se logra conectando rco a la señal load).

Similar esquema suele emplearse en los temporizadores de procesadores y microcontroladores,

donde además de los recursos habituales de aritmética y lógica se agrega un contador, con

controles sincrónicos, denominado usualmente “timer”.

Otro contador, que puede implementarse con estos controles, es uno que cuente desde 0000

hasta un valor dado; para ello se requiere decodificar el estado y con esto alimentar la señal

clear.

No es recomendable emplear las entradas asincrónicas de los contadores para diseños como los

descritos antes; en este caso debe restringirse el uso de los controles asincrónicos sólo para

establecer el estado inicial.

Un diagrama lógico del contador 74163 se muestra en la Figura 13.17.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

11

load’

clear’

P0

P1

P2

P3

PE

TE

74163

Q0

Q1

Q2

Q3

RCO

clk

Figura 13.17. Esquemático contador 74163.

Los controles clear’ y load’ se definen de lógica negativa, esto implica que la limpieza a cero

del estado del contador se logra con el canto de bajada de clear’. Como este control es

sincrónico, el instante preciso, en que se produce la acción, es el canto de subida del reloj luego

de que clear tiene un canto de subida. La Figura 13.17a, muestra la especificación del contador

mediante una tabla de verdad.

clear’

1

1

1

1

0

load’

0

1

1

1

x

PE

x

0

x

1

x

TE

x

x

0

1

x

Operación

preset

No cuenta

No cuenta

cuenta

reset

Figura 13.17a. Especificación contador 74163.

La siguiente descripción Verilog, ilustra el funcionamiento del contador.

module C74163(loadn, clearn, PE, TE, clk, P, RCO, Q)

input loadn, clearn, PE, TE, clk;

input [3:0] P;

output [3:0] Q;

output RCO;

reg [3:0] Q;

assign RCO = (&Q) & TE;

always @ (posedge clk)

begin

if (clearn == 0) Q <= 0;

else if (loadn ==0) Q <= P;

else if (PE & TE ) Q <= Q+1;

end

endmodule

Profesor Leopoldo Silva Bijit

19-01-2010

12

Sistemas Digitales

La expresión &Q es equivalente al AND de cada uno de los bits de Q.

13.1.8. Contador sincrónico binario módulo 32.

De los diseños de los contadores binarios módulos 4, 8 y 16, pueden inducirse las siguientes

ecuaciones, sin efectuar desarrollos. Lo mismo puede decirse para contadores módulo una

potencia de dos: 64, 128, etc.

Las ecuaciones de diseño basadas en flip-flops JKs:

J4 = Q3Q2Q1Q0

K3 = Q3Q2Q1Q0

J3 = Q2Q1Q0

K3 = Q2Q1Q0

J2 = Q1Q0

K2 = Q1Q0

J1 = Q0

K1 = Q0

J0 = 1

K0 = 1

Para diseños basados en flip-flops Ds:

Q4+ = Q1Q0Q2Q3Q4' + Q4(Q3' + Q2'+ Q1' + Q0')

Q3+ = Q1Q0Q2Q3' + Q3(Q2'+ Q1' + Q0')

Q2+ = Q1Q0Q2' + Q2(Q1' + Q0')

Q1+ = Q0Q1' + Q0'Q1

Q0+ = Q0'

=

=

=

=

=

D4

D3

D2

D1

D0

A continuación se ilustran algunos ejemplos de contadores binarios sincrónicos que no son

módulo una potencia de dos.

13.1.9. Contador sincrónico módulo 7.

Si la cifra menos significativa es Q0 y la más significativa es Q2, se tienen:

000

Q2Q1

00

Q0

0

1

001

010

01

0

1

011

100

11

2

3

000

10

6

7

101

110

Q2+ Q1+ Q0+

001

4

5

111

110

101

010

011

100

Figura 13.18. Contador sincrónico módulo 7.

El estado 111 (7) se trata como superfluo.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

Resultan:

Q2+ = Q1Q0Q2'+Q1'Q2

Q1+ = Q0Q1' + Q2'Q0'Q1

Q0+ = (Q2'+Q1')Q0'

Las que implican:

J2 = Q1Q0

J1 = Q0

J0 = Q2'+Q1'

13

= J2Q2' +K2'Q2 = D2

= J1Q1' +K1'Q1 = D1

= J0Q0' +K0'Q0 = D0

K2 = Q1

K1 = Q2 + Q0

K0 = 1

13.1.10. Contador sincrónico módulo 6.

Si la cifra menos significativa es Q0 y la más significativa es Q2, se tienen:

000

Q2Q1

00

Q0

0

001

01

0

11

2

011

10

6

101

001

4

111

110

1

1

010

100

3

7

000

010

5

101

011

100

Q2+ Q1+ Q0+

Figura 13.19. Contador sincrónico módulo 6.

Resultan:

Q2+ = Q1Q0Q2'+Q0'Q2

Q1+ = Q2'Q0Q1' + Q0'Q1

Q0+ = Q0' + 0 Q0

Las que implican:

J2 = Q1Q0

J1 = Q2'Q0

J0 = 1

= J2Q2' +K2'Q2 = D2

= J1Q1' +K1'Q1 = D1

= J0Q0' +K0'Q0 = D0

K2 = Q0

K1 = Q0

K0 = 1

En la familia TTL existen contadores asincrónicos como el 7493 que pueden contar en módulo

8 ó 16. Y el 7490 que puede contar en módulo 5 o por décadas (Módulo 10).

13.2. Registros de desplazamiento.

Se denomina registro a una serie de flip-flops agrupados, con reloj y señales de control común.

En los de desplazamiento se transfiere información de una celda (o flip-flop) hacia la adyacente,

dentro del mismo registro. Esta operación se llama corrimiento (shift). El corrimiento puede ser

Profesor Leopoldo Silva Bijit

19-01-2010

14

Sistemas Digitales

a la izquierda o a la derecha. Si el contenido representa a un número con signo, los corrimientos

aritméticos pueden ser realizados con extensión de signo.

Debe considerarse en forma especial los bordes. Indicando con qué se llena el hueco que se

produce; y especificando que se hace con el bit que sale del registro.

13.2.1 Usos.

Algunos de sus principales usos son:

a) Operaciones aritméticas. Permite multiplicar y dividir por dos el contenido de un registro

interpretado como número binario. Esta operación puede producir rebalse y también

truncamiento. Esto en caso que el resultado del producto no pueda representarse en el

registro; o en caso de una división de un número impar, respectivamente.

b) Operaciones lógicas. Permite posicionar un bit cualquiera en otra posición del registro. Esto

favorece las operaciones orientadas al bit. Una variante de esta operación es la rotación, en

la cual lo que sale del registro se introduce en el lugar vacante.

c) Conversión serie a paralelo. Permite pasar una información binaria en serie a paralelo y

vice-versa.

d) Generador de secuencias. Si se conecta como registro de rotación, puede generarse una

secuencia de largo n, donde n es el número de celdas.

e) Línea de retardo. Un valor en la entrada, sale n pulsos más tarde en la salida.

f) Reconocedor de secuencias. Si se conecta en las salidas de los flip-flops un decodificador

puede reconocerse una secuencia cada vez que se presente en la entrada.

g) Generador de códigos de chequeo. Se emplean para agregar información de chequeo a

paquetes con información, de tal modo de transmitir la información con datos de control,

que permitan verificar la correcta recepción del paquete.

h) Generador de secuencias binarias pseudoaleatorias (PRBS). Se emplean como generadores

de ruido. También se emplean para generar encriptación, en una configuración denominada

LFSR (Linear feedback shift register).

13.2.2. Ejemplo de diseño.

Se desea efectuar un corrimiento a la derecha. Es decir, con el canto del reloj, el contenido del

flip-flop Q0 pasa a Q1. Alternativamente, lo que se desea es que el próximo estado de Q1 sea el

valor actual de Q0.

x

clk

J0

Q0

K0

Q0'

J1

Q1

K1

Q1'

Figura 13.20. Transferencia entre dos flip-flops.

Entonces, se desea que:

Q1+ = Q0 = D1

Expandiendo en Q1 se logra:

Q1+ = Q0Q1' +Q0Q1

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

15

Comparando con la ecuación característica, se obtiene:

Q1+ = J1Q1' +K1'Q1

Se logran: J1 = Q0; K1 = Q0'

Si se desea ingresar x a Q0, se debe cumplir: Q0+ = x = D0

En este caso se tendrá: Q0+ = xQ0' +xQ0 = J0Q0' +K0' Q0

Se logran: J0 = x; K0 = x'

13.2.3. Registro de desplazamiento a la derecha de largo 4.

A continuación se ilustra un registro de largo 4, en base a JK:

reset’

x

rst

J Q0

rst

J Q1

rst

J Q2

rst

J Q3

K

K

K

K

clk

clk

clk

clk

clk

Figura 13.21. Registro de desplazamiento a la derecha de largo 4.

Se muestran las formas de ondas cuando se aplica, en la entrada, la secuencia x = 01101110.

Debe notarse, en la gráfica, cómo el valor de x pasa a Q0, el valor de Q0 pasa a Q1, el de Q1 a

Q2, etc.

x

rst

clk

Q3

Q2

Q1

Q0

Figura 13.22. Formas de ondas en registro de desplazamiento.

13.2.4. Registros de desplazamiento TTL

La componente 7491 es un 8-bit shift register, serial-in serial out gated input.

Profesor Leopoldo Silva Bijit

19-01-2010

16

Sistemas Digitales

El 7494 es un shift register de 4 bits. Entrada paralela y salida serial. Además tiene entrada

serie. EL 7495, es de 4 bits, tiene entrada serial, carga de entrada en paralelo, salida paralela,

además de controles para corrimiento a la izquierda y a la derecha.

Las componentes 74164, 74165, 74166 son registros de 8 bits.

74194, 74195 y 74198 se denominan universales (de 4 y 8 bits) y tienen carga paralela y

corrimiento en ambas direcciones. Algunos de ellos están disponibles en los simuladores.

13.2.5. Registro universal 74194A.

Para el 74194A de Texas Instruments se entrega la siguiente tabla de funcionamiento:

Funciones 74LS194.

CLR S1 S0 CLK SL

L

X X

X X

H

X X

L X

H

H H

↑ X

H

L H

↑ X

H

L H

↑ X

H

H L

↑ H

H

H L

↑ L

H

L L

↑ X

SR

X

X

X

H

L

X

X

X

A

X

X

a

X

X

X

X

X

B

X

X

b

X

X

X

X

X

C

X

X

c

X

X

X

X

X

D

X

X

d

X

X

X

X

X

QA

L

Qa

a

H

L

Qb

Qb

Qa

QB

L

Qb

b

Qa

Qa

Qc

Qc

Qb

QC

L

Qc

c

Qb

Qb

Qd

Qd

Qc

QD

L

Qd

d

Qc

Qc

H

L

Qd

Función

Clear

Hold

Load

Shift R

Shift R

Shift L

Shift L

Hold

Con: SR shift right serial input; SL shift left serial input; A, B, C, D entrada paralela; QA,

QB, QC, QD salida paralela. S0 y S1 entradas de control. La señal CLR es un control

asincrónico, que coloca en cero los flip-flops. El evento que sincroniza las transferencias es el

canto de subida de la señal CLK.

De las especificaciones se logra la siguiente descripción funcional.

S0=1 y S1= 1 generan la señal de carga paralela. ( QA+=A, QB+=B, QC+=C, QD+=D )

S0=0 y S1 =1 corrimiento izquierdo ( QA+ = QB, QB+ = QC, QC+ = QD, QD+ = SL )

S0=1 y S1 =0 corrimiento derecho ( QA+ = SR, QB+ = QA, QC+ = QB, QD+ = QC )

S0=0 y S1 =0 se inhibe el reloj, el registro mantiene su estado (hold).

La siguiente descripción Verilog, modifica la especificación anterior, dejando el control CLR

como sincrónico.

module UniversalShiftRegister(CLR, CLK, SL, SR, S, datos, Q);

input CLR, CLK;

input SL, SR;

input [1:0] S;

input [3:0] datos;

output [3:0] Q;

reg [3:0] Q;

always @(posedge CLK)

if (CLR==0) Q<=0;

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

17

else

begin

if (S==2’b11) Q <= datos;

else if (S==2’b10) Q <= { REG[2:0] , SL};

else if (S==2’b01) Q <= { SR, REG[3:1] };

end

endmodule

El esquemático siguiente es la implementación de Texas Instruments para el 74LS194A.

Figura 13.23. Registro universal Texas.

A partir del esquemático de la Figura 13.23, se obtienen las siguientes ecuaciones, asumiendo

flip-flops Ds, en lugar de SRs. Debe notarse que el estado hold se logra pasando por una

compuerta el reloj externo. Las ecuaciones siguientes permiten una descripción a nivel de

compuertas y flip-flops.

DA = (SR S1' +(S0' +S1')' A + QB S0' )

DB = (QA S1' +(S0' +S1')' B + QC S0' )

DC = (QB S1' +(S0' +S1')' C + QD S0' )

DD = (QC S1' +(S0' +S1')' D + SL S0' )

clk = (clk externo + S1’ S0’)’

Philips en su diseño no modifica el reloj, agregando una decodificación adicional, para

cada flip-flop.

Profesor Leopoldo Silva Bijit

19-01-2010

18

Sistemas Digitales

Figura 13.23a. Registro universal Philips.

13.3. Registros.

Se denomina registro a una colección de flip-flops con lógica y controles similares. Suelen

compartir el reloj, y las líneas asincrónicas de set y clear.

13.3.1. Registro de almacenamiento.

El siguiente esquema, es un registro de almacenamiento, que muestrea 4 bits disponibles en las

líneas de entrada, los captura en un canto del reloj y los mantiene en las salidas hasta el próximo

canto del reloj.

In0

In1

In2

In3

reset’

rst

rst

rst

rst

D Q0

D Q1

D Q2

D Q3

clk

clk

clk

clk

clk

Out0

Out1

Out2

Out3

Figura 13.24. Registro de almacenamiento.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

19

Una variante del registro anterior, es un registro con habilitación de escritura. Se agrega una

señal adicional WE (write enable), cuya activación permite la escritura en el registro.

13.3.2. Registro de desplazamiento.

El siguiente esquema es un registro de desplazamiento a la derecha, implementado con flipflops Ds. Almacena los últimos 4 bits de la secuencia de entrada.

reset’

In

rst

rst

rst

rst

D Q0

D Q1

D Q2

D Q3

clk

clk

clk

clk

clk

Out0

Out1

Out2

Out3

Figura 13.25. Registro de desplazamiento a la derecha de largo 4.

13.3.3. Diseño de máquinas en base a registros

Si se agrega un decodificador, que tenga como entradas a las salidas del registro de la Figura

13.25, puede generarse un detector de una secuencia de 4 bits, cada vez que ésta se presente.

13.4. Alternativas de Diseño de Máquinas Secuenciales.

13.4.1. Diseño basado en ROM.

Almacenar el estado en un registro, e implementar las funciones de próximo estado en una

ROM.

ROM

entradas

direcciones

registro

contenidos

clk

Figura 13.26 Diseño basado en EPROM.

Este esquema se emplea para diseñar unidades de control microprogramadas de procesadores.

La información del próximo estado se almacena en la ROM.

Profesor Leopoldo Silva Bijit

19-01-2010

20

Sistemas Digitales

13.4.2. Diseño basado en PLD.

Usar un dispositivo programable con salidas de registro; con esta arquitectura, las

realimentaciones del estado son internas.

PLD

entradas

salidas

clk

Figura 13.27. Diseño basado en PLD.

Este esquema se emplea para diseñar unidades de control en firmware, o de lógica alambrada.

13.4.3. Secuenciador.

Una variante del esquema basado en ROM, es emplear, para registrar el estado, un contador

sincrónico con funciones de carga paralela, clear e incrementar; y programar la función de

próximo estado en función de estas señales.

Este esquema se denomina de microsecuenciación y se emplea en diseños de la unidad de

control de procesadores.

Las funciones de las señales de control del contador son:

Cero:

Inc:

Load:

llevar al estado inicial.

pasar al estado siguiente.

presetear un estado determinado

Cero

0000

i

Inc

i

Load

i+1

Figura 13.28. Operaciones del contador.

Ejemplo 13.1.

Diseñar con un secuenciador el siguiente diagrama de estados.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

21

0000

inc

0001

load

load

x= 0

0100

load

0110

x=1

load

x= 2x= 3

1000

inc

inc

inc

1001

load

load

1011

x= 5

x= 4

0011

0010

inc

1100

inc

0101

0111

1010

Cero

Cero

Cero

Cero

Cero

Cero

Figura 13.29. Diagrama de estados mediante secuenciador.

El contador registra el estado, y sus salidas están conectadas a las direcciones de la memoria. El

contenido de la memoria son los bits: C, I, L que están conectadas a las señales Cero,

Incrementar y Cargar del registro; además pueden grabarse en la memoria, los diversos bits de

salida que se requieran asociados a cada estado (esquema de Moore).

A continuación se presenta la tabla de transiciones, o programa del secuenciador, notando que la

información del próximo estado no se almacena en la memoria, se incorpora en la tabla sólo con

fines aclaratorios del funcionamiento:

Profesor Leopoldo Silva Bijit

19-01-2010

22

Sistemas Digitales

Estado

0000

0001

0010

0011

0100

0110

1000

1011

1001

1100

0101

0111

1010

Próximo

0001

0000

0000

0101

0111

1001

1100

1010

0000

0000

0000

0000

C

0

0

1

1

0

0

0

0

0

1

1

1

1

I

1

0

0

0

1

1

1

1

1

0

0

0

0

L

0

1

0

0

0

0

0

0

0

0

0

0

0

Salidas

Figura 13.30. Programa del secuenciador.

Nótese que los nombres binarios de los estados se eligen para ocupar lo más eficientemente que

sea posible la señal de cuenta o incremento del contador.

Al estado 0000, se llega después del reset inicial. Si la naturaleza del proceso secuencial es

repetitiva, al terminar los diferentes recorridos de estados se retorna al estado inicial. Para esto

se emplea la señal Cero.

Estando en el estado 0001, de acuerdo a la entrada se discierne cuál es el próximo estado. En el

ejemplo existe sólo un estado para el cual existen múltiples bifurcaciones. Se requiere

almacenar la información de los próximos estados de acuerdo a los valores de las entradas, y

cuando se active la señal Load. Esta información se denomina Tabla de Despacho.

Entrada x

000

001

010

011

100

101

Próximo estado.

0100

0110

1000

1011

0011

0010

Figura 13.31. Tabla de despacho.

Esta información puede codificarse en una ROM pequeña, o implementarse mediante un PLD.

Debe notarse que en la ROM del secuenciador no se almacena el próximo estado. Esto puede

significar un ahorro importante de memoria, si existe un pequeño número de estados con

múltiples bifurcaciones.

En caso de existir varios nodos con bifurcaciones, es preciso definir otras señales de carga, una

por cada nodo con bifurcaciones, y también igual número de tablas de Despacho. La señal Load

del contador es activada por el or de las señales de carga de las tablas de despacho.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

23

Un esquema general de la arquitectura para diseño de máquinas secuenciales en base a un

secuenciador, se ilustra a continuación.

ROM

Próximo Estado

Contador

Tabla de

Despacho

Direcciones

Carga

Paralela

L

Entradas

C

Contenidos

I C L Salidas

Inc

Figura 13.32. Arquitectura para diseño mediante secuenciador.

13.5. Diseño de controladores.

Un uso frecuente de las máquinas secuenciales sincrónicas es ejercer control sobre dispositivos

asincrónicos con los que se desea intercambiar datos. Un ejemplo de esta situación es la

conexión de un sistema sincrónico con memorias o periféricos.

Especificación del dispositivo.

Para ilustrar consideraremos un dispositivo que genera datos. En la Figura 13.33, se muestra un

diagrama de bloques, indicando las señales de entrada y de salida.

comando

habilita

datos

ocupado

Figura 13.33. Dispositivo a ser controlado.

Se envía un pulso de comando que inicia la actividad del periférico, luego de un tiempo el

dispositivo indica que está procesando el requerimiento con la señal ocupado; cuando los

nuevos datos generados por el dispositivo están listos para ser usados, se habilita la salida,

permitiendo de este modo que los datos estén disponibles en el bus de salida. Cuando la salida

está deshabilitada el bus de datos está en un estado de alta impedancia, lo cual permite que

varios dispositivos compartan el bus de datos.

El primer paso del diseño consiste en estudiar la hoja de datos del dispositivo, analizando los

requerimientos temporales. En la Figura 13.34 se muestran las formas de ondas con sus

especificaciones de tiempo.

Profesor Leopoldo Silva Bijit

19-01-2010

24

Sistemas Digitales

Asumiremos algunos valores de los parámetros para ilustrar el ejemplo.

El ancho del pulso del comando que da inicio a la actividad del dispositivo tiene que tener un

ancho mínimo dado por ta = 300 ns.

Luego del canto de bajada del pulso de comando, transcurre un tiempo de retardo hasta que el

dispositivo inicia su actividad, sea tr = 700 ns. Este tiempo es el máximo indicado por el

fabricante.

Posteriormente a tr, el dispositivo indica que comenzó a efectuar el procesamiento, y mantiene

alta la señal ocupado mientras dure el trabajo interno, sea este tiempo tp = 10 μs. Nótese que

este intervalo es mucho mayor que el indicado en el diagrama, lo cual se indica con una línea

quebrada en su parte superior.

Luego del canto de bajada de ocupado, debe habilitarse la salida, pero los datos estarán

disponibles luego de transcurrido el tiempo de acceso al bus, sea este tiempo tb = 250 ns. Luego

de esto se tienen nuevos datos válidos en el bus de salida, y se podría proceder a su captura. Una

vez almacenados los datos se deshabilita el bus, subiendo la señal habilita. El dispositivo aún

mantiene los datos en el bus un tiempo antes de entrar en flotación, sea este tiempo tf = 150 ns.

comando

ta

ocupado

tr

tp

habilita

tb

datos

tf

validos

Figura 13.34. Requerimientos temporales.

Por otro lado se dispone de un sistema sincrónico que opera con un reloj de 5 MHz, lo cual

implica un período de reloj de 200 ns.

Deseamos diseñar una máquina de estados finitos o controlador que:

a) Acepte órdenes sincrónicas para grabar los datos generados por el dispositivo periférico.

b) Genere las señales de control para el dispositivo, cumpliendo las especificaciones temporales.

c) Encueste la respuesta asincrónica.

d) Permita conocer cuando la operación está realizada.

Especificación del sistema sincrónico.

La Figura 13.35, muestra el entorno del controlador. El sistema sincrónico genera las señal de

reset, para colocar en un estado inicial al controlador; la señal lea para iniciar la lectura; y recibe

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

25

la señal capture, que se emplea para grabar los datos en el registro y como notificación de que la

operación se ha completado.

sistema

controlador

dispositivo

reset

lea

comando

capture

ocupado

habilita

datos

clk

Figura 13.35. Entorno de diseño.

Debe notarse que las señales que interactúan entre el controlador y el sistema si bien están

sincronizadas por el mismo reloj, lo hacen en cantos diferentes. Esta elección se realiza para

garantizar el cumplimiento de las reglas de sincronización de los flip-flops del controlador y del

sistema, tanto en el tiempo de setup como en el de mantenimiento (hold). Lo cual se ilustra en el

diagrama de la Figura 13.36.

A la izquierda se muestran las señales lea o reset como pulsos de un ancho del reloj de

duración, sus cambios ocurren en los cantos de bajada del reloj, de este modo los flip-flops del

controlador tomarán muestras de sus entradas en los cantos de subida del reloj, instante en que

ambas señales estarán estables. A la derecha se ilustra que el registro que almacena los datos

tendrá su habilitación estable en el canto de bajada del reloj, ya que la señal capture, que

proviene del controlador, cambia entre cantos de subida del reloj.

lea o reset

capture

clk

clk

Figura 13.36. Entorno de diseño.

El dispositivo puede tener internamente un funcionamiento sincrónico, pero se asume que su

reloj es diferente del reloj del sistema, por esto se dice que la señal ocupado es asincrónica

respecto del controlador. Razón por la cual deberá ser sincronizada, esto lo lograremos haciendo

pasar esta señal por dos flip-flops Ds, antes de ser ingresada al controlador.

Diseño del controlador.

Lo primero que enfrentaremos será generar la señal de control comando, cumpliendo el

requisito del ancho mínimo del pulso. Como el reloj tiene un período de 200 ns, podemos crear

un pulso que dure 400 ns, lo cual cumple la especificación. En la Figura 13.37, se muestra la

Profesor Leopoldo Silva Bijit

19-01-2010

26

Sistemas Digitales

señal lea, que ha llegado después de un pulso de reset. En el estado inicial E0, debemos iniciar

la señal comando en nivel alto. Estando en E0, permanece en ese estado mientras la señal lea

esté baja. Estando en E0, cuando la señal lea se encuentra en alto, la red combinacional de

próximo estado genera el nuevo estado E1, el que se actualiza en el próximo canto de subida del

reloj, situación que se ilustra en la Figura 13.37, con el marcador a.

a b

d

clk

lea

comando

E0 E1 E2 E3

Figura 13.37. Generación de señal de control comando.

Para lograr el requerimiento de ancho mínimo del pulso comando, debemos mantener baja esta

señal dos períodos del reloj, de este modo la señal tendrá un ancho de 400 ns, que es levemente

mayor al requisito de 350 ns como ancho mínimo. Lo anterior implica disponer de dos estados

E1 y E2, durante los cuales la señal comando esté en 0. La Figura 13.38, muestra la parte del

diagrama de estados que controla la generación de la señal comando, la cual se muestra con la

letra c, en el interior del estado del diagrama de Moore.

reset

lea=0

E0

c=1

lea=1

a

E1

c=0

ocupadoS=0

b

E2

c=0

E3

d

c=1

Figura 13.38. Diagrama de estados para la señal de control comando.

Los estados E1 y E2 se emplean para temporizar, por esta razón no se requieren cambios de las

entradas para el cambio de estado. Los instantes en que se producen los cambios al estado E2 y

E3, se muestran con los marcadores temporales b y d, en la Figura 13.37.

El estado E0 se usa para esperar el canto de subida de lea; el estado E3 se emplea para esperar el

canto de subida de ocupadoS, donde esta señal representa la sincronización de la señal ocupado,

generada por el dispositivo asincrónico que se desea controlar. La señal ocupadoS en el peor

caso tiene un retardo de dos períodos de reloj respecto de la señal ocupado, ya que para

sincronizarla se la pasa por dos flip-flops Ds.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

27

Para cumplir con los requerimientos de los flip-flops del controlador, la señal ocupadoS debe

ser sincronizada con los cantos de bajada del reloj.

La Figura 13.39 muestra la transición al estado E4, en el canto marcado con el identificador e.

Que corresponde al siguiente canto de subida en el que se ha sensado ocupadoS en alto.

e

f

g

clk

ocupadoS

habilita

capture

E3

E4

E5 E6

E0

Figura 13.39. Generación de habilita y capture.

Permanece en E4 hasta que llegue el canto de bajada de ocupadoS; luego en el canto de subida

del reloj, se pasa al estado E5, en el cual se genera el control habilita=0. Se decide generar la

señal capture en el estado siguiente E6, ya que como los datos se graban con el canto de bajada

del reloj, esto ocurrirá 300 ns luego del instante denominado f en el diagrama. Lo cual garantiza

que se tendrán datos válidos en el bus de tercer estado del dispositivo. Finalmente se requiere

deshabilitar la salida y terminar el registro de los datos, esto puede lograrse si el estado inicial

produce los controles: capture=0 y habilita =1. Esto permite la especificación del diagrama de

estado completo del controlador, que se muestra en la Figura 13.40.

reset

E0

lea=0

E6

capture=1

h=0

c=1

lea=1

a

g

E5

h=0

E1

ocupadoS=0

c=0

ocupadoS=0

b

E2

c=0

E3

d

c=1

e

ocupadoS=1

f

E4

h=1

ocupadoS=1

Figura 13.40. Diagrama de estados del controlador.

Profesor Leopoldo Silva Bijit

19-01-2010

28

Sistemas Digitales

Descripción del controlador en Verilog.

module controlador(clk, reset, lea, capture, habilita, comando, ocupado);

// Interfaz con el sistema sincrónico

input clk; // reloj del sistema

input reset;

input lea;

// Interfaz con el dispositivo asincrónico

input ocupado;

reg ocupado1, ocupadoS;

output capture, habilita, comando;

reg capture, habilita, comando;

// Estados internos

reg [2:0] estado;

reg [2:0] proximoestado;

// Declaraciones de estado

parameter E0 = 0;

parameter E1 = 1;

parameter E2 = 2;

parameter E3 = 3;

parameter E4 = 4;

parameter E5 = 5;

parameter E6 = 6;

always @ (negedge clk) //sincronización

begin

ocupado1 <= ocupado;

ocupadoS <= ocupado1;

end

always @ (posedge clk or posedge reset) //cambio de estado

begin

if (reset) estado <= E0;

else estado <= proximoestado;

end

always @ (estado or ocupadoS or lea) //Red de salida y próximo estado

begin

case (estado)

E0: begin

capture = 0; habilita = 1; comando=1;

if(lea) proximoestado = E1;

else proximoestado = E0;

end

E1: begin

capture = 0; habilita = 1; comando=0;

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

29

proximoestado = E2;

end

E2: begin

capture = 0; habilita = 1; comando=0;

proximoestado = E3;

end

E3: begin

capture = 0; habilita = 1; comando=1;

if (ocupadoS) proximoestado = E4;

else proximoestado = E3;

end

E4: begin

capture = 0; habilita = 1; comando=1;

if (!ocupadoS) proximoestado = E5;

else proximoestado = E4;

end

E5: begin

capture = 0; habilita = 0; comando=1;

proximoestado = E6;

end

E6: begin

capture = 1; habilita = 0; comando=1;

proximoestado = E0;

end

default: begin

capture = 1; habilita = 0; comando=1;

proximoestado = E0;

end

endcase

end // always @ (estado or ocupadoS or lea)

endmodule // controlador

Simulación del controlador.

El siguiente módulo genera estímulos para simular funcionalmente el módulo controlador.

`timescale 1ns / 1ps

module test_v;

// Inputs

reg clk;

reg reset;

reg lea;

reg ocupado;

// Outputs

wire capture;

Profesor Leopoldo Silva Bijit

19-01-2010

30

Sistemas Digitales

wire habilita;

wire comando;

// Instantiate the Unit Under Test (UUT)

controlador uut (

.clk(clk),

.reset(reset),

.lea(lea),

.capture(capture),

.habilita(habilita),

.comando(comando),

.ocupado(ocupado)

);

initial begin

// Initialize Inputs

clk = 0; reset = 0; lea = 0; ocupado = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

reset=1; clk=0; #100; clk=1; #100;

reset=0; clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

lea=1; clk=0; #100; clk=1; #100;

lea=0; clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; ocupado=1;clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; ocupado=0;clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

clk=0; #100; clk=1; #100;

end

endmodule

Se generan las siguientes formas de ondas.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

31

Figura 13.41. Simulación funcional del controlador.

Profesor Leopoldo Silva Bijit

19-01-2010

32

Sistemas Digitales

Problemas resueltos.

Problema 13.1. Contador

Se tiene un contador binario módulo 5 ascendente (Q2Q1Q0) y un contador binario módulo7

descendente (Q5Q4Q3), con Q3 y Q0 las cifras menos significativas.

a) Diseñar las ecuaciones del contador módulo 5 empleando flip-flops Ds.

b) Diseñar las ecuaciones del contador módulo 7 empleando flip-flops JKs.

c) Generar salida z, que se ponga alta cuando el contador módulo 5 pasa por la cuenta decimal

3, y que se ponga baja cuando el contador módulo 7 pase por la cuenta decimal 1. Si se

producen simultáneamente las cuentas anteriores, la salida debe pasar a cero.

d) Indicar mediante un esquema temporal, respecto de los estados de los contadores y del reloj,

cuando cambia la salida z.

Solución.

a) Para el contador binario módulo 5 ascendente:

Q2Q1

00

Q0

01

0

0

001

1

010

11

2

ΦΦΦ

011

1

100

10

3

ΦΦΦ

6

7

4

000

ΦΦΦ

5

Q2+Q1+Q0+

Figura P13.1. Contador módulo cinco

D2 = Q2+ = Q1Q0

D1 = Q1+ = Q1Q0’ + Q1’Q0 D0 = Q0+ = Q2’Q0’

b) Para el contador binario módulo 7 descendente:

Q5Q4

00

Q3

01

0

0

110

1

000

11

2

001

1

010

10

6

3

ΦΦΦ

4

011

101

7

5

100

Q5+Q4+Q3+

Figura P13.2. Contador módulo siete

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

33

Q5+ = J5Q5’ + K5’Q5 = Q5Q4 + Q5Q3 + Q5’Q4’Q3’; J5 = Q4’Q3’

K5 = Q4’Q3’

Q4+ = J4Q4’ + K4’Q4 = Q4Q3 + Q4’Q3’;

J4 = Q3’

K4 = Q3’

Q3+ = J3Q3’ + K3’Q3 = Q4Q3’ + Q5Q3’;

J3 = Q4 + Q5 K3 = 1

c) Las condiciones se obtienen según:

C3 = Cuenta 3 decimal del módulo 5 = Q2’Q1Q0

C1 = Cuenta 1 decimal del módulo 7 = Q5’Q4’Q3

La siguiente tabla muestra el estado de los contadores, los valores de los decodificadores de

cuenta igual a tres (C3), e igual a uno (C1). También se ilustra el estado de la salida,

considerando que desde el canto de subida de C3 la salida Z toma valor 1, y que Z toma valor

cero desde el canto de subida de C1.

Mod5

Mod7

C3

C1

Z

0

0

0

0

0

1

6

0

0

0

2

5

0

0

0

3

4

1

0

1

4

3

0

0

1

0

2

0

0

1

1

1

0

1

0

2

0

0

0

0

3

6

1

0

1

4

5

0

0

1

0

4

0

0

1

1

3

0

0

1

2

2

0

0

1

3

1

1

1

0

4

0

0

0

0

0

6

0

0

0

1

5

0

0

0

2

4

0

0

0

3

3

1

0

1

4

2

0

0

1

0

1

0

1

0

1

0

0

0

0

2

6

0

0

0

3

5

1

0

1

Figura P13.3. Estados y salidas. Solución 1.

También se considera correcta la siguiente tabla que muestra los cambios de Z con los cantos de

bajada de las señales C3 y C1.

Mod5

Mod7

C3

C1

Z

0

0

0

0

0

1

6

0

0

0

2

5

0

0

0

3

4

1

0

0

4

3

0

0

1

0

2

0

0

1

1

1

0

1

1

2

0

0

0

0

3

6

1

0

0

4

5

0

0

1

0

4

0

0

1

1

3

0

0

1

2

2

0

0

1

3

1

1

1

1

4

0

0

0

0

0

6

0

0

0

1

5

0

0

0

2

4

0

0

0

3

3

1

0

0

4

2

0

0

1

0

1

0

1

1

1

0

0

0

0

2

6

0

0

0

3

5

1

0

0

Figura P13.4. Estados y salidas. Solución 2.

La variable z, debe almacenarse en un flip-flop. No puede obtenerse en términos

combinacionales a partir de C1 y C3.

Lo anterior puede determinarse de varias formas, se consideran correctas, cualquiera de las

explicaciones siguientes:

c1) Observando un valor de uno de los contadores (por ejemplo la cuenta 4 del contador módulo

5), se aprecia que Z a veces es uno y otras es cero, ya que depende del valor anterior de Z.

c2) Si puede construirse una matriz de transiciones y Z+ depende del valor actual de Z.

En el caso que Z+ no dependiera de Z se trataría de una situación combinacional.

c3) Si se puede dibujar un diagrama de estados.

Profesor Leopoldo Silva Bijit

19-01-2010

34

Sistemas Digitales

Para confeccionar la tabla de transiciones, se asume que inicialmente z es cero. Entonces si C3 y

C1 son ceros, se conserva el estado de la salida z; si ambas son unos, entonces el próximo valor

de z es cero.

Cuando C3 pasa a 1 estando Z en 0, el próximo valor de Z será 1; y si era 1 permanece en ese

valor.

Cuando C1 pasa a 1 estando Z en 1, el próximo valor de Z será 0; y si era 0 permanece en ese

valor.

C3C1

00

z

01

0

0

1

0

1

11

2

0

1

0

6

Z=0

4

1

0

3

0 ,11

10

7

0

1

5

10

1

Z=1

0

z+

Figura P13.5. Matriz de transiciones.

La función secuencial queda:

z+ = C3C1’ + C1’ z

Con flip-flop D resulta Dz = (Q2’Q1Q0 + z) (Q5 +Q4 +Q3’)

Con JK, resulta: Jz = C3C1’ = Q2’Q1Q0(Q5 +Q4 +Q3’)

Kz = C1 = Q5’Q4’Q3

d) La implementación anterior conduce a las siguientes formas de ondas, donde z cambia con

los cantos de bajada de las señales C3 y C1. El próximo estado se calcula con los valores

actuales y toma su valor después del canto sincronizante.

clk

C3

C1

z

Figura P13.6. Formas de ondas.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

35

Los diagramas se ilustran con flip-flops activados por canto de subida. La salida z, tiene su

canto de subida coincidente con el canto de bajada de C3, y su canto de bajada coincidente con

el canto de bajada de C1. La señal z es sincrónica, y su ancho de pulso es variable.

La implementación de cambios de z con los cantos de subida de C3 y C1, mediante flip-flops

JK o D, debe basarse en generar la señal C3 cuando el contador módulo 5 pase por la cuenta dos

(Q2’Q1Q0’), y la señal C1 cuando el contador módulo siete pasa por la cuenta dos (Q5’Q4Q3’).

También se consideran correctas soluciones basadas en latchs.

Alternativamente las señales C3 y C1 pueden emplearse para comandar un latch de nor (que

opera con cantos de subida), y tal que el comando set sea C3C1’, y el comando reset sea: C1.

R

clk

Z

C1

C3

C1

S

C3C1’

z

Figura P13.7. Latch de nor.

En el largo plazo la señal z es periódica, después de 35 (5*7) pulsos del reloj, ambos contadores

pasan por cero simultáneamente.

Mod5 0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0

Mod7 0 6 5 4 3 2 1 0 6 5 4 3 2 1 0 6 5 4 3 2 1 0 6 5 4 3 2 1 0 6 5 4 3 2 1 0

Problema 13.2.

Diseño de máquina de estados.

Para el siguiente diagrama de estados, asumir que el estado inicial es el A, al cual se llega

reseteando asincrónicamente los flip-flops.

a) Explicar el objetivo de la máquina secuencial.

b) Determinar matriz de transiciones.

c) Determinar los estados adyacentes de acuerdo a las reglas de asignación. Indicar los nombres

binarios elegidos para cada estado lógico.

d) Determinar las ecuaciones de próximo estado y de salida.

e) Diseñar empleando flip-flops de tipo D, dibujando el esquemático.

Profesor Leopoldo Silva Bijit

19-01-2010

36

Sistemas Digitales

inicial

1/1

A

0/0

B

0/0

1/0

0/1

C

1/0

Figura P13.8. Problema 13.2.

Solución.

a) Se genera un uno en la salida después de una secuencia, de cualquier largo, de ceros o de

unos de la entrada.

Más específicamente, se genera salida uno cuando llega un:

uno en secuencias de uno o más ceros seguidos 01, 001, 0001, 00001, ....

cero en secuencias de uno o más unos seguidos 10, 110, 1110, 11110, ....

b) Se tiene

x

Estado 0

1

A

B/0 C/0

B

B/0 A/1

C

A/1 C/0

Estado+

Figura P13.9. Matriz de transiciones Problema 13.2.

c) Regla 1: Deben ser adyacentes A con B; y A con C

Regla 2: Deben ser adyacentes: B con C, A con B, y A con C

Regla 3: Deben ser adyacentes A con B y A con C.

A debe ser el estado 00 para que se llegue a él, al resetear los flip-flops.

Asignación 1: B = 01; C = 10. Asignación 2: B = 10; C = 01.

Existen dos asignaciones posibles, que cumplen todas las reglas, excepto que B y C sean

adyacentes:

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

37

Asig 1

Q1Q0

A=00

B=01

11

C=10

x

0

1

01/0 10/0

01/0 00/1

dd/d dd/d

00/1 10/0

Q1+Q0+/z

Q1+ = x Q0’; Q0+ = x’Q1’

z = x’ Q1 + x Q0

Asig 2

Q1Q0

A=00

C=01

11

B=10

x

0

1

10/0 01/0

00/1 01/0

dd/d dd/d

10/0 00/1

Q1+Q0+/z

Q1+ = x’ Q0’ ; Q0+ = xQ1’

z = x’Q0 +x Q1

Figura P13.10. Asignaciones Problema 13.2.

e) Para el diseño con la asignación 1, se tienen:

D1 = x Q0’ ; D0 = x’Q1’; z = x’ Q1 + x Q0

Se obtiene:

x

Q1

D1

Q1’

z

Q0

D0

Q0’

Figura P13.11. Esquemático Problema 13.2.

Para el diseño 2, con Q1 = x’ Q0’ ; Q0 = x Q1’ ; z = x’Q0 + x Q1 el esquemático es similar.

Problema 13.3.

Contador binario

Diseñar un contador binario con salidas sincrónicas, que cuente en forma ascendente si

C = 1; y en forma descendente si C = 0. Si M = 0 debe contar en módulo 5; si M = 1, debe

contar en módulo 7.

Si se cambian los controles, debe ir a la cuenta siguiente, en caso que ésta exista; si la cuenta no

existe debe ir a la cuenta 0.

Profesor Leopoldo Silva Bijit

19-01-2010

38

Sistemas Digitales

a) Escribir la matriz de transición para el contador en función de Q2, Q1, Q0, M y C.

b) Diseñar en base a flip-flops D las ecuaciones de próximo estado en función de Q2, Q1, Q0,

M=0 y C=0.

c) Diseñar en base a flip-flops J-K las ecuaciones de próximo estado en función de Q2, Q1, Q0,

M=1 y C=1.

d) Setear un latch de nand cuando el contador pase por la cuenta 3 y resetear el latch cuando el

contador pase por cuenta 0.

Solución:

a)

1 , 00

111

1

000

0, 11

01

1

0

00

10

110

001

0

01

010

10

01

0

11

0

101

11

Q2Q1Q0

0

100

1

011

1

CM

Figura P13.12. Diagrama de estados Problema 13.3.

Q2Q1Q0

000

001

011

010

110

111

101

100

00

100

000

010

001

000

000

100

011

CM

01

11

110

001

000

010

010

100

001

011

101

000

110

000

100

110

011

101

Q2+Q1+Q0+

10

001

010

100

011

000

000

000

000

Figura P13.13. Matriz de transiciones Problema 13.3.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

39

b)

Q2Q1

00

Q0

01

11

0

0

100

10

2

001

6

000

4

Q2+ = Q2’Q1’Q0’ + Q2Q1’Q0 = D2

011

Q1+ = Q2’Q1Q0 + Q2Q1’Q0’ = D1

1

000

1

3

010

000

7

100

5

Q0+ = Q2’Q1Q0’ + Q2Q1’Q0’ = D2

Q2+ Q1+ Q0+

Figura P13.14. Diseño con M=0 y C=0 Problema 13.3.

c)

Q2Q1

00

Q0

01

0

0

001

11

2

011

10

6

000

4

Q2+ = Q2Q1’ +Q2’Q1Q0 = J2Q2’+K2’Q2

101

Q1+ = Q1’Q0 +Q2’Q1Q0’ = J1Q1’+K1’Q1

1

010

1

100

3

000

7

110

5

Q0+ = Q2’Q0’+Q1’Q0’

= J0Q0’+K0’Q0

Q2+ Q1+ Q0+

Figura P13.15. Diseño con M=1 y C=1 Problema 13.3.

J2 = Q1Q0

J1 = Q0

J0 = Q2’ + Q1’

K2 = Q1

K1 = Q2 + Q0

K0 = 1

d) La cuenta tres ocurre cuando Q2’Q1Q0 es 1.

Por lo tanto S’ = Q2 + Q1’ + Q0’ es la negación de la cuenta tres.

Cuando la cuenta tres tiene un canto de subida se desea que S’ tenga un canto de bajada.

La cuenta cero ocurre cuando Q2’Q1’Q0’ es 1. Por lo tanto R’ = Q2 + Q1 + Q0

La implementación con NAND, es: S’ = (Q2’ Q1 Q0)’ y R’ = (Q2’Q1’Q0’)’

Otra solución para d).

Sea L la salida del latch (usualmente denominada Q).

Estando L en cero, sólo pasa a uno cuando llega a la cuenta 3; estando en estado uno el latch

pasa a cero cuando entra a la cuenta cero. Se tiene entonces la matriz de transiciones siguiente:

Profesor Leopoldo Silva Bijit

19-01-2010

40

Sistemas Digitales

L

0

1

000

0

0

001

0

1

011

1

1

Q2Q1Q0

010

110

0

0

1

1

L+

111

0

1

101

0

1

100

0

1

Figura P13.16 Salida del latch Problema 13.3.

Empleando la siguiente tabla de excitaciones:

Q Q+ S’ R’

0 0 1

0 1 0 1

1 0 1 0

1 1

1

Figura P13.17. Tabla excitaciones Problema 13.3.

Se logran los programas para S’ y R’:

L

0

1

000

1

10

001

1

1

011

01

1

Q2Q1Q0

010

110

1

1

1

1

S’R’

111

1

1

101

1

1

100

1

1

Figura P13.18. Programas SR Problema 13.3.

Resultan: S’ = Q2 + Q1’ + Q0’

Q2’

Q1

Q0

S’

Q2’

Q1’

Q0’

R’

y R’ = Q2 +Q1 + Q0

L

Figura P13.19. Latch SR Problema 13.3.

Problema 13.4.

Se tiene el siguiente circuito:

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

41

Z

x

T

D

Q1

Flip-flop T

Q0

Flip-flop D

clk

Figura P13.20. Esquemático Problema 13.4.

Si en t = 0 se tienen Q1 = 0 y Q0 = 0, con las siguientes formas de ondas:

clk

x

t=0

Figura P13.21. Formas de ondas Problema 13.4.

La señal x cumple las condiciones de set-up y hold.

a) Determinar las formas de ondas de Q1, Q0 y Z, relativas al clk y x.

b) Determinar la matriz de transiciones en el formato:

x

Q1Q0

00

01

11

10

0

1

Q1+ Q0+

Figura P13.22. Formato matriz de transición Problema 13.4.

Solución:

Del esquemático, se tienen:

T = X +Q0 ; D = Q1 ; Z = X + Q1

Ecuaciones de los flip-flops: Q1+ = T Q1 ; Q0+ = D

Reemplazando en las ecuaciones de los flip-flops, se obtienen:

Profesor Leopoldo Silva Bijit

19-01-2010

42

Sistemas Digitales

Q1+ = (X+Q0)Q1’ + (X+Q0)’Q1 = Q1’Q0 + Q1Q0’X’ + Q1’ X

Q0+ = Q1

Es un modelo de Meely.

Como los flip-flops operan con cantos de subida, se tiene la siguiente secuencia de entrada:

X

= {0,

1, 0,

0, 1,

0 ..}

Se genera la secuencia de estados y salida:

Q1Q0/Z = 00/0, 10/1, 11/1, 01/1, 10/1, 11/1..}

Q1Q0

00

01

11

10

x

0

1

00/0

10/1

10/0

10/1

01/1

01/1

11/1

01/1

Q1+ Q0+/Z

Figura P13.23. Matriz de transición Problema 13.4.

Las formas de ondas de Q1 y Q0 muestran los retardos de propagación a través de los flip-flops.

El cual se considera despreciable respecto del período del reloj.

La forma de Z, ilustra la dependencia de la salida con la entrada, y también asume que el retardo

a través de la compuerta or, es despreciable respecto del período del reloj. Debe notarse que Z

cambia entre cantos de subida del reloj; es decir, no es una señal sincrónica, lo cual es

característico del modelo de Meely.

clk

x

t=0

Q1

Q0

Z

Figura P13.24. Formas de ondas Problema 13.4.

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

43

Problema 13.5.

Se desea diseñar un contador con una entrada de control C, tal que:

Cuando C=0, el contador cuente en la secuencia: 000, 001, 010, 011, 100, 101, 110, 111.

Cuando C=1, el contador cuenta en la secuencia: 000, 001, 011, 010, 110, 111, 101, 100

El flip-flop más significativo es Q2; el menos significativo es Q0.

Q2 y Q1 son flip-flops Ds; y Q0 es flip-flop JK.

Las secuencias deben repetirse. Si cambia C durante la ejecución debe seguir contando según el

nuevo valor, no retorna al estado inicial. Estado inicial: 000

Determinar las ecuaciones para programar los flip-flops. No dibujar circuito.

Solución.

Matriz de transiciones:

Q2Q1

Q0C

00

00

001

01

001

11

011

10

010

01

0

11

4

011

1

110

3

2

010

100

12

111

5

13

111

7

15

101

6

10

14

000

8

101

000

9

11

100

10

110

Q2+, Q1+, Q0+

Figura P13.25. Matriz de transiciones Problema 13.5.

Hay dos diseños para D2:

Q2+ = Q2'Q1Q0C'+Q1Q0'C+Q2Q0'C'+Q2Q0C+Q2Q1'Q0 (o Q2Q1'C') =D2

Para D1:

Q1+ = Q1Q0'+Q2'Q0C+Q1'Q0C'

=D1

Para el JK, se tiene:

Q0+=Q0'C'+Q2'Q1'C+Q2Q1C=Q0'(C'+Q2'Q1'C+Q2Q1C)+Q0( Q2'Q1'C+Q2Q1C)

Comparando coeficientes:

J0 = C'+Q2'Q1'C+Q2Q1C

K0 = ( Q2'Q1'C + Q2Q1C)'

Arreglando:

K0 = ( Q2+Q1+C')( Q2'+Q1'+C')

Profesor Leopoldo Silva Bijit

19-01-2010

44

Sistemas Digitales

Índice general.

CAPÍTULO 13 ............................................................................................................................................1

BLOQUES BÁSICOS SECUENCIALES.................................................................................................1

13.1. CONTADORES. ..................................................................................................................................1

13.1.1. Contador sincrónico binario módulo 4. ...................................................................................1

13.1.2. Contador sincrónico binario módulo 8. ...................................................................................3

13.1.3. Contador sincrónico binario módulo 16. .................................................................................5

13.1.4. Contador binario de ripple, con salida asincrónica. ...............................................................7

13.1.5. Contador de anillo (ring counter). ...........................................................................................8

13.1.6. Contador de Johnson. ..............................................................................................................9

13.1.7. Contador integrado 74163. ....................................................................................................10

13.1.8. Contador sincrónico binario módulo 32. ...............................................................................12

13.1.9. Contador sincrónico módulo 7. ..............................................................................................12

13.1.10. Contador sincrónico módulo 6. ............................................................................................13

13.2. REGISTROS DE DESPLAZAMIENTO. ..................................................................................................13

13.2.1 Usos. .......................................................................................................................................14

13.2.2. Ejemplo de diseño. .................................................................................................................14

13.2.3. Registro de desplazamiento a la derecha de largo 4. ............................................................15

13.2.4. Registros de desplazamiento TTL ..........................................................................................15

13.2.5. Registro universal 74194A. ...................................................................................................16

13.3. REGISTROS. ....................................................................................................................................18

13.3.1. Registro de almacenamiento. .................................................................................................18

13.3.2. Registro de desplazamiento....................................................................................................19

13.3.3. Diseño de máquinas en base a registros ................................................................................19

13.4. ALTERNATIVAS DE DISEÑO DE MÁQUINAS SECUENCIALES. ...........................................................19

13.4.1. Diseño basado en ROM. ........................................................................................................19

13.4.2. Diseño basado en PLD...........................................................................................................20

13.4.3. Secuenciador. .........................................................................................................................20

Ejemplo 13.1. .....................................................................................................................................20

13.5. DISEÑO DE CONTROLADORES. ........................................................................................................23

Especificación del dispositivo. ...........................................................................................................23

Especificación del sistema sincrónico................................................................................................24

Diseño del controlador. .....................................................................................................................25

Descripción del controlador en Verilog.............................................................................................28

Simulación del controlador. ...............................................................................................................29

PROBLEMAS RESUELTOS. ........................................................................................................................32

Problema 13.1. Contador...................................................................................................................32

Problema 13.2. ...................................................................................................................................35

Problema 13.3. ...................................................................................................................................37

Problema 13.4. ...................................................................................................................................40

Problema 13.5. ...................................................................................................................................43

ÍNDICE GENERAL. ....................................................................................................................................44

ÍNDICE DE FIGURAS .................................................................................................................................45

Profesor Leopoldo Silva Bijit

19-01-2010

Capítulo 13. Bloques básicos secuenciales

45

Índice de figuras

Figura 13.1. Matriz transiciones contador módulo 4. .................................................................... 1

Figura 13.2. Matriz de transiciones contador módulo 4. ............................................................... 2

Figura 13.2.a. Esquemático contador módulo 4. ........................................................................... 2

Figura 13.3. Matriz de transiciones contador módulo 8. ............................................................... 3

Figura 13.4. Matriz de transiciones y diagrama de estados para contador módulo 8. ................... 3

Figura 13.5. Esquemático contador módulo 8 mediante JK. ......................................................... 4

Figura 13.6. Formas de ondas contador módulo 8. ....................................................................... 5

Figura 13.7. Matriz de transiciones contador módulo 16. ............................................................. 5

Figura 13.8. Esquemático contador módulo 8 mediante JK. ......................................................... 6

Figura 13.9. Formas de ondas contador módulo 16. ..................................................................... 6

Figura 13.10. Disminución fan-out. .............................................................................................. 7

Figura 13.11 Contador ondulado o de ripple. ................................................................................ 7

Figura 13.12. Formas de ondas contador ripple. ........................................................................... 8

Figura 13.13. Contador de anillo. .................................................................................................. 8

Figura 13.14. Formas de ondas contador de anillo. ....................................................................... 9

Figura 13.15. Contador de Johnson. .............................................................................................. 9

Figura 13.16. Formas de ondas contador Johnson. ..................................................................... 10

Figura 13.17. Esquemático contador 74163. ............................................................................... 11

Figura 13.17a. Especificación contador 74163. .......................................................................... 11

Figura 13.18. Contador sincrónico módulo 7. ............................................................................. 12

Figura 13.19. Contador sincrónico módulo 6. ............................................................................. 13

Figura 13.20. Transferencia entre dos flip-flops. ........................................................................ 14

Figura 13.21. Registro de desplazamiento a la derecha de largo 4. ............................................ 15

Figura 13.22. Formas de ondas en registro de desplazamiento. .................................................. 15