registro de secuencia y decodificador

Anuncio

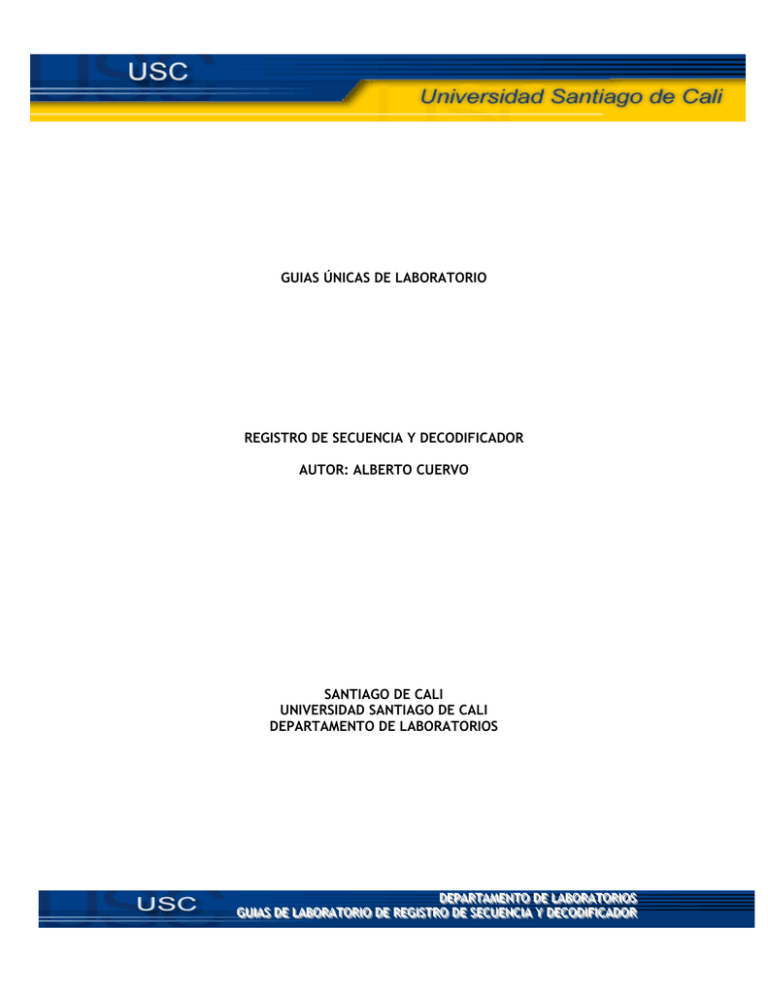

GUIAS ÚNICAS DE LABORATORIO REGISTRO DE SECUENCIA Y DECODIFICADOR AUTOR: ALBERTO CUERVO SANTIAGO DE CALI UNIVERSIDAD SANTIAGO DE CALI DEPARTAMENTO DE LABORATORIOS DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR REGISTRO DE SECUENCIA Y DECODIFICADOR OBJETIVO Con mucha frecuencia los diseñadores de circuitos digitales de control utilizan distintos métodos de diseño buscando la implementación de un circuito que produzca la secuencia de control deseada de forma lógica y directa para ahorrar tiempo en el diseño y facilitar el reconocimiento de la secuencia de eventos por los cuales pasa el control por cualquier persona diferente al diseñador. Con esto se facilita la labor de mantenimiento posterior de los equipos digitales así construídos. Uno de estos métodos de diseño de circuitos secuenciales lo constituye el “método del registro de secuencia y decodificador”. Este método utiliza un registro para dar secuencia a los estados del control, el cual se decodifica para suministrar una salida por cada estado. Si el registro contiene n flipflops, el circuito tendrá 2n estados y el decodificador 2n salidas. La presente práctica tiene como objetivo reforzar los conocimiento del estudiante utilizando este método para diseñar una unidad de control cuya especificación viene dada en el lenguaje de transferencia entre registros. PLANTEAMIENTO DEL PROBLEMA Las siguientes operaciones de transferencia entre registros especifican una unidad de control de cuatro estados del tipo: registro de secuencia y decodificador. G es un registro de secuencia de dos bits (utilice dos flip-flops JK) y T0, T1, T2 y T3 son las salidas del decodificador. x, y,z,.......son señales de entrada a la unidad de control, donde solamente una de ellas toma el valor binario 1. A es un registro de 4 bits del procesador de datos (A3, A2, A1 y A0). xT0 : G←G+1 yT0 : G←10 zT0 : G←11 T1 + T2 + T3 : G←G+1 T0 : A←4 T1 : A←shlA, A0←A3 T2 : A←shrA, A3←A0 T3 : A←0 DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR x y z registro de secuencia G2 LÓGICA G1 D E C O D I F I C A D O R .T0 . . . T1 T2 T3 Unidad de Control a.- Dibuje el diagrama de estados del sistema b.- Diseñe el circuito de su sistema digital utilizando los siguientes elementos del módulo DIGI-BOARD2 • • • • Dos flip-flops JK (38) para el registro de secuencia G de dos bits. El registro SRG4 (11) para el registro A Las compuertas que estime necesarias El demultiplexor (12) para el decodificador de la unidad de control La salida del registro A debe ser llevada al display de 7 segmentos y T0, T1, T2 y T3 a LEDs para poder visualizar el resultado en el registro A, así como el estado de la unidad de control después de la ocurrencia de un pulso de reloj. Los pulsos de reloj deben ser obtenidos del divisor de frecuencias (28) con una frecuencia de 1 Hz. Las señales x, y, z deben ser obtenidas de un teclado (31) Todas las conexiones deben quedar bien explícitas. c.- Diga en cada caso x=1, y=1 ó z=1 cuál es la secuencia de números que se obtiene en el display de 7 segmentos, o sea, en el registro A, así como la secuencia de estados de la unidad de control. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR SOLUCIÓN De acuerdo con las proposiciones de transferencia entre registos se deduce lo siguiente: 1. En el estado T0, si x=1 el registro G se incrementa. Si y =1, el registro G toma el valor 10, entonces el circuito secuencial pasa al estado T2. Si z = 1 toma el valor binario 11, por tanto el circuito pasa al estado T3. 2. En cualquier otro estado, T1, T2 o T3, el registro G se incrementa en forma incondicional. 3. En el estado T0, si ninguna señal es 1, el circuito se queda en el estado T0 con la ocurrencia de un pulso de reloj. De acuerdo con lo anterior se puede construir el diagrama de estados que se muestra a continuación. T1 x=y=z=0 x=1 T0 y=1 T2 z=1 T3 Diagrama de Estados De este diagrama de estados se puede construir la siguiente tabla de estados presente y siguiente, obteniéndose a partir de la misma las funciones de las entradas J y K de los dos flip-flops G1 y G2. Estado presente T0: T0: T0: T0: T1: T2: T3: Estado siguiente G2G1 0 0 x=y=z=0 x=1 00 y=1 00 z=1 00 01 10 11 G2G1 00 01 10 11 10 11 00 por tanto JG2 = yT0 + zT0 + T1 KG2 = T3 JG1 = xT0 + zT0 + T2 KG1 = 1 DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR De la tabla anterior se observa que el flip-flop G2 cambia de 0 a 1 (su entrada J debe ser 1 para que esto ocurra) cuando el circuito se encuentra en el estado T0 y “y”=1, o se encuentra en el estado T0 y “z”=1, o cuando está en el estado T1. Por tanto la función para la entrada J del flip-flop G2 será como la mostrada anteriormente. Similarmente se observa que una transición de 1 a 0 en este flip-flop ocurre solamente en el estado T3, por tando la entrada K del flip-flop G2 es igual a T3, etc. Por tanto el circuito de la unidad de control será como se muestra a continuación, donde la red lógica queda determinada por las funciones anteriormente encontradas las cuales deben ser implementadas con las compuertas lógicas que dispone el módulo DIGIBOARD2. X Y Z 1J G1 A0 A1 R E D 1K L O G I C A 1J 0 1 DX & G2 T0 T1 T2 T3 1 1K reloj Circuito de la Unidad de Control Las señales de salida del circuito de la unidad de control serán las salidas del decodificador T0, T1, T2 y T3 que irán al registro A (SRG4) para dar secuencia a las microoperaciones que se deben ejecutar en el mismo. Las proposiciones de transferencia entre regiastro especifican lo siguiente: DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR • En el estado T0 se debe almacenar el #4 en el registro A, por tanto en este estado el modo del registro debe ser M1M0= 11 • En el estado T1 debe ocurrir un desplazamiento a la izquierda del dato almacenado en el registro A introduciendo el bit de mayor orden A3 en la posición de menor orden. Por lo anterior, en este estado el modo debe ser M1M0=01 y la salida de mayor orden del registro debe conectarse a la entrada secuencial de desplazamiento a la izquierda. • De forma similar, el estado T2 debe colocar al registro en el modo M1M0=10 para producir un desplazamiento a la derecha y la salida de menor orden debe introducirse a la entrada secuencial para desplazamiento a la derecha. • Finalmente, cuando se produzca el estado T3 debe borrarse el registro, por lo que T3´se conecta a la entrada asincrónica R del registro la cual se activa con 0 Lo anterior se muestra en la siguiente figura que muestra al registro A con sus conexiones, así como una tabla resumiendo lo anteriormente señalado. T0 T1 T2 0 M0/3 1 C4 reloj 2 SRG4 M1 M0 /1 R T3 Registro A Al display 0 0 1 0 1,4D 3,4D 3,4D T0 T1 T2 T3 1 0 1 0 1 1 0 0 M1 = T0 + T2 M0 = T0 + T1 3,4D 3,4D 2,4D BIBLIOGRAFÍA 1. M. Morris Mano, “Lógica Digital y Diseño de Computadores”, Editorial Dossat S.A.,1982 2. F. Hill y G. Peterson, “Digital Systems: Hardware Organization and Design”, Nueva York: John Wiley & Sons, 1973. 3. System Technick, “Módulo DIGI-BOARD2: Descripción Técnica” DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE LLAABBOORRAATTOORRIIOO DDEE RREEGGIISSTTRROO DDEE SSEECCUUEENNCCIIAA YY DDEECCOODDIIFFIICCAADDOORR