IEE 2712 Sistemas Digitales

Anuncio

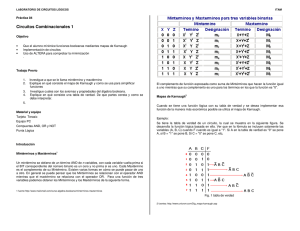

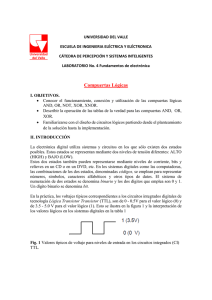

IEE 2712 Sistemas Digitales Clase 6 Objetivos educacionales: 1. Saber aplicar el método de mapas de Karnaugh para 5 o más variables y para situaciones no-importa. 2. Conocer la implementación práctica de las compuertas lógicas. 3. Introducir el concepto de diseño y herramientas que lo facilitan. Minimización de funciones binarias Mapas de Karnaugh Mapas de 5: se pueden usar dos mapas de 4 variables, e imaginárselo uno encima del otro. ¿Cómo hacerlo para 6 variables? 1 Minimización de funciones binarias Mapas de Karnaugh Situaciones no-importa (don’t care): para ciertos minitérminos no importa cuál es el resultado de la función. Por ejemplo • Esa entrada nunca se da (código BCD por ejemplo) • El valor de la función realmente no importa para esa entrada (algo como el ángulo de un vector cuando la magnitud es cero) Minimización de funciones binarias Mapas de Karnaugh Ejemplo: 2 2.4 Más sobre compuertas a) b) c) d) Simbología Nivel de integración Familia lógica Lógica positiva y negativa a) Simbología de compuertas 3 Simbología de compuertas b) Circuitos integrados: nivel de integración • SSI (small-scale integrated): Las entradas y salidas están directamente conectadas a los pins (no más de 10 compuertas) 4 Circuitos integrados: nivel de integración • MSI (medium-scale integrated): Contiene entre 10 y 100 compuertas. Típicamente realizan una tarea específica simple (BCD a Decimal, por ejemplo). Circuitos integrados: nivel de integración • LSI (large-scale integrated): Contiene entre 100 y algunos miles de compuertas. Por ejemplo, procesadores pequeños, memorias, etc. NLC0048 Modular exponentiation 5 Circuitos integrados: nivel de integración • VLSI (Very large-scale integrated): Contiene entre varios miles a cientos de millones de compuertas. Las CPU más complejas por ejemplo. c) Circuitos integrados: familias lógicas Indica la implementación electrónica de la compuerta. Las más comunes son: • TTL transistor-transistor logic y • CMOS complementary metal-oxide semiconductor compuerta NOR TTL compuerta NAND CMOS 6 d) Lógica positiva o negativa Lógica positiva: Se asigna el valor 1 al voltaje mayor (H) Lógica negativa: Se asigna el valor 1 al voltaje menor (L) Para TTL, H es entre 2 y 5 V y L entre 0 y 0,8 V Lógica positiva o negativa Ejemplo de implementación de la misma tabla de verdad en lógica positiva y lógica negativa 7 3. Diseño de lógica combinacional 3.1 Circuitos combinacionales 3.2 Conceptos de diseño 3.3 Análisis de circuitos combinacionales 3.4 Diseño de circuitos combinacionales 3.5 Decodificadores 3.6 Codificadores 3.7 Multiplexores 3.8 Sumadores binarios 3.9 Restadores 3.10 Sumadores-restadores binarios 3.11 Multiplicadores binarios 3.12 Aritmética decimal 3.13 Representación HDL 3.1 Circuito combinacional • Las salidas, en cualquier momento, son una combinación del valor de las entradas • Hay 2n posibles combinaciones para la entrada • Cada salida tiene un valor único para cada una de esas 2n entradas • Las salidas se pueden especificar con una tabla de verdad o • Las salidas se pueden especificar con una función binaria de las entradas 8 3.2 Conceptos de diseño Diseño jerárquico 3.2 Conceptos de diseño Diseño jerárquico 9 3.2 Conceptos de diseño Diseño Top-down Primero se especifica la funcionalidad del bloque completo, y luego las partes necesarias 3.2 Conceptos de diseño Diseño asistido por computador, CAD 10 3.2 Conceptos de diseño Lenguajes descriptores de hardware Hardware Description Language (HDL) • VHDL – Very-High-Speed Integrated Circuit, VHSIC HDL – Usaremos VHDL como ejemplo en este curso • Verilog – desarrollado por Gateway Design automation Co., pertenece a Cadence Design Systems Inc. 3.2 Conceptos de diseño Lenguajes descriptores de hardware Parecidos a lenguajes de programación, pero con uso intensivo de procesamiento paralelo. Ventajas: • Descripción estructurada (en vez de diagramas) • Descripción de alto nivel • Permite simulación • Síntesis lógica (RTL, Register Transfer Language) 11 3.2 Conceptos de diseño Lenguajes descriptores de hardware Compilador • Análisis. Revisa sintaxis y semántica. • Elaboración. Genera los módulos interconectados. Simulador Pasos típicos: • Inicialización. Inicialización de variables y estados. • Simulación. Ejecuta el modelo. 12