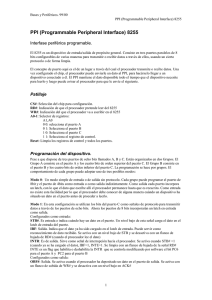

Interface paralelo programable 8255.

Anuncio

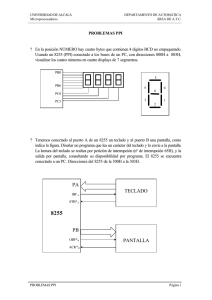

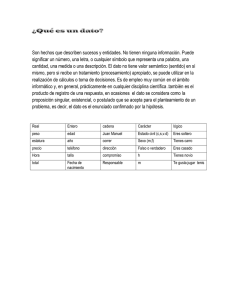

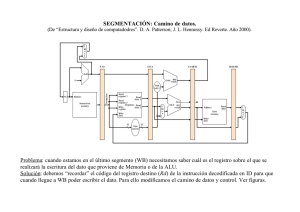

SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Interface paralelo programable 8255. 1 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Comunicaciones paralelo. ➲ CARACTERÍSTICAS ➯ Transferencia simultánea de bits por líneas separadas ➯ Ventaja: frecuencias de transmisión mayores ➯ Desventaja: el coste de las líneas cortas distancias 2 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Interface paralelo programable 8255. ➲ CARACTERÍSTICAS • • • • • 3 Puertos de E/S. 2 de tamaño byte. 1 de tamaño, 2x4 bits con control bit a bit. Disposición de los puertos como entradas, como salidas o bidireccionales. Líneas de protocolo. 3 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Diagrama de bloques PUERTO A CONTROL PA7-PA0 (GRUPO A) GRUPO A PUERTO C parte alta PC7-PC4 (GRUPO A) BUS DE DATOS BUFFER BUS DE D7-D0 DATOS BUS DE DATOS INTERNO (8 bits) PUERTO C parte baja PC3-PC0 (GRUPO B) RD WR A1 A0 RESET LÓGICA DE CONTROL DE LECTURA CONTROL GRUPO B PUERTO B PB7-PB0 (GRUPO B) ESCRITURA CS Diagrama de bloques del 8255. 4 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Direcciones A1 0 0 1 1 A0 0 1 0 1 PUERTO A B C CONTROL Registro de control. GRUPO A 1 00 modo 0 01 modo 1 1X modo 2 1 entrada 0 salida 1 entrada 0 salida GRUPO B D6 D5 D4 D3 D2 D1 D0 MODO PUERTO A PUERTO C (alto) PUERTO C (bajo) PUERTO B 1 entrada 0 salida 1 entrada 0 salida MODO 0 modo 0 1 modo 1 5 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Palabra de control de bit. ➲ Escritura en la dirección con control con D7 = 0 Se utiliza para poner a 1 ó 0 los bits del PUERTO C. D/ D6 D5 D4 D3 L2 D2 L1 D1 L0 D0 0/1 Los bits D1 a D3 dan el número del bit que se debe modificar El bit D0 indica si tiene que ser un 1 o un 0. 6 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Modos de operación. ➲ Modo 0: Operación simple de E/S sin protocolo. ➯ ➯ ➯ ➯ PUERTO A (8 bits) controlado por D4. PUERTO B (8 bits) controlado por D1. PUERTO C alto (4 bits) controlado por D3. PUERTO C bajo (4 bits) controlado por D0. 7 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Cronograma modo 0. MODO 0 (ENTRADA) RD ENTRADA DATO CS, A1, A0 DATO D -D 7 0 MODO 0 (SALIDA) WR D -D 7 0 DATO CS, A1, A0 DATO SALIDA Cronograma del modo 0 8 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Modo 1: ➲ Entrada/Salido con protocolo. ➯ PUERTO A (8 bits) controlado por D4. ➯ PUERTO B (8 bits) controlado por D1. ➯ PUERTO C señales de protocolo. ➲ Señales de protocolo: Entrada: STB A (Strobe input) Un 0 en esta línea de entrada al 8255 carga un dato en el latch del PUERTO A. IBFA (Input buffer full) Un 1 en esta línea de salida indica que el dato ha sido cargado en el latch. IBF se hace 1 cuando STB es 0 y se hace 0 con el flanco de subida de la señal RD, es decir, cuando la CPU ha leído el dato. 9 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Salida: OBF A (Output buffer full) Esta línea de salida será 0 para indicar que la CPU ha puesto un dato en el PUERTO A y que este debe ser recogido por el dispositivo exterior. OBF será 0 con el flanco de subida de la señal WR y se hará 1 cuando la señal de entrada ACK sea 0. ACK A (Acknowledge input) Un 0 en esta entrada informa al 8255 de que los datos del PUERTO A han sido leídos. Esencialmente es una respuesta del dispositivo periférico indicando que ha sido recibido el dato enviado por la CPU. Interrupción: Para entradas INTRA es 1 cuando STBA es 1, IBFA es 1 e INTEA es 1. Para salidas INTRA es 1 cuando ACK A es 1, OBFA es 1 e INTEA es 1. 10 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Puerto A en modo 1. PUERTO A (entrada) PUERTO A (salida) PUERTO A INTE A PUERTO A INTE A PC4 STB A PC6 ACK A PC5 IBF A PC7 OBF A PC3 INTR A PC3 PC6, PC7 INTE A = PC4 E/S PC4, PC5 INTR A E/S INTE A = PC6 Puerto A en modo 1. 11 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Puerto B en modo 1. PUERTO B (entrada) PUERTO B (salida) PUERTO B INTE B PUERTO B INTE B PC2 STBB PC2 ACK B PC1 IBF B PC1 OBF B PC0 INTR B PC0 INTRB INTE B = PC2 INTE B = PC2 Puerto B en modo 1. 12 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Lectura del PUERTO C En MODO 1. Entrada: PC7 E/S PC6 E/S PC5 PC4 PC3 PC2 PC1 PC0 IBFA INTEA INTRA INTEB IBFB INTRB GRUPO A GRUPO B Salida: PC7 PC6 OBFA INTEA PC5 PC4 E/S E/S GRUPO A PC3 PC2 INTRA INTEB PC1 PC0 OBFB INTRB GRUPO B 13 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Cronograma del modo 1. MODO 1 (ENTRADA) STB IBF INTR RD ENTRADA DATO MODO 1 (SALIDA) WR OBF INTR ACK SALIDA DATO Cronograma del modo 1. 14 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Modo 2: ➲ Bidireccional con protocolo. ➯ PUERTO A (8 bits) controlado por D4. ➯ PUERTO C señales de protocolo. ➲ Señales de protocolo: STB A (Strobe input). IBFA (Input buffer full). ACK A (Acknowledge). OBF A (Output buffer full). 15 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Puerto A en modo 2. PC3 INTR PUERTO A PC7 OBF PC6 ACK PC4 STB PC5 IBF PC2, ... PC0 E/S INTE 1 INTE 2 INTE 1 = PC6 INTE 2 = PC4 Puerto A en modo 2. 16 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Cronograma del modo 1. MODO 2 (BIDIRECCIONAL) Dato desde la CPU al 8255 WR OBF INTR ACK STB IBF Dato desde el 8255 a la CPU RD BUS PERI. Dato desde el periférico al 8255 Dato desde el 8255 al periférico Cronograma del modo 2. 17 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Lectura del PUERTO C en MODO 2. PC7 PC6 OBFA INTE 1 PC5 PC4 PC3 IBFA INTE 2 INTRA GRUPO A PC2 E/S PC1 PC0 E/S E/S GRUPO B 18 SISTEMAS DE ADQUISICIÓN Y TRATAMIENTO DE DATOS ARQUITECTURA DE ENTRADA/SALIDA Interface CENTRONICS conector CENTRONICS LPT1 [0000:0408]+0 0 1 2 3 4 5 6 7 [0000:0408]+1 0 1 2 3 4 5 6 7 [0000:0408]+2 0 1 2 3 4 5 6 7 habilitación de interrupción 2 3 4 5 6 7 8 9 D0 D1 D2 D3 D4 D5 D6 D7 15 13 12 10 11 error on line out of paper acknowledge busy 1 14 16 17 strobe auto feed initialize select input 18 - 25: tierra Señales del protocolo CENTRONICS. 19