Problema de Ingeniería 1 - Electronica Digital III

Anuncio

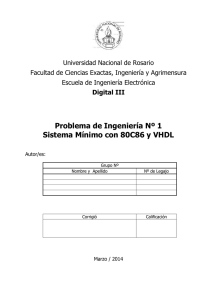

O, Universidad Nacional de Rosario Facultad de Ciencias Exactas, Ingeniería y Agrimensura Escuela de Ingeniería Electrónica Digital III Problema de Ingeniería Nº 1 Sistema Mínimo con 80C86 y VHDL Autor/es: Grupo Nº Nombre y Apellido Corrigió Marzo / 2015 Nº de Legajo Calificación Universidad Nacional de Rosario Facultad de Ciencias Exactas, Ingeniería y Agrimensura Escuela de Ingeniería Electrónica 1. Índice 1. Índice....................................................................................................................2 2. Introducción..........................................................................................................2 3. Objetivos..............................................................................................................2 4. Problema de Hardware.........................................................................................3 5. Requisitos del Informe.........................................................................................5 6. Solución /es propuesta / s......................................................................................5 7. Conclusiones.........................................................................................................5 8. Bibliografía............................................................................................................5 9. ANEXO I: Mapas de Memoria.............................................................................6 2. Introducción El presente Problema de Ingeniería aborda las primeras etapas del diseño de hardware de un sistema de microcómputo, es decir, las conexiones entre los componentes principales del sistema: microprocesador, memoria, unidades de entrada salida y los circuitos auxiliares necesarios para que el sistema sea funcional. El problema se plantea en base a un microprocesador 80C86-2 de Intel abordando los aspectos lógicos del sistema implementado. 3. Objetivos El objetivo principal de este problema es lograr que el alumno adquiera la capacidad de describir el hardware de un sistema de microcómputo, como así también que logre versatilidad en la elección, utilización y crítica de diversas herramientas destinadas a resolver el problema (Bibliografía, Hojas de datos, Información disponible en Internet, consultas, etc.) Página 2 de 6 Universidad Nacional de Rosario Facultad de Ciencias Exactas, Ingeniería y Agrimensura Escuela de Ingeniería Electrónica 4. Problema de Hardware 1. Describir en VHDL el circuito de reloj necesario para el microprocesador 80C86-2 (8 MHz) suponiendo un reloj externo de 25 MHz con ciclo de trabajo del 50%. Realizar la simulación de funcionamiento. 2. Describir en VHDL el circuito de acerrojado de direcciones y estados. Realizar la simulación de funcionamiento. 3. Describir en VHDL el circuito de selección del mapa de memoria detallado en el anexo 1. Las paginas de memoria “visibles” deben ser seleccionables en tiempo de ejecución mediante la escritura en un latch mapeado en el espacio de entrada / salida (Registro de Selección de Paginas). Realizar la simulación de funcionamiento. 4. Describir en VHDL un circuito Controlador de Interrupciones (CTRL_IRQ.vhd) de 8 entradas de pedido de interrupción (IRQ[0] – IRQ[7] ), con la posibilidad de enmascarlas individualmente y que al ser procesada, produzcan un tipo correlativo. Caracteristicas: ▪ Entradas: IRQ[0] – IRQ[7] : Entradas de Interrupciones Activas por Nivel Alto – Generacion asincronica Tipo Asignado según: IRQ[n] → IRQ_TIPO + n ▪ Interfase al Microprocesador: CLK: Reloj Principal IRQR: IRQ Request compatible con microprocesador IRQA: IRQ Acknowledge compatible con microprocesador D0-D7: Bus de datos - I/O Tri-state RD: Read – Activo en bajo WR: Write – Activo en bajo CS: Chip Select – Activo en bajo A0: Selector de registro interno ▪ Registros Internos: IRQE: IRQ Enable: Mascara de Interrupciones. El bit de mascara en alto inhibe la atencion de la IRQ correspondiente. Despues del reset, TODAS las interrupciones estaran ENMASCARADAS (IRQE[RESET]: 0xFF). IRQE[n] –> Mascara de Interrupcion para Entrada IRQ[n] , bit n: [0,7] IRQ_TIPO: Permite fijar el tipo base de las interrupciones. Todas las IRQs produciran un tipo correlativo a su respectiva entrada. (desde 0x00 a 0xF7) Página 3 de 6 Universidad Nacional de Rosario Facultad de Ciencias Exactas, Ingeniería y Agrimensura Escuela de Ingeniería Electrónica 5. Implementar los siguientes Testbenchs que permitan verificar el correcto funcionamiento del Controlador de Interrupciones (CTRL_IRQ): a) TEST1_TB Este Tesbench funcionará con todos los pedidos de interrupciones desenmascarados y deberá generar pedidos por dos entradas consecutivas (IRQ[n] e IRQ[n+1], n: [0 , 6] ) de manera SIMULTANEA permitiendo evaluar el correcto funcionamiento del controlador. b) TEST2_TB Este Tesbench funcionará con todos los pedidos de interrupciones desenmascarados y deberá generar pedidos por dos entradas consecutivas (IRQ[n] e IRQ[n+1], n: [0 , 6] ) de manera SIMULTANEA permitiendo evaluar el correcto funcionamiento del controlador. c) (OPCIONAL) Otros testbenchs que puedan resultar de utilidad quedan a voluntad del grupo. 6. Realizar un diagrama general de conexionado de todos los bloques intervinientes junto al microprocesador y los bancos de memoria de manera que sea interpretable por terceros. Los dispositivos que intervienen en el mapa son los siguientes: 2 memorias Flash 29F040 de 512Kb x 8 bits 4 RAM K6T1008 de 128 Kb x 8 bits Página 4 de 6 Universidad Nacional de Rosario Facultad de Ciencias Exactas, Ingeniería y Agrimensura Escuela de Ingeniería Electrónica 5. Requisitos del Informe Mantener el formato de este enunciado en el informe. Entregar las hojas numeradas, y los anexos correspondientes. Todos los cálculos, razonamientos, y justificaciones deben quedar registrados en este informe. Se deberán simular cada uno de los módulos en VHDL y Adjuntar la simulación (Testbenchs y Gráfico de simulación). No es necesario incluir introducciones teóricas En caso de utilizar circuitos o resultados preexistentes, declarar su origen, analizar y contrastar los resultados. Se permite la realización de circuitos o diagramas dibujados a mano, siempre que sean claramente interpretables y estén presentados de forma prolija, acorde a la presentación de un informe de nivel universitario. 6.Solución /es propuesta / s 7.Conclusiones 8.Bibliografía Se sugiere la utilización de la siguiente bibliografía: - Hojas de datos del: 80C86-2, AM29F040, K6T1008. - Los microprocesadores Intel, Barry Brey, Tercera Edicion. Página 5 de 6 Universidad Nacional de Rosario Facultad de Ciencias Exactas, Ingeniería y Agrimensura Escuela de Ingeniería Electrónica 9.ANEXO I: Mapas de Memoria MAPA de MEMORIA Direccion es Tamaño Dispositivos Mapeados (8 bits) 0xFFFFF ... 0x80000 0x7FFFF … 0x40000 0x3FFFF ... 0x00000 512Kb Memoria FLASH Fija 256K de Flash1 y 256K de Flash2 256Kb Memoria RAM Fija 128K de RAM3 y 128K de RAM4 256Kb Memoria paginada 256K de Flash1, 256K de Flash2, 128K de RAM1 y 128K de RAM2 MAPA de Entrada / Salida Direcciones Tamaño Dispositivo 0x0000 1 byte (Espejado) Registro de Paginación Selección de mapa de memoria 0x3FFF 0x4000 0x7FFF 0x8000 Controlador de Interrupciones Dispositivo IO 1 0xBFFF 0xC000 0xFFFF Dispositivo IO 2 Registro de Paginación Bit 7 Bit 6 -- -- Bit 5 Bit 4 Bit 3 Bits de Paginación PAG_2 -PAG_1 Bit 2 Bit 1 Bit 0 -PAG_0 Página 6 de 6