Circuitos Electrónicos. Final de junio curso 2004

Anuncio

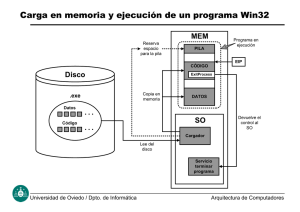

Circuitos Electrónicos. Final de junio curso 2004-2005 Problema 2 (sólo 1º parcial) Se desea diseñar un sistema electrónico que implemente una pila LIFO. Una pila LIFO consiste en un conjunto de registros de almacenamiento en los que se pueden almacenar y recuperar datos de uno en uno. El dato a recuperar siempre es el último introducido. Cuando se recupera un dato, se saca de la pila, y el siguiente a recuperar es el que se introdujo antes de éste. La pila estará compuesta de un conjunto de registros que almacenarán los datos (REG), de un puntero que guardará la dirección del registro donde se guardará el próximo dato que se introduzca (PUNT), de dos comparadores C1 y C2 para el valor de PUNT, de una lógica de direccionamiento que selecciona un registro para obtener su valor (M) o para introducir un valor nuevo (D), y de una máquina de estados que controla el funcionamiento del sistema, como se puede ver en la figura. El sistema tiene como entradas las señales PUSH y POP y los bits del dato a introducir (Di), y como salidas los bits del dato a leer (Do), y las señales de error EMPTY y FULL. Cuando se activa la señal PUSH, se debe introducir un dato en la pila. La máquina de estados debe comprobar que hay sitio en la pila mirando la salida de los comparadores de PUNT. Si hay sitio, debe seleccionar el registro apropiado y activar la señal L, que le dice a los registros que capturen la entrada, y luego incrementar el puntero PUNT con la señal INC. Si no hay sitio, se activa la señal de error FULL, que debe permanecer activa al menos un ciclo de reloj. El funcionamiento es similar cuando se activa la entrada POP. En este caso, se saca un dato de los registros y el puntero se decrementa. Si no había ningún dato, se activa la señal EMPTY. Las señales externas PUSH y POP nunca se dan a la vez, y se supone que se mantienen activas el tiempo suficiente para realizar todas las operaciones. El tamaño de los datos es de 8 bits, y el número de registros en la pila es 16. Todos los subsistemas son SÍNCRONOS y comparten la misma señal de reloj. En todas las cuestiones se pueden usar biestables tipo D (con salida normal y negada), puertas estándar de cualquier tipo con dos entradas, e inversores. Se pide: 1) Diseño de uno de los registros REG, de forma que se pueda colocar en el esquema de la figura. No se admitirán señales externas no previstas en dicho esquema. Obsérvese que hay una sola señal L, común para todos los registros, y 16 señales de salida de D, una para cada registro. (2 puntos) 2) Diseño de los bloques D y M de direccionamiento de registros para que cumplan con las especificaciones dadas. En este apartado se pueden usar bloques MSI. (1 punto) 3) Diseño del registro PUNT. (1 punto) 4) Diseño de la tabla de transiciones de la máquina de estados y de los comparadores C1 y C2, que indicarán a la máquina de estados cuando la pila está llena o vacía. Para la máquina de estados se recomienda considerar sólo las combinaciones de las señales de entrada que tienen sentido y que son relevantes (3 puntos). 5) Dibujo del cronograma a partir de que se activa la señal PUSH. Dibujar todas las señales importantes. Suponer que la pila no está llena. (2 puntos) 6) A partir del cronograma anterior, ¿cuántos ciclos de reloj debe mantenerse activa la señal PUSH para asegurar el correcto funcionamiento del sistema? (1 punto) Tiempo: 1h15min Circuitos Electrónicos. Curso 2004-2005 Solución al problema 2. Final de Junio El problema pedía el diseño de una pila LIFO. Para ello se dispondrá de una serie de registros en los que se almacenarán los datos de la pila, y de una lógica de control externa que lleva la cuenta del número de registros ocupados, y selecciona un registro concreto para extraer o introducir un dato. Lo primero que hay que saber es que si hay 16 registros, el tamaño del puntero que guarda la dirección del primer registro libre debe ser 5 bits. Esto es así porque el rango va de 0 a 16, inclusive, para poder considerar los estados de “pila vacía” y “pila llena”. 1) El primer apartado pide el diseño de cada uno de los registros que componen el conjunto REG, de forma que se pueda cargar un dato cuando se activa la señal L y el registro está seleccionado por D. Un registro de este tipo es un registro de captura normal, con la particularidad de que la captura se produce cuando L y D están activas simultáneamente. El diseño se muestra en la figura. En el enunciado se decía que se podían utilizar puertas de dos entradas, con lo que el multiplexor 2:1 hay que definirlo en función de las puertas que contiene 2) Los bloques D y M se usan para seleccionar un registro concreto para escribir o leer. Puesto que el bloque D tiene como entrada un número de 5 bits que representa el registro al que se quiere escribir, y 16 salidas conectadas a cada uno de los registros, su funcionamiento es el de un decodificador 4:16 al que se conectan los 4 bits menos significativos de PUNT. El bloque M, en cambio, tiene 16 entradas que seleccionan el registro, y 8 salidas que se conectan a las salidas Do. También necesitará leer los contenidos de los registros. Las 16 entradas pueden ser las provenientes del bloque D, ya que ahí está seleccionado el registro que corresponda. Se trata de un conjunto de 8 multiplexores 16:1 (uno para cada bit del dato), que no tienen 4 bits de entrada, sino que la entrada ya está decodificada en las 16 líneas de control. Se puede construir a base de un codificador y 8 multiplexores, o también se puede hacer a base de puertas lógicas: En la figura anterior, REGi_j representa el bit j del registro i-ésimo, y Do_i es el bit de los datos de salida Do. El esquema debe repetirse 8 veces, una para cada bit de los datos. 3) El registro PUNT es un contador ascendente/descendente síncrono de 5 bits. La única particularidad es que si no están activos ni INC ni DEC el contador debe permanecer en reposo. La celda básica tiene la siguiente estructura: Y la forma de encadenar las celdas es la que se muestra en la figura: 4) En este apartado se pide la tabla de transiciones de la máquina de estado que controla la pila, y el diseño de los comparadores C1 y C2. Para hacer la tabla de transiciones sólo vamos a tener en cuenta las entradas posibles, y no todas las combinaciones. El funcionamiento del sistema es el siguiente, según las órdenes de entrada: • Se activa la señal PUSH y la pila no está llena. La máquina activa la señal L (estado 1), para capturar el dato. A continuación desactiva L y activa INC (estado 2). Después vuelve al estado de reposo (estado 0). Como se supone que las entradas están activas el tiempo suficiente, no tenemos que considerar cambios en las entradas durante este proceso. La única señal que ha podido cambiar será C2 (pila llena), ya que la pila ha podido llenarse después del incremento de PUNT, pero eso no nos afecta. • Se activa la señal POP y la pila no está vacía. Como las señales de salida estána activas siempre, no hay que hacer nada con ellas. Lo único que hay que hacer es activar DEC durante un ciclo de reloj y volver al reposo. Igual que antes, si después de activar DEC la pila se vacía no importa. • Se activa PUSH y la pila está llena. Se activa la señal FULL y se mantiene activa hasta que externamente se desactive la señal PUSH. Como no se especificaba, también es correcto activar FULL sólo durante un ciclo de reloj y volver al reposo. • Se activa POP y la pila está vacía. Igual que antes, se activa EMPTY hasta que se desactive la señal POP o durante un ciclo de reloj. Con esta explicación, la tabla de transición de estados queda como: Entradas: PUSH POP C1 C2, Salidas: L EMPTY FULL INC DEC Estado 10x0 010x 0110 1001 0000 Salidas 0 1 4 2 3 (0) 00000 1 5 - - - - 10000 2 - - (2) - - 01000 3 - - - (3) - 00100 4 - 0 - 0 0 00010 5 0 - 0 - 0 00001 Los comparadores C1 y C2 dicen a la máquina de estados cuando la pila está llena y cuándo está vacía. Se trata, por tanto, de comparar el valor de PUNT con 0 y con 16 (no con 15, porque 15 significa que aún queda un sitio libre en la pila). 5) Una vez que se activa PUSH, y siguiendo las indicaciones dadas en el enunciado, debe activarse la señal L para que se capture el dato en Di. Esto se produce, según la tabla de transición de estados del apartado anterior, en 1 ciclo de reloj. Una vez se ha capturado el dato, se pasa al siguiente estado, en el que se desactiva L y se activa INC, también durante un ciclo de reloj. Un ciclo de reloj después el contador se incrementa, y es seguro desactivar la señal PUSH. Todo esto se representa en el cronograma siguiente: 6) Como se puede ver en el cronograma, es necesario mantener la señal de PUSH durante 3 ciclos de reloj. Después del primer ciclo, se activa la señal L, un ciclo después se activa la señal INC, un ciclo más y se incrementa el contador PUNT, y ya se puede desactivar la señal PUSH, ya que la máquina de estados ha vuelto al inicio.