7. Test de circuitos integrados

Anuncio

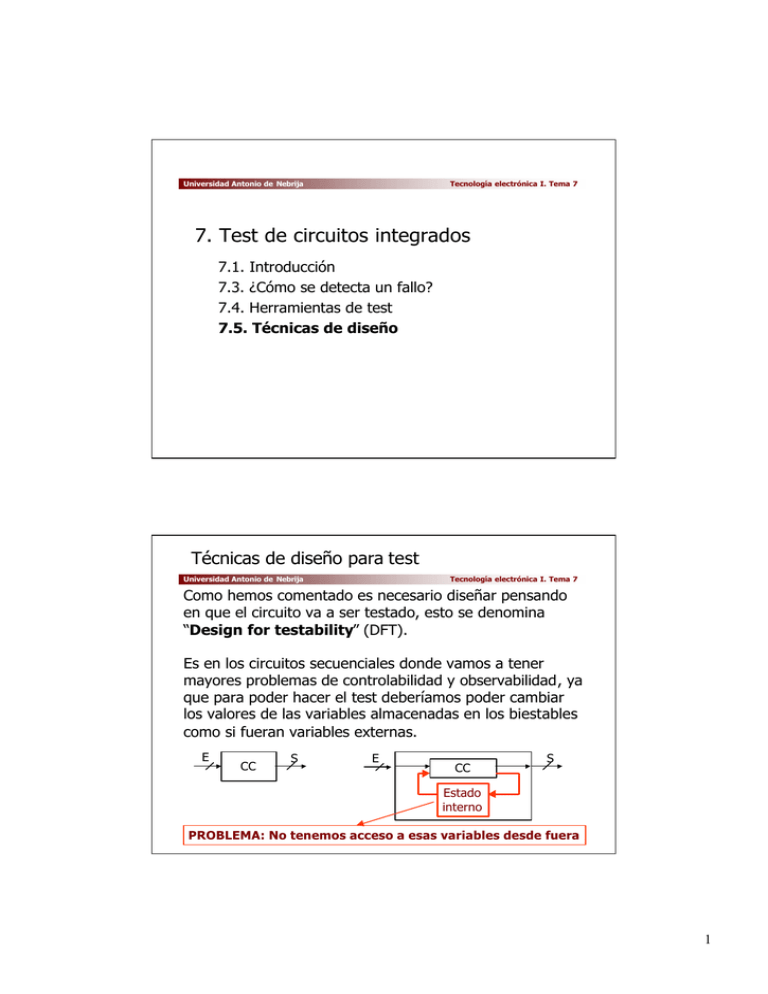

Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 7. Test de circuitos integrados 7.1. Introducción 7.3. ¿Cómo se detecta un fallo? 7.4. Herramientas de test 7.5. Técnicas de diseño Técnicas de diseño para test Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Como hemos comentado es necesario diseñar pensando en que el circuito va a ser testado, esto se denomina “Design for testability” (DFT). Es en los circuitos secuenciales donde vamos a tener mayores problemas de controlabilidad y observabilidad, ya que para poder hacer el test deberíamos poder cambiar los valores de las variables almacenadas en los biestables como si fueran variables externas. E CC S E CC S Estado interno PROBLEMA: No tenemos acceso a esas variables desde fuera 1 Técnicas de diseño para test. Scan Path Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Técnica del Scan Path. Con la señal de test conseguimos que los biestables se comporten como un registro de desplazamiento. Se consigue que el valor de las variables almacenada en los biestables sean “transparentes” y puedan ser variadas a nuestro antojo, para poder así probar nuestros vectores de test. El concepto lo representamos así: E S CC Estado interno 0 1 E’ TEST Técnicas de diseño para test. Scan Path Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Técnica del Scan Path. Ejemplo D Un sistema como: Q D /Q CLEAR E Q D /Q CLEAR Q /Q CLEAR S PUERTAS LÓGICAS Y CONEXIONES Se diseñaría con esta técnica así: IN 1 0 D Q 1 0 D Q 1 0 D Q /Q CLEAR /Q CLEAR /Q CLEAR 0 1 0 1 0 1 TEST RESET E PUERTAS LÓGICAS Y CONEXIONES S 2 Técnicas de diseño para test. Scan Path Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Técnica del Scan Path. Ejemplo Pasamos a tener un estado de test, que lo activamos desde fuera, mediante el cual podemos cambiar el contenido de los biestables, y por tanto el estado interno del sistema, casi como si fueran variables externas. El valor que queremos dar a los biestables lo debemos introducir en serie bit a bit, desde el primer biestable, de forma que se irá propagando de un biestable a otro ya que está funcionando como registro de desplazamiento. Técnicas de diseño para test. Test interno Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Técnica del Test interno ( Built In Self Test). Se quiere realizar un test interno automático de un bloque de un circuito integrado. Se compone de: • Generador interno de vectores de test • Analizador de la respuesta, que genera información que se transmitirán en serie a la máquina de test n 0 GENERADOR DE VECTORES DE TEST CLK 1 n m BLOQUE ANALIZADOR DE LA RESPUESTA m TEST ENABLE SALIDA SERIE CONTROL 3 Técnicas de diseño para test. Test interno Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 El analizador de la respuesta debe calcular la “firma” del bloque y transmitirla en serie hacia fuera. El concepto de firma es: se trata de asociar a cualquier secuencia de p palabras de m bits una palabra de r bits, característica de la secuencia particular en cuestión. Para que sea útil dicha firma debe ocurrir que: • r<<m·p, es decir que la información sea mucho más compacta. • Si dos secuencias s1 y s2 tienen la misma firma debe ocurrir que s1 y s2 sean muy distintas. Por ejemplo: • s1 = 00, 00, 10, 11 • s2 = 11, 00, 11, 01 d(s1 s2) = 4 La característica más importante del generador de firma es la distancia mínima D entre secuencias con la misma firma: Si F(s1) = F(s2) entonces d(s1, s2) ≥ D Técnicas de diseño para test. Test interno Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Si el generador de firmas tiene una distancia mínima D, cualquier error que afecte a menos de D bits será detectado. Por ejemplo: generador de paridad, tiene una distancia D = 2, por lo que detecta los errores de un solo bit. RESET IN 1 IN 2 IN m CLEAR D CLK Q OUT /Q 4 Técnicas de diseño para test. Test interno Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Generadores de firma más sofisticados: Registros de desplazamiento con realimentaciones lineales, LFSR (Linear Feedback Shift Register). RESET IN m RESET IN m CLK RESET CLEAR CLEAR CLEAR D D D Q CLK /Q RESET IN m IN m Q CLK /Q CLEAR Q /Q D CLK Q OUT /Q Técnicas de diseño para test. Bloques Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Descomposición en bloques. Para diseñar un circuito fácil de testear se puede descomponer en bloques. e1 e2 en E s1 B1 s2 B2 B1 sn CONEXIONES S 5 Técnicas de diseño para test. Bloques Universidad Antonio de Nebrija Tecnología electrónica I. Tema 7 Descomposición en bloques. Si cada bloque es comprobable. El problema se reduce a n problemas de menor complejidad. TEST 1 e1 0 s1 B1 1 2 e2 0 n 0 E s2 B2 2 S en B1 sn n 0 CONEXIONES 6