AMPLIFICADOR OPERACIONAL IDEAL Circuito Integrado

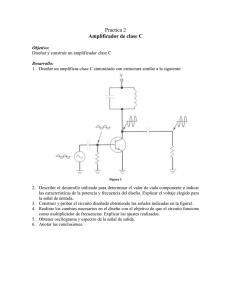

Anuncio

UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA AMPLIFICADOR OPERACIONAL IDEAL Circuito Integrado Analógico de uso universal (no de aplicación específica) . Se emplea como bloque funcional para facilitar el diseño de circuitos electrónicos analógicos. Un amplificador operacional (A.O., habitualmente llamado op-amp) es un circuito electrónico (normalmente se presenta como circuito integrado) que tiene dos entradas y una salida. La salida es la diferencia de las dos entradas multiplicada por un factor (G) (ganancia): Vout = G·(V+ − V−) El primer amplificador operacional monolítico data de los años 1960, era el Fairchild μA702 (1964), diseñado por Bob Widlar. Le siguió el Fairchild μA709 (1965), también de Widlar, y que constituyó un gran éxito comercial. Más tarde sería sustituido por el popular Fairchild μA741 (1968), de David Fullagar, y fabricado por numerosas empresas, basado en tecnología bipolar. Originalmente los A.O. se empleaban para operaciones matemáticas (suma, resta, multiplicación, división, integración, derivación, etc) en calculadoras analógicas. De ahí su nombre. El A.O. ideal tiene una ganancia infinita, una impedancia de entrada infinita, un ancho de banda también infinito, una impedancia de salida nula, un tiempo de respuesta nulo y ningún ruido. Como la impedancia de entrada es infinita también se dice que las corrientes de entrada son cero. El símbolo de un MONOLITICO es el mostrado en la siguiente figura: Figura 1.3. Amplificador operacional ideal Los terminales son: • • • • • V +: entrada no inversora V -: entrada inversora V OUT: salida V S+: alimentación positiva V S-: alimentación negativa UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Las terminales de alimentación pueden recibir diferentes nombres, por ejemplo en los A.O. basados en FET VDD y VSS respectivamente. Para los basados en BJT son VCC y VEE. Normalmente los pines de alimentación son omitidos en los diagramas eléctricos por claridad. COMPORTAMIENTO EN CONTINUA (DC) Lazo abierto Si no existe realimentación la salida del A.O. será la resta de sus dos entradas multiplicada por un factor. Este factor suele ser del orden de 100.000 (que se considerará infinito en cálculos con el componente ideal). Por lo tanto si la diferencia entre las dos tensiones es de 1V la salida debería ser 100.000V. Debido a la limitación que supone no poder entregar más tensión de la que hay en la alimentación, el A.O. estará saturado si se da este caso. Si la tensión más alta es la aplicada a la patilla + la salida será la que corresponde a la alimentación V S+, mientras que si la tensión más alta es la del pin - la salida será la alimentación VS-. Lazo cerrado Se conoce como lazo a la realimentación en un circuito. Aquí se supondrá realimentación negativa. Para conocer el funcionamiento de esta configuración se parte de las tensiones en las dos entradas exactamente iguales, se supone que la tensión en la patilla + sube y, por tanto, la tensión en la salida también se eleva. Como existe la realimentación entre la salida y la patilla -, la tensión en esta patilla también se eleva, por tanto la diferencia entre las dos entradas se reduce, disminuyéndose también la salida. Este proceso pronto se estabiliza, y se tiene que la salida es la necesaria para mantener las dos entradas, idealmente, con el mismo valor. Siempre que hay realimentación negativa se aplican estas dos aproximaciones para analizar el circuito: • • V + = VI+ = I- = 0 COMPORTAMIENTO EN ALTERNA (AC) En principio la ganancia calculada para continua puede ser aplicada para alterna, pero a partir de ciertas frecuencias aparecen limitaciones. (Ver sección de limitaciones) Un ejemplo de amplificador operacional es el 741op Análisis UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Para analizar un circuito en el que haya A.O. puede usarse cualquier método, pero uno habitual es: 1. Comprobar si tiene realimentación negativa 2. Si tiene realimentación negativa se pueden aplicar las reglas del apartado anterior 3. Definir las corrientes en cada una de las ramas del circuito 4. Aplicar el método de los nodos en todos los nodos del circuito excepto en los de salida de los amplificadores (porque en principio no se puede saber la corriente que sale de ellos) 5. Aplicando las reglas del apartado 2 resolver las ecuaciones para despejar la tensión en los nodos donde no se conozca. CONFIGURACIONES Comparador Figura 1.4. Amplificador comparador • Esta es una aplicación sin la realimentación. Compara entre las dos entradas y saca una salida en función de qué entrada sea mayor. Se puede usar para adaptar niveles lógicos. • Seguidor • Es aquel circuito que proporciona a la salida la misma tensión que a la entrada Figura 1.5. Amplificador seguidor • • • Se usa como un buffer, para eliminar efectos de carga o para adaptar impedancias (conectar un dispositivo con gran impedancia a otro con baja impedancia y viceversa) Como la tensión en las dos patillas de entradas es igual: V out = Vin Z in = ∞ UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Inversor Figura 1.6. Amplificador inversor Se denomina inversor ya que la señal de salida es igual a la señal de entrada (en forma) pero con la fase invertida 180 grados. • El análisis de este circuito es el siguiente: o V + = V- = 0 o Definiendo corrientes: y de aquí se despeja o • • Para el resto de circuitos el análisis es similar. Z in = Rin Por lo cual podemos controlar la impedancia de entrada mediante la elección de R1 • Esta configuración es una de las más importantes, porque gracias a esta configuración, se puede elaborar otras configuraciones, como la configuración del derivador, integrador, sumador. No inversor Figura 1.7. Amplificador No inversor Como observamos, el voltaje de entrada, ingresa por el pin positivo, pero como conocemos que la ganancia del amplificador operacional es muy grande, el voltaje en el pin positivo es igual al voltaje en el pin negativo, conociendo el voltaje en el pin negativo podemos calcular, la relación que existe entre el voltaje de salida con el voltaje de entrada haciendo uso de un pequeño divisor de tensión. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA • • Zin = ∞ Sumador inversor Figura 1.8. Sumador inversor • • La salida está invertida Para resistencias independientes R 1, R2,... Rn • La expresión se simplifica bastante si se usan resistencias del mismo valor Impedancias de entrada: Z n = Rn • o Restador Figura 1.9. Restador • Para resistencias independientes R 1,R2,R3,R4: • Igual que antes esta expresión puede simplificarse con resistencias iguales La impedancia diferencial entre dos entradas es Z in = R1 + R2 • o UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Integrador ideal Figura 1.10. Integrador ideal • Integra e invierte la señal (V in y Vout son funciones dependientes del tiempo) • o V inicial es la tensión de salida en el origen de tiempos Nota: El integrador no se usa en la práctica de forma discreta ya que cualquier señal pequeña de DC en la entrada puede ser acumulada en el capacitor hasta saturarlo por completo. Este circuito se usa de forma combinada en sistemas retroalimentados que son modelos basados en variables de estado (valores que definen el estado actual del sistema) donde el integrador conserva una variable de estado en el voltaje de su capacitor. Derivador ideal Figura 1.11. Derivador ideal • Deriva e invierte la señal respecto al tiempo • • Este circuito también se usa como filtro NOTA: Es un circuito que no se utiliza en la práctica porque no es estable, esto se debe a que al amplificar más las señales de alta frecuencia se termina amplificando el ruido por mucho. Otros • Osciladores, como el puente de Wien UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA • • • • Convertidores carga-tensión Convertidores corriente-tensión Filtros activos Girador permite construir convertidores de inmitancias (empleando un condensador simular un inductor, por ejemplo) APLICACIONES • • • • • • • Calculadoras analógicas Filtros Preamplificadores y buffers de audio y video Reguladores Conversores Evitar el efecto de carga Adaptadores de niveles (por ejemplo CMOS y TTL) ESTRUCTURA Aunque es usual presentar al A.O. como una caja negra con características ideales es importante entender la forma en que funciona, de esta forma se podrá entender mejor las limitaciones que presenta. Los diseños varían entre cada fabricante y cada producto, pero todos los A.O. tienen básicamente la misma estructura interna, que consiste en tres etapas: 1. Amplificador diferencial: es la etapa de entrada que proporciona una baja amplificación del ruido y gran impedancia de entrada. Suelen tener una salida diferencial. 2. Amplificador de tensión: proporciona una ganancia de tensión. 3. Amplificador de salida: proporciona la capacidad de suministrar la corriente necesaria, tiene una baja impedancia de salida y, usualmente, protección frente a cortocircuitos. Ejemplo del 741 UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Figura 1.12. Diagrama electrónico del operacional 741. En el diagrama se destaca en azul el amplificador diferencial. Éste es el responsable de que las corrientes de entrada no sean cero, pero si respecto a las de los colectores (Nótese como a pesar de aproximar las corrientes de entrada a 0, si éstas realmente fueran 0 el circuito no funcionaría). La impedancia de entrada es de unos 2MΩ. Las etapas en rojo son espejos de corriente. El superior de la izquierda sirve para poder soportar grandes tensiones en modo común en la entrada. El superior de la derecha proporciona una corriente a la circuitería de salida para mantener la tensión. El inferior tiene una baja corriente de colector debido a las resistencias de 5kΩ. Se usa como conexión de gran impedancia a la alimentación negativa para poder tener una tensión de referencia sin que haya efecto de carga en el circuito de entrada. Los pines llamados Offset null son usados para eliminar las tensiones de offset que pueda haber en el circuito. La etapa de ganancia en tensión es NPN. La sección verde es un desplazador de tensión. Esto proporciona una caída de tensión constante sin importar la alimentación. En el ejemplo 1V. Esto sirve para prevenir la distorsión. El condensador se usa como parte de un filtro paso bajo para reducir la frecuencia y prevenir que el A.O oscile. La salida en celeste es un amplificador PNP seguidor con emisor push-pull. El rango de la tensión de salida es de un voltio menos a la alimentación, la tensión colector-emisor de los transistores de salida nunca puede ser totalmente cero. Las resistencias de salida hacen que la corriente de salida esté limitada a unos 25mA. La resistencia de salida no es cero, pero con realimentación negativa se aproxima. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA PARÁMETROS • • • • • • • • Ganancia en lazo abierto. Indica la ganancia de tensión en ausencia de realimentación. Se puede expresar en unidades naturales (V/V, V/mV) o logarítmicas (dB). Son valores habituales 100.000 a 1.000.000 V/V. Tensión en modo común. Es el valor medio de tensión aplicado a ambas entradas del operacional. Tensión de Offset. Es la diferencia de tensión, aplicada a través de resistencias iguales, entre las entradas de un operacional que hace que su salida tome el valor cero. Corriente de Offset. Es la diferencia de corriente entre las dos entradas del operacional que hace que su salida tome el valor cero. Margen de entrada diferencial. Es la mayor diferencia de tensión entre las entradas del operacional que mantienen el dispositivo dentro de las especificaciones. Corrientes de polarización (Bias) de entrada. Corriente media que circula por las entradas del operacional en ausencia de señal Slew rate. Es la relación entre la variación de la tensión de salida máxima respecto de la variación del tiempo. Se mide en V/ μs, kV/μs o similares. Relación de Rechazo en Modo Común (RRMC,o CMRR en sus siglas en inglés). Relación entre la ganancia en modo diferencial y la ganancia en modo común. LIMITACIONES Saturación Un A.O.L típico no puede suministrar más de la tensión a la que se alimenta, normalmente algunos voltios menos. Cuando se da este valor se dice que satura, pues ya no está amplificando. La saturación puede ser aprovechada por ejemplo en circuitos comparadores. Un concepto asociado a éste es el Slew rate(analisis básico de bajo flujo recoltor). Tensión de offset Es la diferencia de tensión que se obtiene entre los dos pines de entrada cuando la tensión de salida es nula, este votltaje es cero en un amplificador ideal lo cual no se obtiene en un amplificador real. Esta tensión puede ajustarse a cero por medio del uso de las entradas de offset (solo en algunos modelos de operacionales) en caso de querer precisión. El offset puede variar dependiendo de la temperatura (T) del operacional como sigue: UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Donde T 0 es una temperatura de referencia. Un parámetro importante, a la hora de calcular las contribuciones a la tension de offset en la entrada de un operacional es el CMRR (Rechazo al modo común). Ahora también puede variar dependiendo de la alimentación del operacional, a esto se le llama PSRR (power supply rejection ratio, relación de rechazo a la fuente de alimentación). La PSRR es la variación del voltaje de offset respecto a la variación de los voltajes de alimentación,expresada en dB. Se calcula como sigue: Corrientes Aquí hay dos tipos de corrientes que considerar y que los fabricantes suelen proporcionar: • IOFFSET = | I + −I − | • Idealmente ambas deberían ser cero. Característica tensión-frecuencia Al A.O. típico también se le conoce como amplificador realimentado en tensión (VFA). En él hay una importante limitación respecto a la frecuencia: El producto de la ganancia en tensión por el ancho de banda es constante. Como la ganancia en lazo abierto es del orden de 100.000 un amplificador con esta configuración sólo tendría un ancho de banda de unos pocos Hercios. Al realimentar negativamente se baja la ganancia a valores del orden de 10 a cambio de tener un ancho de banda aceptable. Existen modelos de diferentes A.O. para trabajar en frecuencias superiores, en estos amplificadores prima mantener las características a frecuencias más altas que el resto, sacrificando a cambio un menor valor de ganancia u otro aspecto técnico. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Capacidades El A.O. presenta capacidades (capacitancias) parásitas, las cuales producen una disminución de la ganancia conforme se aumenta la frecuencia. Deriva térmica Debido a que una unión semiconductora varía su comportamiento con la temperatura, los A.O. también cambian sus características, en este caso hay que diferenciar el tipo de transistor en el que está basado, así las corrientes anteriores variarán de forma diferente con la temperatura si son bipolares o JFET. Espejo de corriente Figura 1.13. Espejo de corriente. En electrónica, un espejo de corriente es una configuración con la que se pretende obtener una corriente constante, esto es, una fuente de corriente. Esta configuración consta de dos transistores, idealmente idénticos, y una resistencia o potenciómetro, si se quisiera regular el circuito en el caso que los transistores no fueran idénticos. En la figura 1.13 se muestra el esquema básico de un espejo de corriente. La Intensidad que circula en R1 está dada por: IR1 = IC1 + IB1 + IB2 Donde IC1 es la intensidad del colector de Q1, IB1 es la intensidad de base de Q1, IB2 es la intensidad de base de Q2. La intensidad de colector de Q1 viene dada por la ecuación: UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA IC1 = 0IB1 Donde β0 es la ganancia de intensidad de idealmente idénticos, la β de Q2 será: Q1. Si Q1 y Q2 son donde VA es debida al efecto Early. Desde que VBE1 = VBE2 y Q1 y Q2 son idénticos, IB1 = IB2. La intensidad de colector de Q2 será entonces dado por: Si β0 > entonces: > 1, Se obtiene así una precisión superior a la obtenida con circuitos más complejos, como los Widlar, de Wilson o Cascodo. El espejo de corriente se usa en los circuitos integrados porque es una forma conveniente de crear fuentes de corriente y cargas activas. La ventaja de utilizar espejos de corriente es la del incremento en la ganancia de tensión y en el rechazo al modo común (CMRR). Figura 1.14. Espejo de corriente implementado con transistores bipolares tipo NPN usando una resistencia para fijar la intensidad de referencia I REF ; V CC = Tensión de entrada UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA REGLAS DE DISEÑO INTRODUCCIÓN La MICROELECTRÓNICA se puede definir como el conjunto de ciencias y técnicas con las que se realizan y fabrican circuitos electrónicos sobre una pastilla de un semiconductor, lo cual formará un circuito integrado (CI). Dentro de estos circuitos integrados, podemos encontrar diferentes estrategias de diseño, como pueden ser los circuitos integrados en los que se deben construir tanto las puertas como las conexiones, denominados habitualmente ASICs (Application Specific Integrated Circuits), circuitos programables en los que se encuentran ya construidos todas las puertas y conexiones de tal forma que únicamente hay que indicar cuales están habilitadas mediante una programación, denominados dispositivos programables (un ejemplo de los cuales pueden ser las FPGAs, (Field Programmbled Gate Arrays). La división existente en los circuitos electrónicos también es válida para la Microelectrónica, es decir, podemos diferenciar entre Microelectrónica Analógica y Digital, según la naturaleza de las señales tratadas. No obstante, el auge de la Microelectrónica surgió gracias a una propiedad de los sistemas digitales: la jerarquía. La propiedad de jerarquía es aquella por la cual un sistema puede estar compuesto de bloques conectados entre sí, de tal forma que dichos bloques son independientes entre sí y de su conexión. A pesar de que un circuito analógico también puede ser construido por una serie de bloques conectados entre sí; estos bloques no serán independientes de su conexión (e incluso su situación en la base del semiconductor) debido a la naturaleza real de las señales analógicas (pueden tener un rango infinito de valores). En cambio, el carácter digital de las señales de los sistemas digitales provee dicha independencia y así la posibilidad de desarrollar un sistema completamente jerárquico. A modo de ejemplo, podemos ver en la figura 1.15 dos ASICs: el caso (a) sería un diseño analógico; y el caso (b) sería un diseño digital. En el caso analógico podemos ver unas estructuras formadas por los mismos bloques dispuestas de una manera especial (parecida a una circunferencia). Bien, esta disposición no es aleatoria sino que debe ser así para garantizar el mismo comportamiento en todos los bloques. En cambio, en el circuito digital podemos apreciar bloques comunes, cuya disposición obedece únicamente a con- tribuir a que el sistema completo sea lo más compacto posible. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA En la figura podemos apreciar una clasificación de los sistemas digitales desde un punto de vista jerárquico. Según dicho esquema los sistemas digitales se pueden representar desde bloques de muy alto nivel, como pueden ser procesadores y/o memorias, hasta un circuito integrado, el chip. Normalmente en el campo digital se suele utilizar un proceso de diseño topdown, en el cual partimos de las especificaciones de más alto nivel, y llegamos al circuito integrado pasando por todos los niveles de jerarquía. Dentro de este proceso podemos distinguir dos fases bien diferenciadas. (a) (b) Figura 1.15. Ejemplos de diseños microelectrónicos (a) analógicos y (b) digitales. En la primera fase se obtiene el circuito lógico a partir de descripciones de alto nivel. El resultado de esta fase será un diagrama o una descripción de en un HDL (Lenguaje de Descripción de Hardware) con las conexiones de puertas, registros, etc., es decir, bloques abstractos en función del nivel en el que nos encontremos. En la segunda fase, se construirán los bloques mencionados anteriormente según una familia lógica, de tal forma que están completamente determinados el tamaño, la forma y la estructura interna de cada uno de los bloques. En esta fase, el diseñador debe obtener los diferentes esquemas a nivel de transistores (moviéndonos en el nivel eléctrico); y a partir del cual se obtendrá el layout del circuito (moviéndonos en el nivel geométrico). El layout se puede definir como una representación física de un circuito electrónico que está sujeto a limitaciones derivadas del proceso de integración, el flujo de diseño y requerimientos de prestaciones. Una vez que tenemos un layout correcto, se pasa a la foundry (que es la fábrica UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA encargada de obtener el circuito físico) para que lleve a cabo todos los procesos de integración. La corrección del layout se debe llevar a cabo en un doble sentido: • Una verificación funcional, en la cual ha de verificarse que las capas incluidas en el layout, así como su distribución, sean equivalentes al esquema eléctrico de partida. Dicha verificación se suele conocer como LVS (Layout Versus Schematic) • Una verificación geométrica, en la cual ha de verificarse que las capas de un determinado material están lo suficientemente separadas como para que, al finalizar el proceso de integración, dichas capas estén realmente separadas. Dicha verificación se suele conocer como DRC (Design Rules Checking). Esta verificación es lo suficientemente importante como para que la foundry vuelva a realizarla para evitar fallos. Por lo tanto nos vamos a centrar en los niveles eléctricos y geométricos, por ser aquellos en los que la acción del diseñador es importante. Figura 1.16.Clasificación jerárquica de los sistemas digitales. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA PROCESOS DE DISEÑO La fabricación de un circuito integrado consiste de una serie de pasos en un orden específico. El material base de los circuitos integrados es una oblea o disco de semiconductor. La tecnología más desarrollada es la basada en silicio (Si), aunque también existen tecnologías a base de otros semiconductores como arseniuro de galio (GaAs) o germanio y silicio (SiGe). No obstante, todas las tecnologías siguen unos pasos similares. El semiconductor no está en equilibrio eléctricamente, sino que unas cantidades controladas de impurezas son añadidas para dotar al cristal de las propiedades eléctricas requeridas. Dichas impurezas pueden ser donadores (cargados eléctricamente con signo negativo), que se corresponden al tipo n; o aceptoras (cargadas eléctricamente con signo positivo), que corresponden al tipo p. En función del tipo de estas impurezas podemos encontrarnos con diferentes tipos de procesos: • Procesos de n-well (utilizado principalmente en Europa) en el que el dopado de la oblea es de tipo p. • Procesos de p-well (utilizado principalmente en Estados Unidos) en el que el dopado de la oblea es de tipo n. • Procesos de well gemelos (el cual se está extendiendo cada vez más) en el que el signo del dopado de la oblea no tiene demasiada importancia ya que se van a generar los dos tipos de well (n-well y p-well). Como los tres tipos de procesos son similares, nos vamos a centrar en uno de ellos, en particular en el proceso de n-well. Dicho proceso se muestra en la figura 1.17, más concretamente la oblea sería el paso (a). La primera máscara define el n-well (figura 1.17b). Esta zona, el n-well, es el lugar en el que se van a implementar los transistores PMOS. En esta etapa también se depositan capas de óxido grueso (denominado de campo), SiO2, para separar cada una de las regiones (figura 1.17c). La siguiente capa que se deposita es la llamada óxido de puerta (o fino), la cual se obtendrá por el crecimiento de las zonas de óxido de campo (figura 1.17d). Dicha capa constituirá con el polisilicio el terminal de puerta de los transistores. Una vez que se ha depositado el óxido de puerta, se coloca el polisilicio (figura 1.17e) y se despeja el resto de óxido de puerta para permitir la creación de los terminales de fuente y drenador (figura 1.17f). El siguiente paso es difundir los terminales de fuente y drenador de los transistores NMOS (figura 1.17g), y seguidamente los terminales correspondientes a los transistores PMOS (figura 1.17h). También se crean los contactos con las zonas de polarización: regiones n+ sobre el n-well, y regiones UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA p+ sobre el resto del CI. Una vez creadas las diferentes regiones n+ y p+, se pasa a la inserción de la primera capa de metal (figura 1.17i). El contacto físico de este material (por lo general aluminio, aunque se está probando con cobre en los últimos tiempos) con el polisilicio y las zonas de difusión provocará un contacto eléctrico. No obstante hay que indicar que aquellas zonas en las que no se requiere contacto, habían sido ocupadas con óxido de campo evitando de esta forma el contacto. Figura 1.17. Pasos del proceso de fabricación de un circuito CMOS con el proceso de nwell. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Para la segunda (y restantes capas) capa de metal (figura 1.17j) se coloca una nueva capa de óxido de campo por todo el CI excepto en los lugares donde exista un contacto entre la capa actual y la anterior. Después se deposita la capa de metal en los lugares correspondientes. Cabe destacar que el material de todas las capas de metal existentes, en la tecnología utilizada, es el mismo, es decir, aluminio (o cobre). En todos estos pasos podemos distinguir dos tipos de acciones: crear zonas de difusión y de well, que alterará la composición interna de la oblea; y la deposición de material sobre la oblea. La primera acción se puede conseguir a través de dos proceso diferentes: difusión e implantación iónica. • El proceso de difusión consiste en depositar sobre la oblea un material desde el cual obtener las impurezas deseadas y calentarla oblea a una temperatura elevada. De esta forma, los espacios intersticiales del semiconductor aumentan, y así las impurezas pueden ocupar estos espacios. • El proceso de implantación iónica consiste en bombardear la oblea con las impurezas que se quieren difundir. Dicha difusión sólo se producirá en las zonas que no se encuentren protegidas por una máscara de material. En cuanto a la segunda acción, el proceso más utilizado es la fotolitografía. Dicha técnica consiste en depositar por todo el circuito una capa de material en cuestión (polisilicio o metal, también se utiliza con el óxido para separar las diferentes capas, pero dicho proceso es transparente para el diseñador, la única acción del diseñador en esta capa son los contactos en los que no debe haber dicha capa de óxido), y encima de ella una máscara fotorresistiva, la cual evitará la pérdida del material que se encuentre bajo ella. Después de haber eliminado el material sobrante del circuito, se elimina la máscara dejando el circuito preparado para una nueva capa. Por lo tanto, para cualquiera de los procesos anteriores, es necesario conocer y verificar una serie de características geométricas como son el tamaño del material depositado sobre el circuito. Dichas características son denominadas reglas de diseño, y gracias a ellas se asegura que los dispositivos descritos en el layout estarán en el circuito físico. Si algunas de estas reglas son violadas no se asegura la correcta creación del circuito electrónico. A modo de ejemplo veamos una porción de un fichero de reglas de diseño para una tecnología CMOS estándar de 0.12 µm en la figura 1.18. En él podemos ver las diferentes capas con las reglas geométricas correspondientes a cada una de ellas. Es interesante notar que las dimensiones están referenciadas a un parámetro, lambda, para que la portabilidad de dichas reglas a otras tecnologías sea más sencilla. En dicho fichero, que lo utiliza la herramienta Microwind, podemos distinguir tres partes en cada línea: la referencia de la regla, la UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA dimensión mínima que se ha de verificar (en términos de lambda) y un breve comentario sobre dicha regla. También se suele adjuntar un esquema en el que se muestran de forma gráfica las diferentes reglas. En este caso particular únicamente se muestran las reglas del nwell, áreas activas o difusiones y del polisilicio. NAME CMOS 0.12µm - 6 Metal * lambda = 0.06 (Lambda is set to half the gate size) * * Design rules associated to each layer * * Well * r101 = 10 (well width) r102 = 11 (well spacing) * * Diffusion * r201 = 4 (diffusion width) r202 = 4 (diffusion spacing) r203 = 6 (border of nwell on diffp) r204 = 6 (nwell to next diffn) r205 = 0 (diffn to diffp) * * Poly * r301 = 2 (poly width) r302 = 2 (gate length) r303 = 4 (high voltage gate length) r304 = 3 (poly spacing) r305 = 1 (spacing poly and unrelated diff) r306 = 4 (width of drain and source diff) r307 = 3 * * Poly 2 * r311 = 2 r312 = 2 * * Contact r401 = 2 r402 = 4 r403 = 1 r404 = 1 r405 = 1 r406 = 2 r407 = 1 * * metal r501 = 3 r502 = 4 r510 = 16 * via r601 = 2 r602 = 4 r604 = 1 r605 = 1 * metal 2 r701 = 3 r702 = 4 r710 = 16 (extra gate poly) (poly2 width) (poly2 spacing) (contact width) (contact spacing) (metal border for contact) (poly border for contact) (diff border for contact) (contact to gate) (poly2 border for contact) (metal width) (metal spacing) (minimum surface) (Via width) (Spacing) (border of metal) (border of metal2) (Metal 2 width) (minimum surface) UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Figura 1.18. Reglas de diseño de un proceso CMOS en tecnología de 0.12 µm. TÉCNICAS DE DISEÑO MICROELECTRÓNICO De forma previa a la creación de un layout, debemos conocer la estructura a nivel de transistores del circuito, para lo cual debemos descender al nivel de jerarquía eléctrico. Las técnicas de diseño no son más que unos procedimientos para desplazarnos a través de los diferentes niveles de jerarquía del circuito. En función del sentido del movimiento tenemos flujos top-down, que van desde el nivel superior al inferior, y flujos bottom-up, que van del nivel inferior al superior. El flujo de diseño top-down parte de una descripción global del sistema (sin precisar las diferentes partes que lo forman ni especificaciones cuantitativas); para a partir de dicha descripción ir refinando cada vez más las diferentes partes. El flujo de diseño bottom-up parte de unas especificaciones muy detalladas para realizar las diferentes partes del sistema, las cuales serán conectadas entre sí con posterioridad. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA En el caso de diseño, el flujo más utilizado es el top-down, ya que cuando la descripción es compleja las especificaciones detalladas son muy difíciles de cumplir; por lo tanto, nos centraremos en el primero. En la figura 1.19 se muestra el procesos en el flujo de diseño top-down. Figura 1.19. Procesos en el flujo de diseño top-down. El flujo de diseño tratará de pasar desde el nivel superior del dominio de comportamiento al nivel inferior del dominio físico pasando por el dominio estructural. Veremos todo este paso con el ejemplo de un multiplicador, mostrado en la figura 1.20. El nivel superior estará compuesto por algoritmos (en su dominio de comportamiento) o por procesadores, memorias y/o buses (en su dominio estructural). En nuestro caso particular necesitaremos un procesador dedicado y un controlador (que no sería más que otro procesador dedicado); mientras que el dominio de comportamiento estaría descrito por cualquiera de los algoritmos de multiplicación disponibles, por ejemplo la multiplicación por sumas sucesivas. Obviamente, el punto de partida sería el algoritmo, ya que el conjunto procesador-controlador no nos suministra la suficiente información para continuar. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA En el siguiente nivel, el comportamiento estaría descrito por un diagrama ASM en el cual estarían descritas todas las operaciones así como la secuencia en la que se han de realizar dichas operaciones. En dicho nivel se tiene la información suficiente para que la descripción estructural sea lo suficientemente precisa para que tenga un sentido lógico. Por lo tanto, en este nivel se suele realizar el proceso de síntesis. El proceso de síntesis se puede definir como el proceso por el cual se pasa del dominio de comportamiento al estructural siguiendo una serie de restricciones. En la figura 1.20 sólo mostramos el esquema correspondiente al procesador. De hecho, para no saturar la figura, sólo se ha considerado una celda para descender de nivel en la jerarquía. Una vez que tenemos los elementos de procesado del nivel RTL, debemos implementarlo con puertas lógicas y biestables. El comportamiento de este nivel estaría descrito a partir de ecuaciones lógicas (booleanas) y diagramas de estado; no obstante, la complejidad (en cuanto al número de componentes) de este nivel es lo suficientemente grande como para que el sistema de estas ecuaciones sea intratable. Como ejemplo mostramos como estaría formado el registro acumulador con las condiciones de habilitación y reset síncrono. En el siguiente nivel se obtendrá la estructura eléctrica de los componentes lógicos: puertas y biestables; para ello, se elegirá la familia lógica que mejor se adapte a las especificaciones. En el ejemplo se ha considerado una familia lógica CMOS estática. Por último, se debe pasar de este esquema a nivel de transistores al layout en el cual se indicarán las capas que se necesitan así como su forma y tamaño. UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Algoritmos Procesador G U/D L CNT Diagrama ASM D R G Ecuaciones lógicas y ecuaciones de estado Controlador R G D + Q D0 REG Q Dn DQ DQ Q0 Ecuaciones eléctricas Ecuaciones de campo eléctrico Figura 1.20. Diferentes pasos del flujo de diseño top-down Qn UNIVERSIDAD NACIONAL ABIERTA Y A DISTANCIA – UNAD ESCUELA DE CIENCIAS BÁSICAS, TECNOLOGÍA E INGENIERÍA CONTENIDO DIDÁCTICO DEL CUSO: 299008 – MICROELECTRÓNICA Un flujo de diseño ampliamente utilizado es el mostrado en la figura 1.21. En él podemos distinguir los siguientes pasos: • partimos de una descripción informal del comportamiento deseado del circuito que queremos diseñar. • A partir de esta descripción, generaremos una descripción en un lenguaje de descripción de hardware (como puede ser VHDL). Dicha descripción puede ser a nivel de comportamiento o directamente a nivel de estructura; no obstante, lo usual es obtener una descripción a nivel de comportamiento que con los algoritmos adecuados proporcionará una descripción a nivel de estructura. • Esta estructura es traducida a componentes de niveles inferiores en la jerarquía como son las puertas lógicas y biestables. • Las puertas lógicas son diseñadas o elegidas de una librería de celdas (ya se verá posteriormente la diferencia) hasta el nivel físico o layout. • Con estos layout se hará una planificación del espacio para poder determinar el lugar en el que se colocarán las diferentes celdas. • Una vez que se han colocado todas las celdas, se realizará el conexionado de todos los nodos del circuito. En el proceso anterior no se ha comentado nada sobre ninguna estrategia a la hora de pasar de un nivel a otro. Realmente, las únicas diferencias se encuentran en las dos últimas etapas: el nivel eléctrico y físico. Todas las estrategias se pueden dividir en dos grandes grupos: • Circuitos full-custom o completamente a medida. En este caso, como su propio nombre indica, todas las puertas son realizadas por el diseñador de tal forma que se obtenga una mejor adaptación a las especificaciones del diseño. Esta realización propia será a nivel eléctrico (esquema de transistores con las dimensiones específicas) y físico (layout, que podemos crear layouts diferentes para una misma celda con el fin de que encaje mejor en el circuito reduciendo el área ocupada). • Circuitos semi-custom o semi-medida. En este caso, se utiliza una librería de celdas que impone el esquema a nivel eléctrico y el layout de los diferentes componentes. La única libertad que le queda al diseñador en estos niveles es la colocación de las celdas en el layout final (siempre y cuando se cumplan una serie de restricciones, como es su colocación en hileras). El destino de esta estrategia puede ser un circuito integrado, denominado entonces basado en celdas, o un dispositivo programable, denominado entonces basado en matrices. Figura 1.21. Flujo de diseño. Como es obvio, ambas estrategias tendrán características diferentes. Así los circuitos full-custom son los que presentan mejores prestaciones a costa de un mayor tiempo de diseño, debido a la realización de todas las celdas. Por el contrario, los circuitos semi-custom mejoran los tiempos de diseño a costa de un empeoramiento en las prestaciones. Dentro de los circuitos semi-custom, aquellos basados en matrices son los que tienen un tiempo de diseño menor ya que no es necesaria el proceso de integración ya que se dispone del dispositivo, que con un proceso de programación adquirirá el comportamiento adecuado. Luego, no podemos encontrar el circuito ideal en el que se optimicen simultáneamente el tiempo de diseño y sus prestaciones, por lo que hay que llegar a un compromiso para decidir la estrategia con la cual abordar la tarea de diseño.