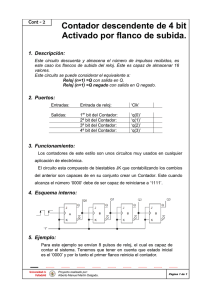

Lógica Secuencial 'SQIRXEVMSW E´EHMHSW IR VSNS 7EPXEVWI PS UYI IWX¤ XEGLEHS 0SW IVVSVIW WI GSVVMKIR IR RIKVS Circuitos Digitales, 2º de Ingeniero de Telecomunicación ETSIT — ULPGC Componentes secuenciales Contienen elementos de memoria Los valores de sus salidas dependen de los valores en sus entradas y de los valores almacenados en los elementos de memoria Los valores almacenados en los elementos de memoria definen el estado del circuito secuencial Ejemplo: contestador telefónico que responde tras cuatro timbres de llamada Componentes secuenciales Los componentes secuenciales se dividen en: Asíncronos Su salida y su estado se puede alterar en cuanto cambien los valores de sus entradas Síncronos Su salida y su estado se alteran, si acaso, sólo en determinados instantes definidos a partir de una señal de reloj Señal de reloj Período de reloj Tiempo entre transiciones sucesivas en la misma dirección Frecuencia de reloj Inversa del período de reloj Señal de reloj Ancho del pulso Intervalo de tiempo en el que la señal de reloj vale 1 Rendimiento de ciclo Relación entre el ancho del pulso (lo que está la señal a 1) y el período Señal de reloj Circuito activo a nivel alto Si reacciona ante la señal de reloj a valor 1 Circuito activo a nivel bajo Si reacciona ante la señal de reloj a valor 0 Circuito activo por flanco de subida Si reacciona ante la transición de la señal de reloj de 0 a 1 Circuito activo por flanco de bajada Si reacciona ante la transición de la señal de reloj de 1 a 0 Báscula (o latch) RS −implementación con NOR− Dos estados del latch : Estado de set (con Q = 1) Estado de reset (con Q = 0) Esquemático Báscula (o latch) RS −implementación con NOR− Tabla de verdad Esquemático Báscula (o latch) RS −implementación con NOR− Cronograma (diagrama de tiempo) Báscula (o latch) RS −implementación con NAND− Tabla de verdad Esquemático Báscula (o latch) RS −implementación con NAND− Cronograma (diagrama de tiempo) Latch RS sincronizado Símbolo Esquemático Latch RS sincronizado Latch RS sincronizado Cronograma Latch D sincronizado Símbolo Esquemático Latch D sincronizado Latch D sincronizado Cronograma Flip-fliops Los latches son sensibles al nivel Responden a los cambios en la entrada durante el pulso del reloj Los flip-flops responden a los cambios en la entrada sólo en los cambios de la señal de reloj Es más seguro trabajar con éstos, aunque son más caros Los hay de dos tipos: maestro-esclavo y disparados por flanco Desplazamiento erróneo con latches tipo D Con latches sensibles al nivel, se puede producir funcionamiento erróneo Esquemático Desplazamiento erróneo con latches tipo D Flip-flop maestro-esclavo En un flip-flop maestro-esclavo la entrada D se muestrea y se almacena su valor en en flanco de subida de la señal Clk Esquemático Flip-flop maestro-esclavo Desplazamiento con flip-flops maestro-esclavo Desplazamiento con flip-flops maestro-esclavo Flip-flops disparados por flanco Esquemático Flip-flops disparados por flanco Tipos de flip-flops )WXS 7° )WXS 2S Tipos de flip-flops )WXS 7° )WXS 2S Diagramas de estados de los flip-flops Diagramas de estados de los flip-flops Latch con entradas asíncronas 1SRXEV GSQS EQTPMEGM¶R HI GSRXIRMHSW Símbolo Esquemático Flip-flop con entradas asíncronas 1SRXEV GSQS EQTPMEGM¶R HI GSRXIRMHSW Símbolo Esquemático Símbolos gráficos de flip-flops con entradas asíncronas Análisis de lógica secuencial Se comienza identificando qué hay en las entradas de los flip-flops: Se suelen expresar de forma algebraica, y se llaman las ecuaciones de excitación Conocido el tipo de flip-flop y conocidas las funciones que definen el valor de sus entradas... Se pueden escribir las ecuaciones de estado siguiente y salidas. Análisis de lógica secuencial Con las ecuaciones de estado siguiente y salidas se puede conocer cuál es el estado siguiente y las salidas para cada estado y entrada posibles: Se organizan en una tabla de estado siguiente y salidas La misma información que en estas tablas se puede expresar de forma gráfica con un diagrama de estados Análisis de lógica secuencial El diagrama de estados permite identificar de forma clara y completa el funcionamiento de un circuito secuencial Opcionalmente se emplean cronogramas (o diagramas de tiempo ) para “ver” el funcionamiento ante un caso de estudio Análisis de un circuito secuencial Ecuaciones de excitación Ecuaciones de estado siguiente Análisis de un circuito secuencial Tabla de estado siguiente Diagrama de estados Análisis de un circuito secuencial Cronograma Análisis de un circuito secuencial de tipo Moore Ecuaciones de excitación Ecuaciones de estado siguiente y salida Análisis de un circuito secuencial de tipo Moore Tabla de estado siguiente y salida Diagrama de estados Análisis de un circuito secuencial de tipo Moore Cronograma Análisis de un circuito secuencial de tipo Mealy Ecuaciones de excitación Ecuaciones de estado siguiente y salida Análisis de un circuito secuencial de tipo Mealy Tabla de estado siguiente y salida Diagrama de estados Análisis de un circuito secuencial de tipo Mealy Cronograma Modelo de máquina de estados finitos (FSM) Modelo de máquina de estados finitos (FSM) Implementaciones de FSMs De tipo Moore Implementaciones de FSMs De tipo Mealy Diagrama de estados de un contador módulo 3 asc./desc. Diseñar un contador asc./desc. módulo 3. El contador debe tener dos entradas: orden de cuenta (C) y dirección de cuenta (D). Cuando C=1 el contador contará en la dirección indicada por D y dejará de contar cuando C=0. El contador contará hacia adelante con D=0 y hacia atrás con D=1. El contador debe tener una salida Y que se pondrá a 1 cuando el contador vaya a alcanzar el valor 2 mientras cuenta hacia atrás o cuando vaya a alcanzar el valor 0 mientras cuenta hacia adelante. Diagrama de estados de un contador módulo 3 asc./desc. Diagrama de estados de un contador módulo 3 asc./desc. %QTPMEGM¶R HI GSRXIRMHSW Diagrama de estados de un contador módulo 3 asc./desc. Diagrama de estados de un contador módulo 3 asc./desc. Minimización de estados La minimización de estados reduce el número de estados y, por ello, el número de flip-flops necesarios. Se basa en el concepto de equivalencia de comportamiento: Dos FSMs son equivalentes si producen la misma secuencia de símbolos de salida para cada secuencia de símbolos de entrada Minimización de estados (IWHI EUY° LEWXE IP ¾REP RS IRXVE REHE si y sk de una misma FSM son equivalentes si ≡ sk si y sólo si ambos estados si y sk producen el mismo símbolo de salida para cada símbolo de entrada i : h (sj,i ) = h (sk, i ) los estados siguientes para cada símbolo de entrada i son equivalentes: f (sj,i ) ≡ f (sk,i ) Minimización de estados Proceso de minimización Particionar los estados en clases de equivalencia Construir una nueva FSM con un estado por cada clase de equivalencia Reducción de estados para el contador módulo 3 Reducción de estados para el contador módulo 3 Reducción de estados para el contador módulo 3 Reducción de estados para el contador módulo 3 Codificación de estados Codificación de mínimo cambio de bits Los códigos se asignan de forma que el número de cambios de bits sea el mínimo en el total de transiciones Si a cada arco del diagrama de estados se le da como peso el número de cambio de bits en la transición, los códigos se eligen de forma que la suma de todos los pesos sea la menor Codificación de mínimo cambio de bits Codificación directa Codificación de mínimo cambio de bits Codificación de prioridad en la adyacencia En esta codificación se asignan codificaciones de la menor distancia posible a los estados con una fuente común, un destino común y una misma salida Codificación de prioridad en la adyacencia Al asignar los códigos: la mayor prioridad es para estados con un mismo estado siguiente la segunda prioridad es para los estados siguientes de un mismo estado la tercera prioridad es para los estados que tienen las mismas salidas para las mismas entradas Codificación de prioridad en la adyacencia Prioridades por adyacencia Diagrama de estados inicial Codificación de prioridad en la adyacencia Posible codificación Codificación “one-hot” Es una codificación en la que en todos los códigos sólo hay un “1” El número de bits de los códigos es igual al número de estados La posición del “1” identifica al estado Es una codificación cara para FSMs con muchos estados Se emplea para hacer FSMs más rápidas Reducción de estados para el contador módulo 3 Tabla de estado siguiente y salida codificada Tablas de excitación (recordatorio) Ecuaciones de excitación (para flip-flops RS) Ecuaciones de excitación (para flip-flops JK) Ecuaciones de excitación (para flip-flops T) Ecuaciones de excitación (para flip-flops D) Implementación con flip-flops D Ejemplo de funcionamiento de implementación con flip-flops D