Práctica 1: Caracterización de transistores

Sebastián Linares; Emiro Lara

{slinaresr, ealarar}@unal.edu.co

Laboratorio de Electrónica Análoga II

Universidad Nacional de Colombia.

1.

1.1.

Trabajo Previo

Calcular el voltaje de umbral Vt

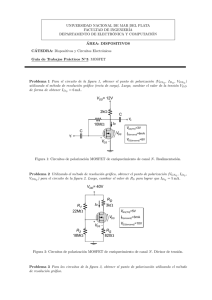

En la primera parte de la práctica se utiliza el circuito de la

figura 1.1 para determinar el voltaje de umbral de un transistor

canal N. En este circuito, al poner los terminales de drain y gate

del MOSFET en cortocircuito, se garantiza que el transistor

opera en saturación [1]:

ID

VDS = VGS

VGS

VT > 0

VDS >VGS − Vt

Siendo ası́, Vt se puede hallar a partir de variables medibles en

el circuito de la siguiente manera:

VDD − VGS

RD

1

ID = kn (VGS − Vt )2

2

VDD − VGS

2

(VGS − Vt ) =

k R

r n D

VDD − VGS

Vt = VGS −

kn RD

ID =

Figura 1: Circuito para caracterizar un

MOSFET de Canal N

En donde kn = kn0 W

L . Para esta primera parte, resulta conveniente escoger un valor de RD lo suficientemente grande, de tal forma que el término de la derecha tienda a

0, y se pueda medir Vt directamente en el circuito de la figura 1.1:

VGS ≈ Vt

Este proceso es homólogo para determinar Vt en los MOSFETs canal P, en cuyo caso VSG ≈ Vt

1.2.

Obtener el valor aproximado de la constante kn

En la segunda parte del laboratorio, se utiliza el mismo circuito para determinar kn de cada transistor de

canal N.

1

1

kn (VGS − Vt )2

2

2ID

kn =

(VGS − Vt )2

ID =

(1)

(2)

El proceso para determinar kp en los de canal P es homólogo, con la distinción de que tanto kp como ID

toman valores negativos.

1.3.

Curva caracterı́stica ID vs. VGS

Una forma de representar el funcionamiento del MOSFET en la región de saturación es con la curva ID vs.VGS .

Con el montaje del circuito 1.1, en el osciloscopio se pueden observar en dos canales, con la misma referencia

a tierra, una señal proveniente de vDD y una de VGS . De esta manera, si CH1 = VDD y CH2 = VGS , se

y CH2.

pueden construir la gráfica con datos de: ID = CH1−CH2

RD

2.

Trabajo en el Laboratorio

En el laboratorio, se montó el circuito de la figura 1.1 para cada uno de los 4 transistores N del integrado

ALD1106, y se utilizó una resistencia de RD = 11,21M Ω para medir Vt entre VG y VS . De forma homóloga,

se hizo el mismo montaje, con la polarización de la fuente en el sentido opuesto, para obtener los Vt en el

ALD1107. Tomando como número 1 el transistor entre los pines 1-3 del integrado, y 4 el que se encuentra

entre 12-14 [2], los valores de Vt para cada transistor de Canal N en el ALD1106, y de Canal P en el ALD1107,

son:

Tipo

N

No.

1

2

3

4

Vt (mV )

577

577

579

577

Tipo

P

Cuadro 1: Valores de Vt para los NMOS ALD1106

No.

1

2

3

4

Vt (mV )

-693

-703

-703

-695

Cuadro 2: Valores de Vt para los PMOS ALD1107

Posterior a esto, se cambió la resistencia RD por una de 99,0kΩ, y, para obtener los valores de kn y kp en el

nuevo montaje, se hallan usando la ecuación 2. Ası́, obtenemos:

Tipo

N

P

No.

1

2

3

4

1

2

3

4

Vt (mV )

577

577

577

577

-693

-703

-703

-695

VGS /VSG (mV )

1.025

1.023

1.024

1.025

1.292

1.300

1.300

1.295

kn /kp (µA/V 2 )

406.8

412.5

414.2

408.6

214.0

214.9

214.9

213.1

Cuadro 3: Valores de kn y kp para todos los MOSFETs

Por último, se reemplazó la fuente DC con una señal triangular de frecuencia 5Hz para emular un barrido

lineal en DC, ya que el tiempo de subida, 100ms, es relativamente largo. Esta sección sólo se realizó con

el NMOS 1. Cómo se describe en la sección 1.3, las sondas del osciloscopio fueron ubicadas en VDD y VGS

respectivamente, lo cuál nos permitió visualizar la figura 2.

2

Al exportar el archivo .csv y graficar las variables coVDD

rrespondientes, podemos observar las señales VGS e

VGS

ID en el tiempo. La gráfica de la figura 3 no es posible obtenerla y visualizarla directamente en el osciloscopio, ya que la señal de la corriente es el resultado de una operación entre los canales. Si, en

otra topologı́a, la resistencia está entre la tierra y

el MOSFET, se podrı́a medir la señal de corriente directamente en un canal, sin embargo, la señal

de tensión VGS ahora tendrá que ser un resultado de una operación matemática. Por esta razón se

exportan los datos para poder tratarlos y graficar- Figura 2: Visualización de VDD y VGS en el Osciloslos.

copio

8.00

7.00

6.00

V (V)

5.00

4.00

3.00

2.00

1.00

0.00

200

4.00

VGS

500.00

ID(µA)

3.00

400.00

300.00

ID (µA)

VGS (V)

2.50

2.00

1.50

200.00

1.00

100.00

0.50

0.00

0.00

300

350

400

450

500

550

600

650

400

500

600

700

800

Habiendo obtenido estos datos, se procede a generar la

curva de la relación entre VGS y ID . En la gráfica de la

figura 4 también se encuentra la curva caracterı́stica teórica del NMOS 1 generado con los parámetros en la tabla

3. Se puede notar que los puntos de la gráfica obtenida

experimentalmente tienen alta incertidumbre en valores

de ID y la discretización en VGS es muy gruesa: esto es

debido a la poca exactitud de los datos del .csv generado

por el osciloscopio, en los cuales sólo se utilizan 2 cifras

significativas, a pesar de que en el cursor del osciloscopio

se pueden observar 5.

600.00

3.50

300

700

Figura 3: ID y VGS en el dominio del tiempo

550

450

350

I (µA)

ID(µA)

ID-T (µA)

250

150

50

0.00

-50

0.20

0.40

0.60

0.80

1.00

1.20

1.40

1.60

1.80

2.00

VGS (V)

Figura 4: Relación VGS vs. ID para el NMOS 1 del ALD1106.

3.

Conclusiones

Los parámetros de los transistores son relativamente cercanos entre sı́ dentro de un mismo chip, lo

que permite con mayor facilidad, en prácticas futuras, implementar circuitos que lo requieran como los

espejos de corriente. Esta ventaja es debido a la integración de los MOSFETs, que permite una alta

confiabilidad en que las diferencias en parámetros de fabricación son prácticamente nulas.

3

Los ALD tienen alta capacidad para amplificación, y presentan una muy buena estabilidad frente a

ruido electromagnético. Sin embargo, debido a su tamaño y el hecho de que son MOSFETs, pueden ser

bastante sensibles a cambios de parámetros ambientales, o a perturbaciones mecánicas.

La resolución o cifras significativas que exporta el osciloscopio son de muy baja calidad, lo cual, en

algunos casos como este, no permite hacer análisis suficientemente precisos. Esto se puede deber a poca

capacidad de almacenar datos en memoria volátil del equipo.

Referencias

[1] Sedra, A., Smith, K., Microelectronic Circuits, 7th ed, Oxford University Press, 2016.

[2] Advanced Linear Devices, Inc., ALD1106/ALD1116 - Quad N-Channel, Matched Pair MOSFET Array,

Sunnyvale, CA, 2012.

4

![A = - g v = - g v vgs[1 + gmRS ] A = - g R or Av =](http://s2.studylib.es/store/data/005705056_1-504131751076188fc89289233c8ca060-300x300.png)