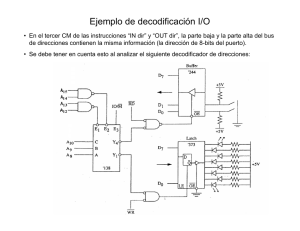

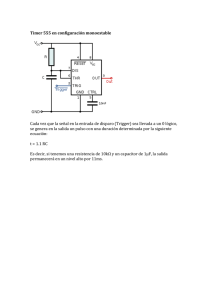

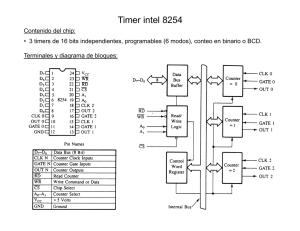

Ejemplo de decodificación I/O • En el tercer CM de las instrucciones “IN dir” y “OUT dir”, la parte baja y la parte alta del bus de direcciones contienen la misma información (la dirección de 8-bits del puerto). • Se debe tener en cuenta esto al analizar el siguiente decodificador de direcciones: Ejemplo de decodificación I/O Dirección A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Puerto de Entrada 1 1 1 1 X 1 0 0 1 1 1 1 X 1 0 0 Puerto de Salida 1 1 1 1 X 0 0 1 1 1 1 1 X 0 0 1 Parte alta bus de direcciones (idem) Ciclos de máquina instrucción OUT: Parte baja bus de direcciones (dirección del puerto) Familia de chips diseñados para el P 8085 8212: Latch de 8-bits (usado para des-multiplexar el bus de direcciones/datos) 8355 / 8755: 2K bytes ROM/EPROM 2 puertos de 8 bits (configurables como I/O) 8155 / 8156: 256 bytes de RAM estatica 2 puertos de 8 bits 1 puerto de 6 bits 1 timer de 14 bits 8253: 3 timers independientes de 16-bits 8279: controlador de display/teclado Existen otros chips de la familia 8XXX con mas funciones: comunicacion serial (8251), paralela (8255), controlador de floppy disk (8271), crt, interrupciones, etc. El P Intel 8085: sistema mínimo con chips de la familia Chip intel 8155/8156 Contenido: • • • • 256 bytes de SRAM (256x8) 2 puertos de 8 bits (PA y PB) 1 puerto de 6 bits (PC) 1 timer programable de 14 bits Terminales y diagrama de bloques: Características especiales: • Posee Latch interno para la parte baja del bus de direcciones. • Decodificación interna de la línea IO/M. Chip intel 8155/8156 Diagrama interno: Ejemplo: determinación de la dirección A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Dirección (en el mapa de IO) Puertos (IO/M=1) 20h Control (W) / Status (R) 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 1 0 0 0 0 1 21h PA 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 22h PB 0 0 1 0 0 0 1 1 0 0 1 0 0 0 1 1 23h PC 0 0 1 0 0 1 0 0 0 0 1 0 0 1 0 0 24h Timer (LSB) 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 25h Timer (MSB) 2h Ejemplo: determinación de la dirección 0 0 1 0 0 X X X 0 0 0 0 0 0 0 0 Dirección (en el mapa de Memoria) (IO/M=0) 2000h 0 0 1 0 0 X X X 1 1 1 1 1 1 1 1 20FFh A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 2h SRAM del 8155 (256x8) Chip intel 8155/8156 Registro de control: Ejemplo: displays de 7 segmentos Problema: • Conectar dos displays de 7 segmentos usando un puerto del 8155. • Escribir las instrucciones necesarias para inicializar y escribir un dato en los displays. Chip intel 8155: el Timer • Se trata de un contador descendente de 14-bits. Cuenta los pulsos de la entrada TIMER IN. • Entrega una onda cuadrada o un pulso, cuando se alcanza el cero (Terminal Count). • Para programar el timer, primero se debe cargar el registro de longitud de cuenta (Count Length) de dos bytes. • En el ejemplo anterior sería en las direcciones de I/O 24h (LSB) y 25h (MSB). • Los bits 0-13 son la longitud de cuenta, mientras que los bits 14 y 15 determinan el modo de funcionamiento del timer: T7 T6 T5 LSB T4 T3 T2 T1 T0 (24h) M2 M1 T13 MSB T12 T11 T10 T9 T8 (25h) Chip intel 8155: el Timer Modos del Timer del 8155: Modo 0: En este modo, la salida del timer permanece en alto por la primer mitad del conteo y va a bajo en la segunda mitad, entregando asi un ciclo de onda cuadrada. La duración del pulso esta determinada por la longitud de cuenta y por la frecuencia de clock. Modo 1: En este modo, el valor inicial de cuenta es recargado de forma automatica al final de cada cuenta, entragando asi una onda cuadrada contínua. Modo 2: En este modo, un pulso único es entregado al final del conteo (con una duración de un clock). Modo 3: Similar al Modo 2, salvo que el conteo inicial es recargado al final para proveer un tren contínuo de pulsos. N = Longitud de cuenta Chip intel 8155: el Timer Registro de control: Ejemplo: “dividir la frecuencia de entrada por 3600” 3600 = E10h LSB = 10h = 00010000b MSB = 4Eh = 01001110b INICIO: (parte baja) (parte alta, incluye modo) MVI OUT A,10h 24h ; cargo LSB MVI OUT A,4Eh 25h ; cargo MSB MVI OUT A,1100XXXXb 20h ; empieza a contar… HLT