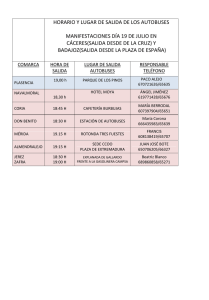

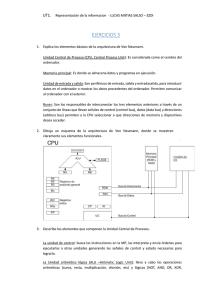

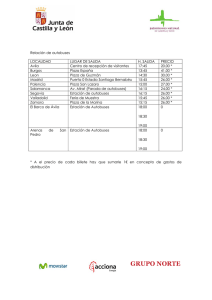

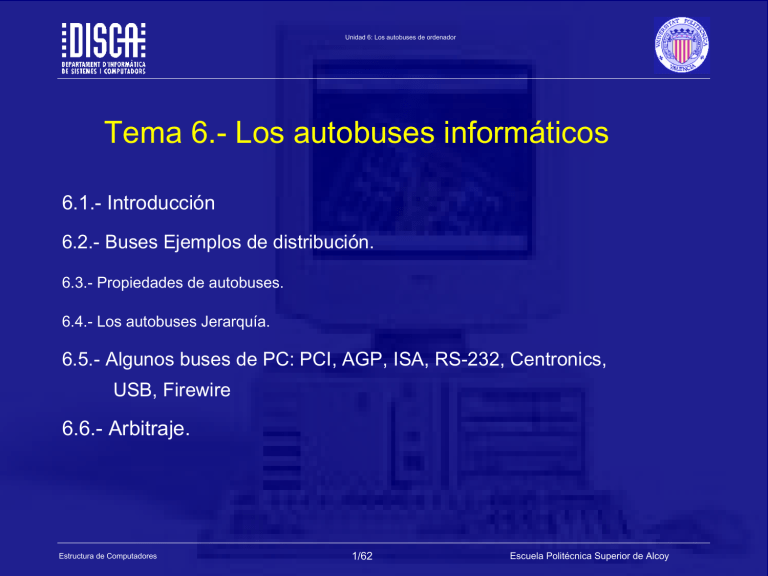

Unidad 6: Los autobuses de ordenador Tema 6.- Los autobuses informáticos 6.1.- Introducción 6.2.- Buses Ejemplos de distribución. 6.3.- Propiedades de autobuses. 6.4.- Los autobuses Jerarquía. 6.5.- Algunos buses de PC: PCI, AGP, ISA, RS-232, Centronics, USB, Firewire 6.6.- Arbitraje. Estructura de Computadores 1/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador Introducción 6.1- Introducción. definición de autobuses: Un conjunto de conexiones físicas (cables, circuitos impresos, etc.) que pueden ser compartidos por múltiples componentes de hardware con el fin de comunicarse entre sí, de acuerdo con algunas reglas de conexión. Estructura de Computadores 2/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.1- Introducción. definición de autobuses: El propósito de autobuses es reducir el número de "vías" necesarios para la comunicación entre los componentes, mediante la realización de todas las comunicaciones a través de un único canal de datos. Es por esto que a veces se utiliza la metáfora de una "autopista de la información". El rendimiento de un sistema no sólo depende de la capacidad de la CPU o la memoria, sino también de cómo se diseñó la arquitectura de bus. Si sólo hay dos componentes de hardware se comunican a través de la línea, se llama un puerto de hardware (como un puerto serie o puerto paralelo). Estructura de Computadores 3/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.1- Introducción. definición de autobuses: Estructura de Computadores 4/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.1- Introducción. definición de autobuses: Capacidad de transferir datos entre dispositivos. información de señalización adecuada. Un bus debe incluir un medio de controlar el flujo de datos. Incluir una definición de puerto para permitir la interconexión física o la conexión de dos o más dispositivos. Por lo general aparecen en forma de pistas sobre una placa de circuito impreso (PCB). Cuatro grupos funcionales: el poder, dirección, datos y control. Estructura de Computadores 5/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.1- Introducción. Autobús: esquema general Estructura de Computadores 6/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.1- Introducción. En general, existen dos buses dentro de un ordenador: los bus interno (A veces llamado el bus frontal o FSB por sus siglas). El bus interno permite que el procesador para comunicarse con la memoria central del sistema (la RAM). los bus de expansión (aveces llamado el de entrada y salida bus) permite diversas placa base componentes (USB, serie y puertos paralelos, tarjetas insertadas en conectores PCI, discos duros, CD-ROM y CD-RW, etc.) que se comunican entre sí. Sin embargo, se utiliza principalmente para añadir nuevos dispositivos que utilizan lo que se llama ranuras de expansión conectados a la outpur bus / entrada. Estructura de Computadores 7/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.1- Introducción. En general, existen dos buses dentro de un ordenador: Estructura de Computadores 8/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.2- ejemplos de distribución. UPC Memoria Unidad Unidad de E / S de E / S Unidad UPC Unidad Memoria de E / S de E / S Adaptador Adaptador UPC Memoria Adaptador Adaptador Unidad Unidad Unidad Unidad de E / S de E / S de E / S de E / S E/S Unidad de E / S Unidad Adaptador E/S Unidad de E / S Unidad Estructura de Computadores 9/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses transmisión de banda base . No hay ninguna modulación de la señal. grado de paralelismo. Número de bits transferidos simultáneamente. De serie: Los bits se transmiten de uno en uno, uno tras otro. Paralelas: Los bits de datos se transfieren de forma simultánea. multiplexado : Datos compartidos y líneas de dirección. Dirección line.Bus control válido válida o datos utilizado por primera vez para especificar una dirección, entonces se utiliza para transferir datos. Menos líneas, ahorra espacio, un menor costo. control más complejo, potencial actuación reducción. Estructura de Computadores 10/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses multiplexado : Datos compartidos y líneas de dirección. Estructura de Computadores 11/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses temporization : ciclo dividido : Bus no siempre está ocupado durante la operación. Una transacción se divide en dos transacciones: Transacción de petición-respuesta y en transacciones. Más complejo, más rápido. ciclo completo : Bus está ocupado durante toda la operación. Otros pueden utilizar el autobús bus ocupado bus ocupado Ciclo de Split Solicitud Responder Autobuses ocupados (otros no pueden utilizar el autobús) toda Ciclo Estructura de Computadores Solicitud Responder 12/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Modo de operación . Forma de llevar a cabo una transferencia: protocolo, el orden y la temporización de la señal. Sincrónico : línea de control de reloj. Eventos determinados por la señal de reloj de alta velocidad. Problema: dispositivos con diferentes velocidades. estados de espera se pueden insertar. buses de memoria tienden a ser sincrónica. modos de transferencia:. 1x, 2x, ... (una palabra por ciclo, dos palabras por ciclo, ...). Estructura de Computadores 13/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Modo de operación. Sincrónico: Estructura de Computadores 14/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Modo de operación. Sincrónico: Estructura de Computadores 15/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Modo de operación. Asincrónico: Sin línea de reloj. La transmisión de datos es coordinado por el apretón de manos. Un evento desencadena la siguiente y así sucesivamente. Permite la conexión de dispositivos con diferentes velocidades. Más lento debido al apretón de manos protocolo. Difícil anticipar el tiempo necesitará una transferencia. Para que las unidades de E / S. semisincrónico: señal de reloj como para el tipo síncrono, sino también la señal WAIT (esperar ciclos), y listo (o similar). Estructura de Computadores 16/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Modo de operación. Asincrónico: Estructura de Computadores 17/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Estrategia de control : Maestro: Dispositivo con iniciativa. Es capaz de iniciar una transferencia. Esclavo: Dispositivo sin iniciativa. obedece las reglas procedentes de un dispositivo maestro. Arbitraje : Si hay más de un maestro, debe determinarse cuál se controla el autobús en cada momento: protocolo de arbitraje del bus. Un maestro que desee utilizar el bus afirma una solicitud de bus y más tarde se le concede el autobús, cuando sea posible. Estructura de Computadores 18/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Arbitraje : Estructura de Computadores 19/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses longitud máxima : Están diseñados para funcionar bien siempre que su longitud no supera alguna límite. Protocolo : El conjunto de reglas acordadas por los dispositivos conectados a un bus como a cómo los datos se va a transferir a través del bus. Protocolos dividir los datos en bloques o tramas de datos. capacidad de conexión : Número de dispositivos que se pueden conectar al bus. restricciones lógico o electrónico (problema de direccionamiento) Estructura de Computadores 20/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Velocidad . Generalmente expresada en bits por segundo (bps). Cada bus tiene una “sobrecarga” para proporcionar otras funciones de control de flujo, direccionamiento, etc. Porcentaje máximo: mejor de los casos. tasa de rendimiento sostenido. ¿Qué tasa de bps puede ser utilizado para transferir información entre dispositivos? Esto dependerá de la longitud, los medios de transferencia (pares, coaxial, fibra óptica, ..), lógica de control, el grado de paralelismo, etc. Estructura de Computadores 21/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Solicitud : Qué está diseñado para el bus ?, industrial comunicaciones, PC, TV, etc. ciclos de bus disponibles . Además de las habituales, ¿Permite DMA o ciclos de interrupción? ciclos de ráfaga : Acelerar el transferir de datos consecutivos. Ex: modo de ráfaga 5-2-2-2: la primera de datos necesita 5 ciclos de reloj, pero los próximos tres a sólo 2 ciclos de reloj. Estructura de Computadores 22/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses tipo de lógica : Por lo general negativo: menor consumo de energía, la conmutación rápida, desconectan dispositivos tienen un nivel apropiado. Soporte físico : El material utilizado para la conexión física. pistas de circuito impreso, alambres, pares, fibra coaxial, óptica, etc. Estructura de Computadores 23/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses dirección de información : unidirectionals : transmisor uno receptores. los conductores de tres estados (alto, y varios bajo, off). Ex: líneas de dirección. unidirectionals : varios transmisores y uno receptor. Logical-OR de las fuentes. Ex: interrumpir peticiones. Bidirectionals : El mismo dispositivo puede ser transmisor o receptor. Por ejemplo: líneas de datos. Estructura de Computadores 24/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Estructura de Computadores 25/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses la contención de bus : Situación indeseable en la que más de un ouput accede a la misma línea de bus. Muy a menudo se encuentran durante los cambios de líneas superpuestas en un autobús: Antes de que se anula la selección de A, B está seleccionada: Estructura de Computadores 26/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses travesaño autobús : múltiples buses operan en paralelo, proporcionando un mayor ancho de banda. Consta de una matriz NxM de interruptores de conexión N entradas a M salidas. Es no-bloqueo (a menos que dos o más entradas quieren hablar con la misma salida), y asegura la conectividad completa será todas las permutaciones posibles. Estructura de Computadores 27/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses líneas de control usuales: escritura de memoria y la memoria leen. E / S de escritura y lectura I / O. Transferir ACK. petición de bus. otorgamiento de enlace. solicitud de interrupción. Interrupt ACK. Reloj. Reiniciar. .. . Estructura de Computadores 28/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.3- propiedades Buses Problemas de diseño: Alto rendimiento Propiedad Bajo costo bus de datos y bus de direcciones De datos y direcciones separadas multiplexadas Más amplio, más rápido Más estrecho, más barato tamaño de transferencia transferencias de bloques las transferencias de palabras Maestro Varios patrones de maestro único transferencia de Split si No Sincronización Sincrónico Asincrónico Ancho de bus Estructura de Computadores 29/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Estructura de Computadores 30/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Bus tipo 0: • Interno Estructura de Computadores • Sin acceso • Sin información 31/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Tipo de bus 1: • la interconexión IC • Short (cm) • No hay necesidad de tampones o terminales • Por Estructura de Computadores lo general, sincrónica con un solo maestro 32/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Tipo de bus 2 (backplane): • conexión • longitud • Deben de diferentes juntas media (<1 m) ser estándar • Algunos 100 líneas (datos + control de dirección +) • ciclo enteras o partidas • Ejemplos: Estructura de Computadores ISA, EISA, PCI, EMV, ... 33/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Bus tipo 3 (Sistema): • conexión de los diferentes módulos • No utilizado • Tipos 2 y 3 similares • Hasta 10 m • Necesidad de terminales • cables y repetidores blindados Estructura de Computadores 34/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Bus tipo 4 (buses paralelos): • Para •4 la conexión periférica conexiones posibles: • Directamente a bus de tipo 2 o 3 • Bus especial (PCI-ISA) • Reducida autobús no estándar • bus estándar paralelo (SCSI, IEEE-488, ...) Estructura de Computadores 35/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.4- jerarquía de autobuses Bus tipo 5 (buses de serie): • Para la conexión periférica. • Permitir conexiones más largas. • Por lo general, más lento. • Unidirectionals, bidirectionals, half-duplex, dúplex completo, ... • Control incrustado en los datos. • Puertos serie: RS-232, RS-485, USB, I2C, SPI, ... • Las redes locales: Ethernet, Fast Ethernet, ... Estructura de Computadores 36/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC ISA bus (Industria estandar de arquitectura) Del bus de direcciones de 20 bits. Bus de datos de 8 bits Muchos PC-AT señales de interrupción incluido. controlador de DMA se puede utilizar. Dos partes: uno clásico con 8 bits (PC, XT y AT) Extended con 16 bits (AT) Estructura de Computadores 37/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC ISA bus (Industria estandar de arquitectura) - Evolución desde el primer bus del PC: PC / XT. - 16 líneas de datos y 20 líneas de dirección. - Las interrupciones no puede ser compartida. - 8 MHz de velocidad máxima Estructura de Computadores 38/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC ISA bus (Industria estandar de arquitectura) Estructura de Computadores 39/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC bus ATA interfaz principal para conectar un disco duro / CD duro a un PC. También conocido como IDE (Integrated Drive Electronics). Se refiere al hecho de que el controlador está construido en la unidad y no en una tabla separada. Inicialmente, ATA fue un interfaz paralelo de 16 bits. ATA-1. Las versiones mejoradas se hace referencia como: ATA-2, ATA-3, ATA / ATAPI-4, ATAPI, ATA-5, ATA-6, ATA-7, SATA / ATAPI-8 ( De serie ATA), SATA II, SATA III, ATA RAID. Estructura de Computadores 40/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC Bus SATA: SATA I (1.x). La interfaz SATA primera generación funcionando a 1,5 Gbit / s. El rendimiento de ancho de banda, que está soportado por la interfaz, es de hasta 150 MB / s. SATA II (2.x) de la interfaz, segunda generación interfaz SATA funcionando a 3,0 Gb / s. El rendimiento de ancho de banda, que está soportado por la interfaz, es de hasta 300 MB / s. SATA III (3.x), funcionando a 6.0Gb / s. El rendimiento de ancho de banda, que está soportado por la interfaz, es de hasta 600 MB / s (4,8 Gb / s). Las diferencias entre la velocidad de carrera y ancho de banda rendimiento son debido a la codificación 8B / 10B: 8 bits de datos se sustituyen por 10 bits de datos + codificación. compatibilidad con versiones anteriores. Estructura de Computadores 41/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC Bus ATA vs SATA Estructura de Computadores 42/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC bus PCI (Interconexión de componentes periféricos) Desarrollado por Intel en 1992. Topología de bus compartido: los diferentes dispositivos PCI están unidos al mismo bus, y comparten el ancho de banda. Independiente de la arquitectura. Periféricos se pueden mover entre sistemas informáticos que utilizan el mismo estándar de bus. Acceso directo a la memoria del sistema para los dispositivos conectados. Utiliza un puente para conectar con el bus frontal y por lo tanto a la CPU. Release 2.1: 66 MHz, 32 y 64 conectores bits. Varios maestros. el intercambio de interrupción. De datos y direcciones multiplexadas. Estructura de Computadores 43/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC bus PCI (Interconexión de componentes periféricos) rendimiento PCI no puede ser suficiente para algunas aplicaciones. PCI correo X tendido: duplicó el bus de 64 bits y la tasa de reloj de hasta 133 MHz: ancho de banda máximo de 1 GB / s. PCI mi xpress: Adopción de la topología de bus punto a punto. Las diferentes versiones. Estructura de Computadores PCI PCI Express 1x PCI Express 4x PCI Express 8x PCI Express 16x IDE (ATA100) IDE (ATA133) 1056 Mb / s SATA I 1500 Mb / s SATA II SATA III FireWire 400 Gigabit Ethernet 3000 Mb / s 44/62 2.500 Mb / s 10.000 Mb / s 20.000 Mb / s 40.000 Mb / s 800 Mb / s 1064 Mb / s 6000 Mb / s 400 Mb / s 1000 Mb / s Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC bus AGP (Puerto de gráficos acelerados) basada en PCI. Desarrollado por Intel en 1996 para evitar los cuellos de botella en las tarjetas gráficas. Sólo una ranura: puerto. Optimizado para trabajar con gráficos. Los datos y las direcciones no son multiplexadas. 64 MHz y 133 MHz de velocidad. Siendo reemplazado por el PCI-Express. AGP 1X 264 MB / s AGP 2X 528 MB / s AGP 4X 1 GB / s AGP 8X 2.133 MB / s Estructura de Computadores 45/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC Bus PCI, AGP y PCI Express Estructura de Computadores 46/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC bus SCSI (Small Computer System Interface) bus de interconexión de los diferentes tipos de periféricos: HD, CD-ROM, escáneres, impresoras, etc. El controlador está en la placa principal o en una tarjeta de expansión. Hasta 8-16 unidades físicas. Más rápidamente que el ATA (IDE). Hasta 640 MB / s con Ultra 640 SCSI. Fue especialmente diseñado para estaciones de trabajo y servidores de alto rendimiento. Diferentes versiones: SCSI-2, -3, Fast SCSI, Fast Wide SCSI, Ultra Wide SCSI, ... Estructura de Computadores 47/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC Universal Serial Bus (USB) Serial Bus para conectar cualquier tipo de periférico: ratón, teclado, escáner, impresora, módem, etc. hasta 127 dispositivos. Conexión en caliente. Cables de fuerza. Diferentes versiones: USB 1.0, USB 2.0, USB 3.0 diferentes velocidades de transferencia: 1,5 Mbps, 12 Mbps, 480 Mbps, 4800 Mbps. USB 3.0: más rápido y más eficiente de la energía. Compatible con versiones anteriores. Estructura de Computadores 48/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC Universal Serial Bus (USB) Fot. 256 flash USB flash 4 MB 256 MB USB 1.0 5.3 s USB 2.0 0,1 s Canción / USB 3.0 0,01 s Estructura de Computadores Película USB flash de alta definición 1 GB 6 GB 16 GB 25 GB 5,7 min 22 min 2,2 h 5,9 h 9.3 h 8,5 s 33 s 0,8 s 3.3 s 49/62 SD película 3,3 min 8,9 min 13,9 min 20 s 53,3 s 70 s Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC De serie RS-232 Bus autobús extremadamente simple. Todavía en uso para algunas aplicaciones industriales, principalmente. Pueden obtenerse a partir USB parcialmente. Adecuado para punto para conexiones punto a punto (PPP) de hasta 100 m. Estructura de Computadores 50/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC bus FireWire (IEEE 1394) Alta velocidad de bus de serie. Diseñado para cámaras digitales y otros dispositivos multimedia. Algunas de las características son las mismas que en USB: conexión en caliente, autoconfiguración, etc. Velocidades de hasta 30 veces la velocidad del USB clásica. Estructura de Computadores 51/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC UNA chipset es el componente que enruta los datos entre los buses de la computadora, de modo que todos los componentes que conforman el equipo pueden comunicarse entre sí. El conjunto de chips originalmente estaba compuesto de un gran número de chips electrónicos, de ahí el nombre. Por lo general, tiene dos componentes: los Puente norte (También llamado el controlador de memoria) es el encargado de controlar las transferencias entre el procesador y la memoria RAM, que es por eso que se encuentra físicamente cerca del procesador. A veces se llama el GMCH, por Gráfico y hub controlador de memoria. los SouthBridge (También llamado el controlador de entrada / salida o controlador de expansión) se ocupa de las comunicaciones entre los dispositivos periféricos. También se llama la ICH (concentrador de controladores de I / O). El término puente se utiliza generalmente para designar un componente que conecta dos buses. Estructura de Computadores 52/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC CPU II principal Mem puente Secundaria (ISA) Bus Puente norte del Sur bus AGP Los autobuses UPC GMem • RS-232 de serie, gcard • Paralelo, USB bus de bus IDE CPU PCI bus Estructura de Computadores 53/62 • I2C, ... bus Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.5- Algunos buses de PC Hub controlador de memoria Sistema de autobús (" Frente del lado del bus “): 64b x 800 MHz (6,4 GB / s), 533 ( “ Puente norte “) MHz, o 400 MHz salida de gráficos: 2.0 GB / s DDR SDRAM Gbit Ethernet: 0.266 GB / s Memoria principal Hub Bus: 8b x 266 MHz 2 ATA de serie: 150 MB / s 2 ATA paralelo: 100 MB / s 8 puertos USB: 60 MB / s Concentrador de controladores de I / O ( “ Southbridge “) Estructura de Computadores 54/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje arbitraje de bus : Un sistema elaborado para resolver los conflictos de control de bus (más de un dispositivo quiere usar el bus al mismo tiempo) y la asignación de prioridades a las peticiones de control del bus. Estática: asignación del bus entre los maestros se realiza de una manera predermined. Dinámica: esquema de asignación de la demanda. Bus Mastering: Un método para habilitar diferentes controladores de dispositivos en el bus a 'hablar' el uno al otro. Cuando multimastering se permite: Asimétricas: prioridades se pueden aplicar. Simétricos: Todos los maestros tienen la misma prioridad. autobús sobrecargas. Estructura de Computadores 55/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje Clasificación de acuerdo con el algoritmo de arbitraje : Algoritmo FCFS (primer llegado, primer servido) ventajas desventajas Simétrico Sólo teórico Fácil Las prioridades estáticas: cada maestro tiene una no es simétrico prioridad diferente Ineficiente, un maestro puede dar el Round Robin: se cambian las prioridades (Gira el autobús entre los maestros) simétrico, fácil para implementar no lo necesitan reasignación de prioridad LRU (menos recientemente utilizado) Simétrico Aleatorio Estructura de Computadores bus incluso si lo hace 56/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje Clasificación de acuerdo con el la distribución física del arbitraje : centralizado : Centralizado arbitraje del bus requiere hardware (árbitro) que otorgará el autobús a uno de los dispositivos que solicitan. Este hardware puede ser parte de la CPU o que puede ser un dispositivo separado en la placa base. Distribuida o descentralizada : En este arbitraje no hay árbitro, por lo que los dispositivos tienen que decidir quién va al lado. Cada módulo tiene una lógica de control de acceso. Un algoritmo distribuido se utiliza para determinar el maestro que debe coger el autobús. Esto hace que los dispositivos más complicados, pero ahorra el gasto de tener un árbitro. Estructura de Computadores 57/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje Clasificación de acuerdo con el distribución física : centralizado Estructura de Computadores 58/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje Clasificación de acuerdo con el distribución física : Repartido Estructura de Computadores 59/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje Clasificación de acuerdo con la distribución física: TIPO centralizado Repartido ventajas desventajas Diseño y prioritarios cambios fácil Muchas líneas, poca flexibilidad, y sensible a las fallas Escalable y tolerante a fallos Mas complejo Semidistributed Estructura de Computadores 60/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje Arbitraje se puede implementar de varias maneras (tanto centralizadas o distribuidas): La conexión en cadena : Se utiliza una sola señal de petición de bus compartido para todos los maestros. La línea de solicitud de bus está conectado por cable-operación AND de manera que la línea de petición pasa a nivel bajo si uno o más maestros solicitan el bus. Cuando el árbitro central recibe la solicitud, envía una señal de concesión para el primer maestro en la cadena. Cada maestro puede transmitir la señal de concesión de entrada a su vecino si no quiere utilizar el autobús. Estructura de Computadores 61/62 Escuela Politécnica Superior de Alcoy Unidad 6: Los autobuses de ordenador 6.6- Arbitraje La conexión en cadena : Estructura de Computadores 62/62 Escuela Politécnica Superior de Alcoy