ESTRUCTURA DE UNA MEMORIA ELEMENTOS:

Anuncio

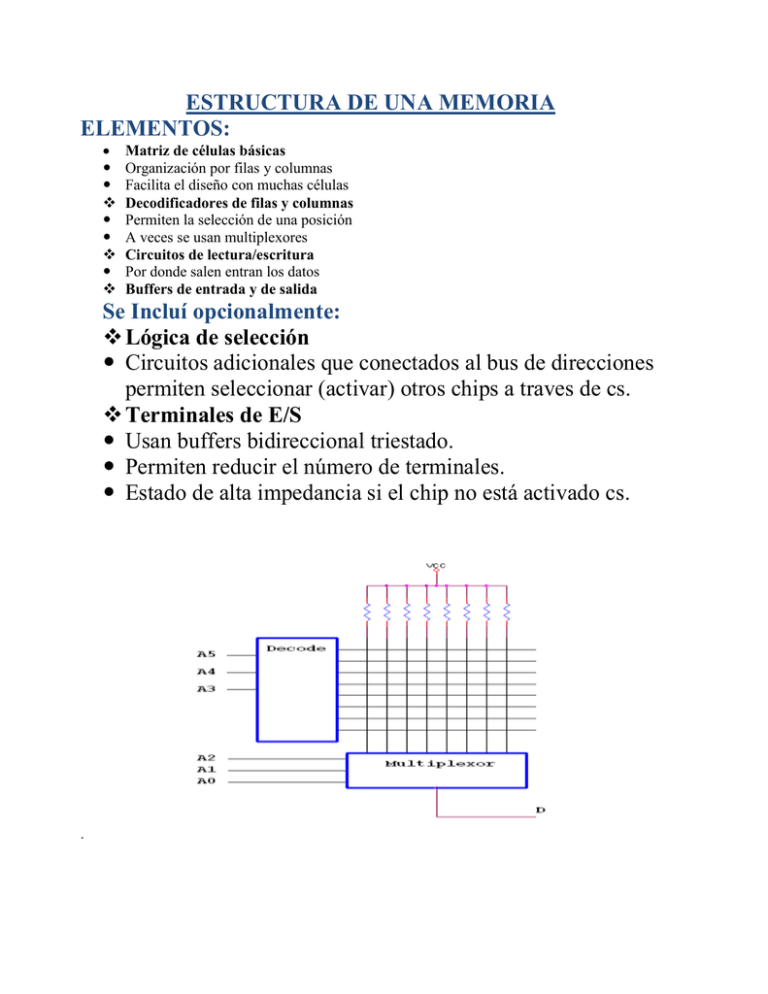

ESTRUCTURA DE UNA MEMORIA ELEMENTOS: Matriz de células básicas Organización por filas y columnas Facilita el diseño con muchas células Decodificadores de filas y columnas Permiten la selección de una posición A veces se usan multiplexores Circuitos de lectura/escritura Por donde salen entran los datos Buffers de entrada y de salida Se Incluí opcionalmente: Lógica de selección Circuitos adicionales que conectados al bus de direcciones permiten seleccionar (activar) otros chips a traves de cs. Terminales de E/S Usan buffers bidireccional triestado. Permiten reducir el número de terminales. Estado de alta impedancia si el chip no está activado cs. . MEMORIAS Definición.- Dispositivo basado en circuitos que posibilitan el almacenamiento limitado de información y su posterior recuperación. Memorias volátil o no volátil: si los datos almacenados en la memoria se pierde cuando se apaga la cámara, entonces es una memoria volátil. Por ejemplo: la RAM. Pero si los datos almacenados no se pierden cuando se apaga la cámara cuando se le llama no volátil. Por ejemplo: ROM. CLASIFICACION.- memorias RAM - memorias ROM MEMORIA RAM RAM (Random Access Memory): es de lectura y escritura. Es volátil, en cuanto se apaga el ordenador se pierde toda la información en ella almacenada. En ella se guardan los programas (secuencias de instrucciones) y los datos. Es la mayor parte de la memoria central. Puede ser leída y escrita por el microprocesador u otros dispositivos de hardware tanta veces como se quiera. Son memorias de acceso aleatorio volátiles .En esta memoria se puede realizar tanto operaciones de lectura como de escritura cuantas veces sea necesario . CARACTERISTICAS: Almacenan datos o valores que cambian con frecuencia Volátiles (Variedad NVRAM no volátil porque se alimenta con batería) Acceso aleatorio Operaciones de lectura y escritura Estructura de una memoria RAM Es útil pensar que la RAM consta de varios registros, cada uno de los cuales almacenan una sola palabra de datos y tiene una dirección única. Las RAMS comúnmente vienen con capacidades de palabras de 1K, 4K, 8K, 16K, 64K, 128K, 256K, y 1024K, y tamaños de palabras de 1, 4, u 8 bits. Como veremos más adelante, la capacidad de las palabras y el tamaño de estas puede extenderse combinando circuitos integrados de memoria. Operación de lectura. El código de dirección selecciona un registro del circuito de memoria para leer o escribir. A fin de leer el contenido de registro seleccionado, la entrada lectura/escritura (R/-W)* debe ser un 1. Además, la entrada (CS) selección de CI debe ser activada (un 0 de este caso). La combinación de R/-W es igual a 1 y CS es igual a 0 habilita los buffers de salida de manera que el contenido de registro seleccionado aparecerá en las cuatro salidas de datos. R/-W igual a 1 también deshabilita los buffers de entrada de manera que las entradas de datos no afecten la memoria durante la operación de lectura. Operación de escritura. Para escribir una nueva palabra de cuatro bits en el registro seleccionado se requiere que R/-W igual a 0 y CS igual 0. Esta combinación habilita los buffers de entrada de manera que la palabra de cuatro bits aplicada a las entradas de datos se cargara en el registro seccionado. R/-W igual a 0 también deshabilita los buffers de salida que son de tres estados, de manera que las salidas de datos se encuentran en el estado de alta-z, durante una operación de escritura. La operación de escritura, desde luego, destruye la palabra que antes estaba almacenada en la dirección. Selección de CI. Muchos circuitos de memoria tienen una o mas entradas CS que se usan para habilitar o deshabilitar el circuito en su totalidad. En el modo deshabilitado todas las salidas y entradas de datos se deshabilitas (alta-z) de manera que no puede tener lugar no la operación de lectura ni de escritura. En este modo en contenido de la memoria no se afecta. La razón para tener entradas CS será mas clara cuando se combinen CI de memoria para tener mayores memorias. Observe que muchos fabricantes llaman a estas entradas CE (habilitación de circuito). Cuando las entradas CS o CE se encuentran en un estado activo, se dice que el CI de memoria a sido seleccionado; de otro modo se dice que no está seleccionado. Muchos CI de memoria están diseñados para consumir una potencia mucho menor cuando están seleccionados. En sistemas de memoria grandes, para una operación dada de memoria, serán seleccionados una o más CI de memoria mientras que los demás no. Terminales comunes de entrada/ salida. A fin de conservar terminales en un encapsulado de CI, los fabricantes a menudo combinan los funciones de entradas y salida de datos utilizando terminales comunes de entrada/salida. La entrada R/-W controla la función de estas terminales E/S. Durante una operación de lectura, las terminales de entrada y salida actúan como salida de datos que reproducen el contenido de la localidad de dirección seleccionada. Durante una operación de escritura, las terminales de S/E actúan como entrada de datos. A las cuales se aplican los datos al ser escritos. Estos 2 tipos difieren en la tecnología que utilizan para almacenar datos, RAM dinámica que es el tipo más común. La RAM dinámica necesita ser restaurada millares de veces por segundo. La RAM estática no necesita ser restaurada, lo que la hace más rápida; pero es también más costosa que la DRAM. Ambos tipos de RAM son volátiles, significando que pierden su contenido cuando se interrumpe el suministro de poder o fuente. RAM estática (SRAM) Memoria Estática de Acceso Aleatorio es un tipo de memoria basada en semiconductores que a diferencia de la memoria DRAM, es capaz de mantener los datos, mientras esté alimentada, sin necesidad de circuito de refresco. Sin embargo, sí son memorias volátiles, es decir que pierden la información si se les interrumpe la alimentación eléctrica. Puede almacenar datos mientras se aplica energía al circuito. Celdas: flip-flops. Disponibles en tecnología bipolar y MOS (NMOS y CMOS). Características Retiene datos mientras se suministra corriente. Los chips de RAM estática tienen tiempos de acceso de 10 a 30 nanosegundos. RAM dinámica (DRAM) La memoria DRAM es una memoria RAM electrónica construida mediante condensadores. Los condensadores son capaces de almacenar un bit de información almacenando una carga eléctrica. Lamentablemente los condensadores sufren de fugas lo que hace que la memoria DRAM necesite refrescarse cada cierto tiempo: el refresco de una memoria RAM consiste en recargar los condensadores que tienen almacenado un uno para evitar que la información se pierda por culpa de las fugas (de ahí lo de “Dynamic”). La memoria DRAM es más lenta que la memoria SRAM, pero por el contrario es mucho más barata de fabricar y por ello es el tipo de memoria RAM más comúnmente utilizada como memoria principal Para aplicaciones donde los factores de velocidad y reducción en la complejidad son más importantes que las consideraciones de espacio y consumo de potencia, las RAM estáticas siguen siendo la mejor opción. Características Es la memoria de trabajo, por que a mayor cantidad de memoria, más datos se pueden tener en ella. Los chips están por encima de los 30 nanosegundos. Mientras se refresca el procesador no se pude acceder a ella. Se encuentra en la placa base como memoria principal del sistema. La celda básica es más simple, ocupa menos espacio físico que una SRAM. Pueden lograrse densidades de almacenamiento muchos mayores que una SRAM. Necesidad de refrescamiento de la información. Refrescamiento de una celda de DRAM DRAM celda básica. Un condensador . La RAM (memoria de acceso aleatorio) se refiere a veces como DRAM para distinguirla de la RAM estática (SRAM). La RAM estática es más rápida y menos volátil que la RAM dinámica, pero requiere más potencia y es más costosa Abreviatura para la memoria de acceso al azar estática. SRAM es un tipo de memoria que es más rápida y más confiable que la DRAM más común (RAM dinámica). El término se deriva del hecho de que no necesitan ser restaurados como RAM dinámica. Como un condensador se descarga, la información Almacenada en una DRAM se debe actualizar cada Cierto tiempo, REFRESCAMIENTO de la DRAM. El diagrama de circuito de la RAM estática MOS es como: En este circuito T 1 y T 3 son cargas T 2 y T 4 son resistencias. T 9 se utiliza para la operación de escritura y T 10 para operación de lectura. X e Y líneas se utilizan para tratar la célula. Cuando X = 1 T 5 y T 6 estará en ON cuando Y = 1, T 7 y T-6 estará en ON. (I) ¿Cuál fue la operación: Para realizar la operación de escritura, T 9 se pone en ON 'Si los datos son 1 lógico, entonces T 3 se convirtió en' ON Si los datos son 0 lógico entonces T1 es "ON" (II) La operación de lectura: Para el MOSFET de operación de lectura (T 10) se convirtió en 'ON' Este se conectará a la línea de datos de datos de salida Por lo tanto se complementan de los datos almacenados que se lee. MEMORIAS ROM Es de sólo lectura, también es de acceso directo. Almacena la información de manera permanente, uno de sus usos más habituales es para guardar la BIOS de la placa base, necesaria para el arranque del ordenador. Algunos chips ROM tienen su contenido grabado permanentemente desde su fabricación. Son memorias de acceso aleatorio no volátiles que solo permiten lectura de los datos almacenados previamente, bien durante su fabricación o bien en un proceso independiente. Es memoria no volátil de solo lectura Independiente de una fuente de corriente Dependiendo del proceso de grabación. Las memorias de solo de lectura ROM (del inglés read only memory) se caracteriza por ser memorias de lectura y contiene celdas de memoria no volátiles. Es decir que la información almacenada se conserva sin necesidad de energía. Transistor bipolar se utiliza en la celda bipolar ROM. Se como se muestra en la figura. Cuando la base del transistor no está conectado con una fila no fluye corriente a la base y que representa un almacenamiento de '0 'lógico. Por otro lado, cuando la base está conectada fluye a la base del transistor y que representa un almacenamiento de '1 'lógico. Usos: . Reside en la distribución de programas que estén estrechamente ligados al soporte físico de la computadora, y que seguramente no necesita actualización. las ROM se utilizan extensivamente en calculadoras y dispositivos periféricos tales como impresoras láser, cuyas fuentes se salvan a menudo en las ROM. ESTRUCTURA DE LA MEMORIA ROM La arquitectura (estructura) interna de un CI-ROM es muy compleja y no necesitamos conocer todos sus detalles. Sin embargo es constructivo observar un diagrama simplificado de la estructura interna. Existen cuatro partes básicas: Decodificador de renglones, arreglo de registros y buffer de salida. Arreglo de registros. El arreglo de registros almacena los datos que han sido programados en la ROM. Cada registro contiene un número de celdas de memoria que es igual al tamaño de la palabra. En este caso, cada registro almacena una palabra de 8 bits. Los registros se disponen en un arreglo de matriz< cuadrada que es común a muchos circuitos de semiconductor. Podemos especificar la posición de cada registro como una ubicada en un reglón y una columna específicos. Las 8 salidas de datos de cada registro se conectan a un canal de datos interno que corre atreves de todo el circuito. Cada registro tiene dos entradas de habilitación (E); ambas tienen que ser altas a fin de que los datos del registro sean colocados en el canal. Decodificadores de direcciones. El código de dirección aplicado A3, A2, A1, A0, determina que registro será habilitado para colocar su palabra de datos en 8 bits en el canal. Los bits de dirección A1, A0, se alimentan de un decodificador uno de 4 que activa una línea de selección de renglón, y los bits de dirección A3, A2, se alimentan de un segundo decodificador uno de cuatro que activa una línea de selección de columna. Solamente un registro estará en el renglón y la columna seleccionados por las entradas de difracción, y estará habilitado. Buffer de salida. El registro habilitado por las entradas de selección coloca el dato que tiene sobre el canal de datos. Estos datos entraran en los buffers de salida mismos que se encargan de trasmitirlos hacia las salidas externas siempre y cuando CS este en bajo. Si CS esta en alto, los buffers de salida se encuentran en el estado de alta impedancia, con lo que D7 asta D0 estarán flotando 0. CELDA DE ROM CONCLUSION La memoria RAM normalmente es más rápida para lectura que la mayoría de las memorias ROM, por lo tanto el contenido ROM se suele traspasar normalmente a la memoria RAM cuando se utiliza. Distinto de la memoria principal (RAM), la ROM conserva su contenido incluso cuando el ordenador se apaga. ROM se refiere como siendo permanente, mientras que la RAM es volátil