PRINCIPIOS

DIGITALES

,

Roger L. Tokheim

TERCERA EDICION

•...••

609 problemas resueltos,

desarrollados

resueltos, perfectamente desarrollados

---

--~---

430 problemas suplementarios, que contribuyen aa la

consolidación

consolidación de los conocimientos adquiridos

adquiridos

•

Proporciona la información

información necesaria para que el lector

pueda resolver los problemos

problemas de electrónica digital

digital que

puedan presentarse como esíudioníe,

estudiante, técnico oo ingeniero

ingeniero

•

PRINCIPIOS

PRINCIPIOS

DIGITALES

DIGITALES

Tercera edición

Tercera

CONSULTORES EDITORIALES

EDITORIALES

CONSULTORES

AREA DE INFORMATICA

INFORMATICA yy COMPUTACION

COMPUTACION

Antonio Vaquero

Vaquero Sánchez

Sánchez

Antonio

Catedrático de Lenguajes

Lenguajes y Sistemas

Sistemas Informáticos

Informáticos

Catedrático

Escuela Superior

Superior de Informática

Informática

Escuela

Universidad Complutense

Complutense de Madrid

Madrid

Universidad

ESPAÑA

ESPAÑA

Gerardo Quiroz

Quiroz Vieyra

Vieyra

Gerardo

Ingeniero en Comunicaciones

Comunicaciones y Electrónica

Electrónica

Ingeniero

ESIME del Instituto

Instituto Politécnico

Politécnico Nacional

Nacional

por la ESIME

Profesor de la Universidad

Universidad Autónoma

Autónoma Metropolitana

Metropolitana

Profesor

Unidad Xochimilco

Xochimilco

Unidad

MEXICO

MEXICO

Traduci

JUj

Dep

Facl

Uni

Revisió

AN

Cate

Escl

Uni

IV

NUEVA Y

•

p

PRINCIPIOS

PRINCIPIOS

DIGITALES

DIGITALES

Tercera edición

ROGER L. TOKHEIM

TOKHEIM

ROGER

Henry

Henry Sibley

Sibley High

High School

School

Mendota

Mendota Heights,

Heights, Minnesota

Minnesota

Traducción:

JUAN

JUAN MANUEL

MANUEL SANCHEZ

SANCHEZ

Departamento

Informática y Automática

Departamento

de Informática

Automática

Facultad

Ciencias Físicas

Físicas

Facultad de Ciencias

Universidad Complutense

Madrid

Universidad

Complutense de Madrid

Revisión

Revisión técnica:

ANTONIO

VAQUERO SANCHEZ

SANCHEZ

ANTONIO VAQUERO

Catedrático de Lenguajes

Lenguajes y Sistemas

Sistemas Informáticos

Informáticos

Catedrático

Escuela

Escuela Superior

Superior de Informática

Informática

Universidad Complutense

Universidad

Complutense de Madrid

Madrid

McGraw-Hill

McGraw-Hill

MADRID.

AIRES. CARACAS.

MADRID. BUENOS

BUENOS AIRES.

CARACAS. GUATEMALA.

GUATEMALA. LISBOA.

LISBOA. MEXICO

NUEVA YORK.

YORK. PANAMA.

PANAMA. SAN JUAN.

JUAN. SANTAFE DE

DE BOGOTA.

BOGOTA. SANTIAGO.

SANTIAGO. SAO PAULO

PAULO

AUCKLAND

AUCKLAND • HAMBURGO

HAMBURGO • LONDRES.

LONDRES. MILAN

MILAN • MONTREAL

MONTREAL • NUEVA

NUEVA DELHI

DELHI

PARIS.

ANC ISCO . SIDNEY • SINGAPUR • STo

NTa

PARIS. SAN

SAN FR

FRANCISCO.

STo LUIS.

LUIS. TOKIO.

TOKIO. TaRa

TORONTO

Capítulo 1.

Capítulo 2.

PRINCIPIOS

PRINCIPIOS DIGITALES

DIGITALES (Tercera

(Tercera edición)

edición)

No

No está permitida

permitida la reproducción

reproducción total

total o parcial

parcial de este libro,

libro, ni su tratamiento

tratamiento

informático,

informático, ni la transmisión

transmisión de ninguna

ninguna forma

forma o por

por cualquier

cualquier medio,

medio, ya sea

sea

electrónico,

electrónico, mecánico,

mecánico, por

por fotocopia,

fotocopia, por

por registro

registro uu otros

otros métodos,

métodos, sin el permiso

permiso

previo

previo yy por

por escrito

escrito de los titulares

titulares del Copyright.

Copyright.

Capítulo 3.

DERECHOS

1995, respecto

respecto aa la

la segunda

segunda edición

edición 'en

'en español,

español, por

por

DERECHOS RESERVADOS

RESERVADOS © 1995,

McGRAW-HILLjINTERAMERICANA

McGRAW-HILLjINTERAMERICANA DE

DE ESPAÑA,

ESPAÑA, S.

S. A.

A. U.

Edificio

Edificio Valrealty,

Valrealty, l."

La planta

planta

Basauri,

Basauri, 17

17

28023

28023 Aravaca

Aravaca (Madrid)

(Madrid)

Traducido

Traducido de

de la

la tercera

tercera edición

edición en

en inglés

inglés de

de

DIGITAL

DIGITAL PRINCIPLES

PRINOPLES

Copyright

© MCMXCIV,

MCMXCIV, por

por McGraw-Hill,

McGraw-Hill, Inc.

Inc.

Copyright ©

ISBN:

ISBN: 0-07-065050-0

0-07-065050-0

ISBN:

ISBN: 84-481-1737-9

84-481 - 1737-9

Depósito

Depósito legal:

legal: M.49.967-2000

M. 49.967-2000

Editor

Editor de

de lala edición

edición en

en español:

español: Andrés

Andrés Otero

Otero

Compuesto

Compuesto en:

en: FER,

FER, Fotocomposición,

Fotocomposición, S.

S. A.

A.

Impreso

Impreso en:

en: Lavel,

Lavel, S.

S. A.

A.

IMPRESO

IMPRESO EN

EN ESPAÑA

ESPAÑA -- PRINTED

PRINTED IN

IN SPAIN

SPAIN

Capítulo 4.

CONTENIDO

CONTENIDO

PROLOGO

PROLOGO

Capítulo 1.

Capítulo

NUMERO S UTILIZADOS

UTILIZADOS EN ELECfRONICA

ELECfRONICA DIGITAL .........

NUMERO

1.1.

1.1.

1.2.

1.2.

1.3.

1.3.

1.4.

lA.

Capítulo

Capítulo 2.

2.

1

1

7

11

11

CODIGOS

CODIGOS BINARIOS . ...... ... ..... .. . ..........................

18

Introducción ........ .... ............................. .... ....

Códigos

Códigos binarios con peso

peso .. .. ........... ..... .. . ...... . . ......

Códigos binarios sin peso .....................................

Códigos

Códigos

Códigos alfanuméricos

alfanuméricos ........................................

18

18

18

18

22

22

27

27

PUERTAS

PUERTAS LOGICAS BASICAS ........ ... ...... ... .. ... ... ... ....

32

3.1.

3.1.

3.2.

3.2.

3.3.

3.3.

3.4.

304.

3.5.

3.5.

3.6.

3.6.

Capítulo

Capítulo 4.

4.

1

Introducción ..... .. .......................... .. ............ . .

Números binarios ...... . ............................... ... .. .

Números hexadecimales

hexadecimales ..... .. ............. . ........... .. .....

Números en complemento a 2 ................... . .............

2.1.

2.1.

2.2.

2.2.

2.3.

2.3.

204.

2.4.

Capítulo

Capítulo 3.

ix

Introducción .................................................

La puerta AND .......................... ..... .......... . ....

La puerta OR .... ... ....... ..... .... ........ .. ..............

La puerta NOT ........... . . . . .. ........... . . ........ ..... ...

Combinación de puertas lógicas

lógicas ......... ... .. ... ....... . . .. ....

lógicas prácticas

prácticas ..........................

Utilización de puertas lógicas

32

32

32

36

36

39

39

41

41

45

45

OTRAS PUERTAS

PUERTAS LOGICAS ............ .................... ... ..

54

4.1.

4.1.

4.2.

4.2.

4.3.

4.3.

4.4.

404.

4.5.

4.5.

4.6.

4.6.

4.7.

4.7.

4.8.

4.8.

Introducción .................................................

La puerta NAND .... .................. . .....................

La puerta NOR ... ... .. ... .............................. . ....

exclusiva .......... . ............................

La puerta OR exclusiva

exclusiva ........ . ........... . .... ............

La puerta NOR exclusiva

Conversión de puertas utilizando inversores

inversores .......... . ...... . .. . .

Conversión

NAND como puerta universal

universal ..... .. .. .... ... ... .. ............

lógicas prácticas

prácticas ..........................

Utilización de puertas lógicas

54

54

54

54

57

57

58

58

61

61

62

62

66

66

68

68

v

-----------------------------------------------------------------------------~---vi

CONTENIDO

Capítulo 5.

Capítulo 6.

Capítulo 7.

SIMPLIFICACION DE CIRCUITOS LOGICOS: DIAGRAMAS

5.1. Introducción

.5.2. Expresiones booleanas en forma de suma de productos

5.3. Expresiones booleanas en forma de producto de sumas

5.4. Utilización de los teoremas de De Morgan

5.5. Utilización de la lógica NAND

5.6. Utilización de la lógica NOR

5.7. Diagramas de Karnaugh

5.8. Diagramas de Karnaugh con cuatro variables

5.9. Utilización de diagramas con expresiones en forma de maxterms

5.10. Términos irrelevantes en los diagramas de Karnaugh

5.11. Diagramas de Karnaugh con cinco variables

78

78

79

81

85

87

90

93

96

100

104

106

CIRCUITOS INTEGRADOS TTL Y CMOS: CARACTERISTICAS

E INTERFACE S

6.1. Introducción

6.2. Términos de los CI digitales

"'........

6.3. Circuitos integrados TTL

6.4. Circuitos integrados CMOS

6.5. Interfaces entre CI TTL y CMOS

6.6. Interconexión TTL y CMOS con conmutadores. . . . . . . . . . . . . . . . ..

6.7. Interconexión (interfaz) TTLjCMOS con dispositivos de salida

6.8. Conversión DjA y AjD

117

117

118

123

128

133

141

145

148

CONVERSION DE CODIGOS

7.1. Introducción

7.2. Codificación

7.3. Decodificación: BCD a decimal

7.4. Decodificación: BCD a código de siete segmentos

7.5. Visualizadores de cristal líquido

7.6. Controladores de LCD

7.7. Visualizadores fluorescentes de vacío

7.8. Control de visualizadores VF con CMOS

. 158

. 158

. 159

. 162

. 166

. 172

. 175

. 179

. 183

Capítulo 9.

Capítulo 10. (

1

1

1

1

1

1

1

Capítulo 11. I

I

I

I

I

I

Capítulo 12.

Capítulo 8.

CIRCUITOS ARITMETICOS y ARITMETICA BINARIA

8.1. Introducción

8.2. Suma binaria

8.3. Resta binaria

8.4. Sumadores y restadores paralelos

8.5. Utilización de sumadores completos

. 192

. 192

. 192

. 197

. 202

. 209

CONTENIDO

78

78

79

81

85

87

90

93

96

100

104

106

Capítulo 9.

Capítulo

vii

Utilización de sumadores

sumadores para la resta ........ . .......... .. .....

8.6. Utilización

complemento a 2 ............... . ....... . .. ...

8.7. Suma y resta en complemento

212

217

FLIP-FLOPS y

y OTROS

OTROS MUL

MUL TIVIBRADORES

TIVIBRADORES ....................

FLIP-FLOPS

Introducción . . .... . ....... . .................... . .... . ........

9.1. Introducción

RS .. ........... .. ....... ......... ..... .............

99.2.

. 2. Flip-flop RS

RS síncrono

síncrono ............ .... . .... .. . .. ........... . ...

9.3. Flip-flop RS

D . ......................... .. .................. . ...

9.4. Flip-flop D

9.5.. Flip-flop JK

JK ...... .. .. .. ....... . .............................

9.5

flip-flops . ........... . ... .. ......... ... ..... ....

9.6. Disparo de los flip-flops

Multivibradores astables: relojes ...... .. . ......... . . .......... . .

9.7. Multivibradores

Multivibradores monoestables

monoestables . ........... .. ....................

9.8. Multivibradores

230

230

230

233

236

239

244

249

253

AS

117

117

118

123

128

133

141

145

148

158

158

159

162

166

172

175

179

183

192

192

192

197

202

209

Capítulo 10. CONTADORES

CONTADORES .... ... ... . ..... . .... ... .... .. ............. ........ 260

Capítulo

10.1. Introducción

10.1.

Introducción . ...... .. ...................... . ........... . . . ... 260

10.2. Contadores

Contadores de rizado .. .. ... ............. . . .. .......... .. ..... 260

10.2.

10.3. Contadores

Contadores paralelos . . ........... .. ........................... 264

10.3.

10.4. Otros contadores

contadores. . ............

. . . . . . . . . . . . . ...............

. . . . . . . . . . . . . . . ..

. . ..............

. . . . . . . . . . . . .. 267

10.4.

10.5. Contadores

Contadores con CI TTL

TTL ... ... ........ . . .... ... ...... . ...... . .. 272

10.5.

10.6. Contadores

Contadores con CI CMOS ... ... .. ... .. ........................ 278

10.6.

10.7. División de frecuencia: el reloj digital .... ... .... ... ·. ..... .. ..... 284

10.7.

Capítulo 11. REGISTROS

REGISTROS DE DESPLAZAMIENTO

DESPLAZAMIENTO ..... .. .. ........ ... .. .... ..

Capítulo

11.1. Introducción

Introducción . .. . ........... ... ... .. ............. . ............

11.1.

11.2. Registro de desplazamiento

desplazamiento de carga serie .. ................ ... ..

11.2.

11.3. Registro de desplazamiento

desplazamiento de carga paralelo .......... .. ..... .. .

11.3.

11.4. Registros de desplazamiento

desplazamiento TTL

TTL . ..... . .................. . ....

11.4.

11.5. Registros de desplazamiento

desplazamiento CMOS .. ..... . ............ .. .......

11.5.

295

295

295

300

305

309

Capítulo 12. MEMORIAS

MICROCOMPUTADORA . .... ... .. ..........

Capítulo

MEMORIAS DE LA MICROCOMPUTADORA

12.1. Introducción

12.1.

Introducción ..... . ....................... . ...................

12.2. Memoria

Memoria de acceso aleatorio (RAM) ...................... . .....

12.2.

12.3. Memoria

Memoria de sólo lectura (ROM) ... ..... .. .....................

12.3.

12.4. Memoria

Memoria programable

programable de sólo lectura

lectura ................ . .. . ...... .

12.4.

12.5. Memorias

Memorias masivas de la microcomputadora

microcomputadora ..... . ......... . .....

12.5.

317

317

317

326

333

341

341

viii

CONTENIDO

Capítulo

Capítulo 13. OTROS

OTROS DISPOSITIVOS

DISPOSITIVOS Y TECNICAS

TECNICAS

.

13.1.

13.1. Introducción

Introducción .......................... .. ......................

13.2. Selectores

.13.2.

Se1ectores de datos/Multiplexores

datosjMultiplexores ......... ... .... ..... .. .........

13.3.

13.3. Visualizar la multiplexación

multiplexación . .. ... .. . .. . .... .... .. .... ..... .....

13.4.

13.4. Demultiplexores

Demultiplexores ........ . ..... ..... ................... . .... ....

13.5.

13.5. Cerrojos y buffers

butTers de tres estados ...............................

13.6.

13.6. Transmisión

Transmisión digital de datos ....................................

13.7.

13.7. Arrays lógicos programables

programables ....................................

13.8.

13.8. Comparadores

Comparadores de magnitud

magnitud .....................................

13.9. Dispositivos disparadores

disparadores Schmitt

Schmitt ................................

13.9.

INDICE

INDICE

352

352

352

357

360

363

369

372

381

381

388

395

395

La electrónic

usan en gran

de oficina e

el resultado 1

tecnologías d(

Este libro

problemas de

o aficionado.

Schaum se b

digital media

1.000 probler

La tercera

que las dos 1=

para reflejar 1

y PMOS. Se

putadoras, ref

de o con la e

CMOS y TT

también algui

(LCD) y los

microcompuu

También se h

de magnitud,

Los tópic

coincidiesen (

colegio. Se a

utilizados en

similares a lo

Principios

numeración

combinaciona

de visualizadc

también divei

y lógica secue

se exploran la

sobre multipl

comparadores

El libro hace

para que el

digital. La m,

estándares.

352

352

352

357

360

363

369

372

381

388

......

395

PROLOGO

PROLOGO

La electrónica

electrónica digital

digital es una

una tecnología

tecnología en rápido

rápido creCImIento.

crecimiento. Los circuitos

circuitos digitales

digitales se

usan en gran

control,

gran cantidad

cantidad de nuevos

nuevos productos

productos de consumo,

consumo, equipos

equipos industriales

industriales y control,

de oficina

oficina e incluso

incluso de comunicaciones.

comunicaciones. Este uso expansivo

expansivo de los circuitos

circuitos digitales

digitales es

el resultado

resultado del desarrollo

desarrollo de circuitos

circuitos integrados

integrados a bajo

bajo precio

precio y la aplicación

aplicación de las

tecnologías de memorias

computadoras y de visualizadores.

visualizadores.

tecnologías

memorias de computadoras

resolver los

Este libro

libro proporciona

proporciona la información

información necesaria

necesaria para

para que

que el lector

lector pueda

pueda resolver

problemas de electrónica

electrónica digital

digital que

que se puede

puede encontrar

encontrar como

como estudiante,

estudiante, técnico,

técnico, ingeniero

ingeniero

problemas

o aficionado.

materia son necesarios,

aficionado. Aunque

Aunque los principios

principios de la materia

necesarios, la filosofía

filosofía de la Serie

basa en mostrar

Schaum

Schaum se basa

mostrar al estudiante

estudiante cómo

cómo aplicar

aplicar los principios

principios de la electrónica

electrónica

digital mediante

prácticos resueltos.

ahora unos

unos

mediante problemas

problemas prácticos

resueltos. Esta

Esta nueva

nueva edición

edición contiene

contiene ahora

problemas resueltos

suplementarios.

1.000 problemas

resueltos y suplementarios.

La tercera

tercera edición

mismos tópicos

que hicieron

edición de este libro

libro contiene

contiene muchos

muchos de los mismos

tópicos que

hicieron

ediciones alcanzasen

ligeros cambios

cambios

que las dos primeras

primeras ediciones

alcanzasen gran

gran éxito.

éxito. Se han

han introducido

introducido ligeros

para

utilizando más

más circuitos

integrados CMOS,

NMOS

para reflejar

reflejar las tendencias

tendencias tecnológicas

tecnológicas utilizando

circuitos integrados

CMOS, NMOS

cuestiones relativas

relativas a microprocesadores/microcornmicroprocesadoresjmicrocomy PMOS.

PMOS. Se han

han introducido

introducido algunas

algunas cuestiones

putadoras, reflejando

práctica actual

actual de enseñar

un curso

después

putadoras,

reflejando la práctica

enseñar un

curso de microprocesadores

microprocesadores después

de o con

electrónica digital.

con la electrónica

digital. Además

Además de las secciones

secciones que

que tratan

tratan sobre

sobre las características

características

ha añadido

añadido una

una sección

interfaces CMOS-TTL.

incluyen

CMOS y TTL,

CMOS

TTL, se ha

sección para

para las interfaces

CMOS-TTL. Se incluyen

también

algunas tecnologías

tecnologías de visual

visualizadores,

como los visualizadores

visualizadores de cristal

cristal líquido

líquido

también algunas

izado res, como

capítulo sobre

sobre la memoria

memoria de la

(LCD) y los

los visualizadores

visualizadores fluorescentes

fluorescentes de vacío.

vacío. El capítulo

(LCD)

ha revisado

revisado y se ha

ha aumentado

aumentado con

con los discos

discos ópticos

ópticos y rígidos.

rígidos.

microcomputadora se ha

microcomputadora

han añadido

añadido secciones

secciones sobre

sobre arrays

arrays lógicos

lógicos programables

programables (PLA),

(PLA), comparadores

comparadores

También se han

También

de magnitud,

Schmitt.

magnitud, demultiplexores

demultiplexores y dispositivos

dispositivos disparadores

disparadores Schmitt.

seleccionaron cuidadosamente

cuidadosamente para

para que

que

Los tópicos

tópicos esbozados

esbozados en

en este

este libro

libro se seleccionaron

Los

coincidiesen con

con los impartidos

impartidos en

en escuelas

escuelas de nivel

nivel superior,

superior, profesionales

profesionales y a nivel

nivel de

de

coincidiesen

analizaron diversos

diversos libros

libros de texto

texto y manuales

manuales de laboratorio

laboratorio de

de los más

más

colegio. Se analizaron

utilizados

utilizados en electrónica

electrónica digital.

digital. Los

Los tópicos

tópicos y problemas

problemas incluidos

incluidos en este

este libro

libro son

son

similares

similares a los encontrados

encontrados en

en estos

estos libros

libros estándares.

estándares.

Principios digitales

digitales de la Serie

Serie Schaum,

Schaum, 3.aa edición,

edición, comienza

comienza con

con sistemas

sistemas de

de

Principios

numeración

numeración y códigos

códigos digitales

digitales y continúa

continúa con

con puertas

puertas lógicas

lógicas y circuitos

circuitos lógicos

lógicos

combinacionales.

combinacionales. A continuación

continuación se exploran

exploran codificadores,

codificadores, decodificadores

decodificadores y controladores

controladores

de visualizadores,

visualizadores, junto

junto a los LED,

LED, LCD

LCD y visualizadores

visualizadores de

de siete

siete segmentos.

segmentos. Se examinan

examinan

también

cubren flip-flops,

tlip-flops, otros

otros multivibradores

multivibradores

también diversos

diversos circuitos

circuitos aritméticos.

aritméticos. Después

Después se cubren

yy lógica

lógica secuencial,

secuencial, seguido

seguido por

por contadores

contadores y registros

registros de

de desplazamiento.

desplazamiento. A

A continuación

continuación

se exploran

exploran las memorias

memorias de semiconductores

semiconductores y de

de gran

gran capacidad.

capacidad. Finalmente

Finalmente se investiga

investiga

sobre

sobre multiplexores,

multiplexores, demultiplexores,

demultiplexores, cerrojos

cerrojos yy «buffers»,

«buffers», transmisión

transmisión digital

digital de

de datos,

datos,

comparadores

comparadores de

de magnitud,

magnitud, dispositivos

dispositivos disparadores

disparadores Schmitt

Schmitt yy arrays

arrays lógicos

lógicos programables.

programables.

El libro

libro hace

hace énfasis

énfasis en

en el uso

uso de

de CI

CI digitales

digitales estándares

estándares en

en la

la industria

industria (TTL

(TTL yy CMOS)

CMOS)

para

lector se familiarice

familiarice con

con aspectos

aspectos prácticos

prácticos del

del hardware

hardware de

de la

la electrónica

electrónica

para que

que el lector

digital.

digital. La

La mayoría

mayoría de

de los

los circuitos

circuitos de

de este

este libro

libro pueden

pueden construirse

construirse utilizando

utilizando CI

CI digitales

digitales

estándares.

.

estándares.

ix

r==============================================--------------------------------x

PROLOGO

PROLOGO

Deseo

Deseo agradecer

agradecer a mi hijo Marshall

Marshall sus muchas

muchas horas

horas de mecanografiado,

mecanografiado, lectura

lectura de

pruebas

pruebas y test de los circuitos

circuitos para

para que

que este libro

libro sea lo más

más preciso

preciso posible.

posible. Finalmente,

Finalmente,

extiendo

extiendo mi agradecimiento

agradecimiento a los demás

demás miembros

miembros de mi familia,

familia, Daniel

Daniel y Carrie,

Carrie, por

por

ayuda y paciencia.

paciencia.

su ayuda

ROGER L. TOKHEIM

TOKHEIM

ROGER

..

El sistema d:

símbolos 0, 1

valor por po.

de las unidad:

30 unidades.

Sumando 200

decimal taml

símbolos dife

«base» son té

Los núme

ras. Los núrr

representar g

considerable

Todos los

pueden utiliz

posición.

1.2.

NUMl

El sistema de

una raíz 2 y e

se denomina

Contar en

con su equiva

En otras pala

La segunda f

en la fila de 1

tres valores (

y 16). Obsen

realmente es

en electrónicr

1111 (que se

Capítulo

Capítulo 1

ctura de

almente,

e, por

NUMERaS

NUMERaS UTILIZADOS

UTILIZADOS

EN ELECTRONICA

ElECTRONICA DIGITAL

DIGITAl

EN

1.1.

INTRODUCCION

INTRODUCCION

El sistema

numeración decimal

todo el mundo.

mundo. Este

Este sistema

utiliza los

sistema de numeración

decimal es familiar

familiar a todo

sistema utiliza

símbolos

también tiene

tiene una

una característica

símbolos O, 1, 2, 3, 4, 5, 6, 7, 8 Y 9. El sistema

sistema decimal

decimal también

característica de

valor

número decimal

posición o lugar

lugar

valor por

por posición.

posición. Considérese

Considérese el número

decimal 238. El 8 está

está en la posición

de las unidades.

por tanto,

tanto, las tres

tres decenas

unidades. El 3 está

está en la posición

posición de las decenas

decenas y, por

decenas significan

significan

30 unidades.

200 unidades.

unidades.

unidades. El 2 está en la posición

posición de las centenas

centenas y significa

significa dos

dos centenas,

centenas, o 200

Sumando

número decimal

total de 238.

238. El sistema

numeración

Sumando 200

200 + 30 + 8 se obtiene

obtiene el número

decimal total

sistema de numeración

decimal

base 10 porque

porque tiene

tiene diez

decimal también

también se llama

llama sistema de base 10.

10. Se denomina

denomina de base

símbolos

base 10 tiene

tiene una

una raíz

raíz 10. «Raíz»

símbolos diferentes.

diferentes. También

También se dice que

que el sistema

sistema de base

«Raíz» y

«base»

mismo.

«base» son términos

términos que significan

significan exactamente

exactamente 10

lo mismo.

utilizan mucho

mucho en electrónica

Los números

números binarios

binarios (base

(base 2) se utilizan

electrónica digital

digital y en

en computadocomputadoutilizados para

para

ras. Los

Los números

números del sistema

sistema hexadecimal

hexadecimal (base

(base 16) y octal

octal (base

(base 8) son

son utilizados

representar

Los números

números binarios

binarios y hexadecimales

hexadecimales tienen

tienen un

un

representar grupos

grupos de dígitos

dígitos binarios.

binarios. Los

considerable

microcomputadoras.

considerable uso

uso en las modernas

modernas microcomputadoras.

Todos

mencionados (decimal,

binario, octal

hexadecimal)

Todos los sistemas

sistemas de numeración

numeración mencionados

(decimal, binario,

octal y hexadecimal)

pueden utilizarse

utilizarse para

para contar.

contar. También

También tienen

característica

pueden

tienen todos

todos una

una característica

de valor

valor por

por

posición.

posición.

1.2.

NUMERO S BINARIOS

BINARIOS

NUMERO

El sistema

utiliza solamente

tiene

sistema de numeración

numeración binario

binario utiliza

solamente dos

dos símbolos

símbolos (O, 1). Se dice

dice que

que tiene

una raíz

raíz 2 y comúnmente

comúnmente se denomina

denomina sistema

Cada dígito

una

sistema de numeración

numeración en base 2. Cada

dígito binario

binario

se denomina

denomina bit.

Contar en binario

binario se ilustra

ilustra en la Figura

derecha

Contar

Figura 1.1. El número

número binario

binario se muestra

muestra a la derecha

menos significativo

significativo (LSB)

posición del 1.

con

que el bit menos

con su equivalente

equivalente decimal.

decimal. Observar

Observar que

(LSB) es la posición

l.

En otras

un 1 a la cuenta

binaria.

otras palabras,

palabras, si aparece

aparece un 1 en la columna

columna derecha,

derecha, se suma

suma un

cuenta binaria.

La

Un 1 en esta

La segJ.lnda

segunda posición

posición a partir

partir de la derecha

derecha es el lugar

lugar del 2. Un

esta columna

columna (como

(como

en la fila de las decenas

cuenta se suma

un 2. Los

Los otros

decenas en los decimales)

decimales) significa

significa que

que a la cuenta

suma un

otros

tres valores

muestran en

Figura 1.1

valores de las posiciones

posiciones también

también se muestran

en la Figura

1.1 (posiciones

(posiciones del 4, 8

y 16). Observar

una potencia

potencia de 2. La 'posición

Observar que

que a cada

cada posición

posición se le asigna

asigna una

'posición del 1

1

realmente es 2°, la del 2 es 2

21,

costumbre

realmente

, la del 4 es 22,

22 , la del 8 es 233,, y la del 16 es 24.

24 . Es costumbre

en electrónica

menos, la secuencia

binaria desde

hasta

electrónica digital

digital memorizar,

memorizar, al menos,

secuencia de cuenta

cuenta binaria

desde 0000

0000 hasta

1111 (que

uno, uno)

uno) o decimal

(que se pronuncia,

pronuncia, uno,

uno, uno,

uno, uno,

decimal 15.

1

2

TEORIA

DE PROBLEMAS

DE PRINCIPIOS

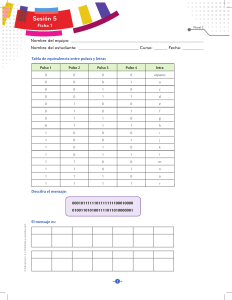

Cuenta

decimal

DIGITALES

Cuenta

Potencias de 2

binaria

1

Valor de la

posición

O

O

Binario

1

1

16

8

4

2

1

2

3

O

1

1

O

1

O

O

6

1

1

O

7

1

1

1

O

O

O

1

O

1

1

O

O

4

1

5

8

1

9

1

10

1

11

1

O

O

O

O

12

1

1

13

1

1

O

O

14

1

1

1

15

1

1

1

1

1

O

O

O

1

O

1

O

O

O

O

1

1

24

23

22

21

2°

1

17

1

18

1

19

Potencias

Potencias de 2

Valor de la

posición

Binario

Decimal

(e) Re

1

O

O

O

O

16

Figura 1.1.

1

Decimal

1

de 2

Contar en binario y decimal.

Considerar el número mostrado en la Figura 1.2a. Esta figura muestra cómo convertir

el binario 10011 (uno, cero, cero, uno, uno) a su decimal equivalente. Observar que, para

cada bit I del número binario, se escribe debajo el decimal equivalente de esa posición. Los

números decimales se suman después (16 + 2 + I = 19) para obtener el decimal equivalente.

El binario 10011 es igual al decimal 19.

Considerar el número binario 101110 de la Figura 1.2b. Utilizando el mismo procedimiento, cada bit I del número binario genera un decimal equivalente según la posición

que ocupe. El bit más significativo (MSB) del número binario es 32. Sumar 8 más 4 más 2

a 32 da un total de 46. El número binario 101110, entonces, es igual al decimal 46. La Figura 1.2b también identifica el punto binario (similar al punto decimal en los números decimales). Es costumbre omitir el punto binario cuando se trabaja con números binarios enteros.

¿Cuál es el valor del número III? Podría ser ciento once en decimal o uno, uno, uno

en binario. Algunos libros utilizan el sistema mostrado en la Figura 1.2c para designar la

base, o raíz, de

pequeño subínc

muestra el subír

binario-decimal

¿Cómo se cc

el número bina!

aparecen en la

binario. El pro

enteros. El valo

número decima

Potencias de .

Valor de la

posición

Binario

Decimal

Convertir el

realizar esta ca

resto de l. El re

----------~--------------------------------------------------------------------~

NUMEROS UTILIZADOS EN ELECTRONICA DIGITAL

Potencias de 2

24

23

22

21

2°

Valor de la

posición

16

8

4

2

I

Binario

1

o

o

1

1

Decimal

16

+

(a)

2

+

binario

19

Conversión binario-decimal

Potencias de 2

25

24

23

22

21

2°

Valor de la

posición

32

16

8

4

2

1

Binario

1

o

1

1

1

o

32

+

Decimal

• -Punto

3

+

8

4

+

<--Punto

binario

46

2

(b) Conversión binario-decirnal

100112

(e)

=

1910

1011102

= 4610

Resumen de conversiones y uso de pequeños subíndices para indicar la base del número

Figura 1.2.

base, o raíz, de un número. En este caso 10011 es un número en base 2 como muestra el

pequeño subíndice 2 detrás del número. El número 19 es un número en base 10 como

muestra el subíndice 10 detrás del número. La Figura 1.2c es un resumen de las conversiones

binario-decimal de la Figura 1.2a y b.

¿Cómo se convierten los números fraccionario s? La Figura 1.3 ilustra cómo se convierte

el número binario 1110.101 a su decimal equivalente. Los valores asignados a cada posición

aparecen en la parte superior. Obs.ervar el valor de cada posición a la derecha del punto

binario. El procedimiento para realizar la conversión es el mismo que con los números

enteros. El valor de la posición de cada bit 1 del número binario se suma para formar el

número decimal. En este problema 8 + 4 + 2 + 0.5 + 0.125 = 14.625 en decimal.

mo convertir

ar que, para

osición. Los

equivalente.

ismo procela posición

más 4 más 2

46. La Figueras decimarios enteros.

o, uno, uno

designar la

23

22

21

2°

1/21

1/22

1/23

Valor de la

posición

8

4

2

l

0.5

0.25

0.125

Binario

1

1

1

o

o

1

Decimal

8

2

+

Potencias de 2

+

4

+

Figura 1.3.

1

0.5

+

0.125

14.625

Conversión binario-decimal.

Convertir el número 87 a binario. La Figura lA muestra un método adecuado para

realizar esta conversión. El número decimal 87 se divide primero por 2, dando 43 con un

resto de l. El resto es importante y se anota a la derecha. Se convierte en el LSB (bit menos

4

TEORIA DE PROBLEMAS DE PRINCIPIOS DIGITALES

significativo) del número binario. El cociente (43) entonces es transferido, como muestra la

flecha, y se convierte en dividendo. Los cocientes son divididos, repetidamente, por 2 hasta

que el cociente es O con un resto de 1, como en la última línea de la Figura 1.4. En la parte

inferior de la figura aparece el decimal 87 igual al binario 1010111.

LSU

8710

-i-

2 = 43 resto de 1

1

.¡;

43

-i-

2 = 21 resto de 1

I

,¡:

21-:-2=10

f

10 -i- 2

=

resto de 1

I

5 resto de O

.¡:

1

5-:-2=

2 resto de 1

I

.¡;

2-:-2=

~

La Figura 1

nuevo que 0.8,

formando el n

problema mues

Considerar '

dos procesos. L

superior de la 1

del número dec

La parte fraccic

Las secciones e

1-:-2=

resto de O

O resto de 1

8710

Figura 1.4.

=

~

1 O

1 O

1 1 12

Conversión decimal-binario.

Convertir el número decimal 0.375 a binario. La Figura 1.5a ilustra un método para

realizar esta tarea. Observar que el número decimal (0.375) se multiplica por 2. Esto da un

producto de 0.75. El O del lugar entero (posición de las unidades) se convierte en el bit más

próximo al punto binario. El 0.75 es entonces multiplicado por 2, dando 1.50. El arrastre

de 1 a la parte entera (posición de las unidades) es el siguiente bit del número binario. El

0.50 se multiplica entonces por 2, dando un producto de 1.00. El arrastre de 1 a la parte

entera es el 1 final del número binarío. Cuando el producto es 1.00, finaliza el proceso

de conversión. La Figura 1.5a muestra el decimal 0.375 convertido en su equivalente binarío 0.011.

1.1.

0.84375 x 2 = 1.6875

,

Solución:

1

0.6875

!

I

0.3 75

0.375 x :2 = 0.75

1

0.75

!

x

0.7 5

2 = 1.50

!

!

0.50

x:2

=

1.00

0.37510

1

=

.0 1 12

0.5O

El sister

x 2 = 1.375

!

1.2.

x 2 = 0.75

I

Figura 1.5.

Cuando

SI

Solución:

Bit sign

x 2 = 1.50

I

x 2 = 1.00

0.8437510

1

=

(b)

(a)

El sistema

Conversiones de fraccionario decimal a binario.

1.3.

¿Cómo se

Solución:

El núrn

.1 1 O 1 12

1.4.

El númer

Solución:

El núrr

NUMEROS UTILIZADOS

NUMEROS

UTILIZADOS EN ELECTRONICA

ELECTRONICA DIGITAL

DIGIT AL

5

binario. Observar

La Figura

Figura 1.5b muestra

muestra el número

número decimal

decimal 0.84375

0.84375 convertido

convertido en binario.

Observar de

nuevo

por 2. El entero

producto se coloca

nuevo que

que 0.84375

0.84375 se multiplica

multiplica por

entero de cada

cada producto

coloca debajo,

debajo,

formando

número binario.

binario. Cuando

producto es 1.00, finaliza

formando. .el número

Cuando el producto

finaliza la conversión.

conversión. Este

Este

problema

muestra el decimal

decimal 0.84375

0.84375 convertido

convertido en el binario

0.11011.

binario 0.1101l.

problema muestra

Considerar

involucra

Considerar el número

número decimal

decimal 5.625.

5.625. La conversión

conversión de este número

número binario

binario involucra

dos procesos.

procesos. La parte

parte entera

procesada por

por división

parte

entera del número

número (5)

(5) es procesada

división repetida

repetida en la parte

superior

Figura 1.

1.6.

decimal 5 se con

convierte

10 1. La parte

su

perior de la Figura

6. El decimal

vierte en el binario

binario 101.

parte fraccionaria

fraccionaria

número decimal

decimal (.625)

(.625) es convertida

convertida al binario

inferior de la Figura

Figura 1.6.

del número

binario .10 1 en la parte

parte inferior

fraccionaria es convertida

convertida a binario

multiplicación repetida.

repetida.

La parte

parte fraccionaria

binario mediante

mediante el proceso

proceso de multiplicación

secciones entera

entera y fraccionaria

fraccionaria del decimal

decimal 5.625 se juntan

dar el binario

1.

Las secciones

juntan para

para dar

binario 10 1.10 1.

5 -;-7- 2

J:.¡:

=

=

resto de

de 1_ _ _ _--.

•

2 resto

I

¡

t~::l::::::: 111

2 -7- 2 = resto de O~

.¡:

1 -7- 2 = O resto de 1

5.625 10

= 1 O 1 . 1 O 12

10 =

0.~25 x 22 == Ir'1,...'.2_(_

O.~25

para

da un

it más

rrastre

rio. El

parte

roceso

bina-

x

]1

11

_ _ _ _ _ __ _ _t ----'

----'

t

0.25

0.25 x 2 == 0.50

0.50

!!

I

,.--,

------------~

0.50 xX 2 == LOO

1.00

0.50

Figura

Figura 1.6.

Conversión

Conversión decimal

decimal a binario.

binario.

PROBLEMAS

PROBLEMAS RESUELTOS

RESUELTOS

1.1.

1.1.

El sistema

binario de numeración

base _ __ y tiene

una raíz

sistema binario

numeración es el sistema

sistema de base

tiene una

raíz de _ __

Solución:

Solución:

El sistema

binario de numeración

base 2 y tiene

una raíz

sistema binario

numeración es el sistema

sistema de base

tiene una

raíz de 2.

1.2.

Cuando

binarios, el término

bit significa

Cuando se trata

trata con

con números

números binarios,

término bit

significa ___ ___

Solución:

Solución:

Bit significa

binario.

significa dígito

dígito binario.

1.3.

¿Cómo se pronunciaría

1001 en (a) binario

(b) decimal?

decimal?

¿Cómo

pronunciaría el número

número 1001

binario y (h)

Solución:

Solución:

El número

pronuncia: (a)

uno, cero,

uno; (b) mil uno.

uno.

número 1001

1001 se pronuncia:

(a) uno,

cero, cero,

cero, uno;

1 12

1.4.

El número

base ___

número 110 10 es un

un número

número en base

oo

Solución:

Solución:

un número

base 10,

pequeño 10 detrás

El número

número 11010

número en base

lO, como

como indica

indica el pequeño

detrás del número

número. .

10 es un

66

TEORIA DE

DE PROBLEMAS

PROBLEMAS DE

DE PRINCIPIOS

PRINCIPIOS DIGITALES

DIGITALES

TEORIA

1.5. Escribir

Escribir en

en base

base 22 elel número

número uno,

uno, uno,

uno, cero,

cero, cero,

cero, uno.

uno.

1.5.

1.3. NUME

Solución:

Solución:

1100122.

11001

El sistema de

numeración

1.6.

1.6.

Convertir los

los siguientes

siguientes números

números binarios

binarios aa sus

sus equivalentes

equivalentes decimales:

decimales:

Convertir

(a) 001100,

001100,

(b) 000011

000011,,

(e) 011100,

011100,

(d) 111100,

111100,

(e) 101010,

101010,

(a)

(b)

(e)

(d)

(e)

(g)) 100001

100001,,

(h) 111000.

111000.

(g

(h)

(f)

(f)

111111

111111,,

Solución:

Solución:

Seguir el

el procedimiento

procedimiento mostrado

mostrado en

en la

la Figura

Figura 1.2.

1.2. Los

Los equivalentes

equivalentes decimales

decimales son:

son:

Seguir

(a) 001100

00110022 == 1210

1210

(e) 011100

01110022 == 28

2810

(e)

1010102 == 4210

4210

(g) 100001

10000122 = 33

3310

(a)

(e)

(e)

101010

(g)

10

10

(b) 000011

00001122=310

(d)

1111002=60

(f) 111111

1111112=63

(h) 111000

11100022=56

(b)

=3 10

(el)

111100

=60

(f)

=63

(h)

=56

10 10

10 10

10 10

1.7.

1.7.

1111000111122 = --10

11110001111

-10

Solución:

Solución:

Seguir el

el procedimiento

procedimiento mostrado

mostrado en la Figura

Figura 1.2.

Seguir

1.8.

Dec

1111000111122 = 1935 10

11110001111

10 ..

11100.01122 == --10

-10

Solución:

Solución:

Seguir el procedimiento

procedimiento mostrado

mostrado en la Figura

Figura 1.3.

Seguir

1.9.

1.9.

en

columna hexad

para el 11, la (

del sistema he)

4 bits. Observa

cuatro bits, del

11100.01122 = 28.37510

10..

110011.1001111

=--10

11001l.l00

--10

2 2 =

Solución:

Solución:

Seguir

mostrado en la·

la"Figura

Seguir el procedimiento

procedimiento mostrado

Figura 1.3.

110011.100112 2 = 51.59375

. .

110011.10011

51.593 75

1010

1010101010.122 =

--10

1.10. 1010101010.1

=-10

Solución:

Solución:

Seguir

Seguir el procedimiento

procedimiento mostrado

mostrado en

en la Figura

Figura 1.3.

1010101010.1

1010101010.12 2 = 682.5

682.510

10..

1.11. Convertir

Convertir los

los siguientes

siguientes números

números decimales

decimales a sus

sus equivalentes

equiva1.entes binarios:

binarios:

(a)

(b)

(e)

(d)

(e)

(f)

(a) 64,

64,

(b) 100,

(e) 111,

(d) 145,

(e) 255,

255,

(f) 500.

Solución:

Solución:

Seguir

Seguir el

el procedimiento

procedimiento mostrado

mostrado en

en la

la Figura

Figura lA.

1.4. Los

Los equivalentes

equivalentes binarios

binarios de

de los

los números

números decimales

decimales son:

son:

(a)

=

1000000

(e)

l

l

l

j¿

=

1101111

(e)

255

=

11111111

(a) 64

6410

=1000000

(e)

111

=1101111

(e)

255

=11111111

2

2

10

2

10

2

2

10

2

10

(b)

(d)

(f) 500

(b) 100

10010

= 1100100

(el) 145

14510

= 10010001

50010

= 111110100

2 2

2 2

2

10=111110100

2

10=10010001

10=1100100

1.12.

1.12. 34.75;0

34.75;0 == ---2

- --2

Solución:

Solución:

Seguir

Seguir el

el procedimiento

procedimiento mostrado

mostrado en

en la

la Figura

Figura 1.6.

1.6.

1.13.

=

1.13. 25.25

25.2510

10 =

34.75

34.7510

= 100010.11

100010.112.2 .

10 =

---2

---2

Solución:

Solución:

Seguir

Seguir elel procedimiento

procedimiento mostrado

mostrado en

en lala Figura

Figura 1.6.

1.6. 25.25

25 .251010 == 11001.01

11001.012.2 .

1.14.

1.14. 27.1875

27.18751010 ==

--2

--2

Solución:

Solución:

Seguir

Seguir elel procedimiento

procedimiento mostrado

mostrado en

en lala Figura

Figura 1.6.

1.6. 27.1875

27.1 875101 0 == 11011.0011

11011.00112. 2 .

Figura t.'

Observar la

hexadecimal eq

utiliza la idea,

el O significa ce

Convertir el

familiar. El 2 es

decimal. El dígi

que el hexadeci

dando 176. El

columna del 1

sumados (512-1

a 69410.

Convertir e

detalla este prc

NUMEROS UTILIZADOS EN ELEeTRONIeA

1.3.

) 111111,

DIGITAL

7

NUMERO S HEXADECIMALES

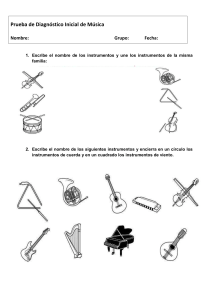

El sistema de numeración hexadecimal tiene una raíz de 16. Se denomina sistema de

numeración en base 16. Utiliza los símbolos 0-9, A, B, C, D, E Y F como se muestra en la

columna hexadecimal de la tabla de la Figura 1.7. La letra A se utiliza para ellO, la B

para el 11, la C para el 12, la D para el 13, la E para el 14, y la F para el 15. La ventaja

del sistema hexadecimal es que es útil para convertir directamente números binarios de

4 bits. Observar en la sección sombreada de la Figura 1.7 que cada número binario de

cuatro bits, del 0000 al 1111, puede ser representado por un único dígito hexadecimal.

10

10

Decimal

O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Figura 1.7.

Binario

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Hexadecimal

O

1

2

3

4

5

6

7

8

9

A

B

e

D

E

F

Decimal

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Hexadecimal

Binario

I

10000

10001

10010

10011

10100

10101

10110

10111

11000

11001

11010

11011

11100

11101

11110

11111

I

10

11

12

13

14

15

16

17

18

19

lA

lB

le

ID

lE

IF

Contar en los sistemas de numeración decimal, binario y hexadecimal.

ecimales son:

Observar. la línea que corresponde al 16 en la columna decimal de la Figura l.7. El

hexadecimal equivalente es 10. Esto muestra que el sistema de numeración hexadecimal

utiliza la idea de valor por posición. El 1 (en 1016) significa 16 unidades, mientras que

el O significa cero unidades.

Convertir el número hexadecimal 2B6 en decimal. La Figura 1.8a muestra el proceso

familiar. El 2 está en la posición del 256, por tanto 2 x 256 = 512, que se escribe en la línea

decimal. El dígito hexadecimal B aparece en la columna del 16. Observar en la Figura l.8

que el hexadecimal B corresponde al decimal 1l. Esto significa que hay once 16 (16 x l l ),

dando 176. El 176 se suma al total decimal en la parte inferior de la Figura 1.8a. La

columna del 1 muestra seis l. El 6 se suma a la línea decimal. Los valores decimales son

sumados (512 + 176 + 6 = 694), dando 69410, La Figura l.8a muestra que 2B616 es igual

a 69410,

Convertir el número hexadecimal A3F.C en su decimal equivalente. La Figura l.8b

detalla este problema. Primero considerar la columna del 256. El dígito hexadecimal A

.---------------------------------------------------------------~--------------8

TEORIA DE PROBLEMAS DE PRINCIPIOS DIGITALES

significa que 256 debe ser multiplicado por 10, dando un producto de 2560. El número

hexadecimal muestra que contiene tres 16, y por tanto 16 x 3 = 48 que se suma a la línea

decimal. La columna del 1 contiene el dígito hexadecimal F, que significa 1 x 15 = 15.

El 15 se suma a la línea decimal. La columna del 0.0625 contiene el dígito hexadecimal C,

que significa 12 x 0.0625 = 0.75. El 0.75 se suma a la línea decimal. Al sumar los contenidos

de la línea decimal (2560 + 48 + 15 + 0.75 = 2623.75) se obtiene el número decimal 2623.75.

La Figura 1.8b convierte A3F,C16 en 2623.7510,

Potencias de 16

162

161

16°

Valor de la posición

256

16

l

Número hexadecimal

2

B

6

512

Decimal

xii

+

176

+

6

La parte fraccn

entero 4 es tra

muestra que el

La principa

ra 1.10a muestr

hexadecimal fo

entonces comb

111O 1110012 .

69410

(a) Conversión hexadecimal-decimal

Potencias de 16

162

161

16°

1/161

Valor de la posición

256

16

1

.0625

Número hexadecimal

A

3

F

C

256

xIO

Decimal

2560

16

x 3

+

48

+

4'

2 -;- 16 = O resto

(a) Conversión de

1

x 6

16

256

x 2

45 -;- 16 = 2 resto

I

1

x 15

.0625

x 12

15

+ 0.75

2623.7510

(b) Conversión hexadecimal fraccionario-decimal

Figura 1.8.

Ahora invertir el proceso y convertir el número decimal 45 en su equivalente hexadecimal. La Figura 1.9a detalla el proceso familiar de división repetida por 16. El número

décimal 45 se divide primero por 16, dando un 2 de cociente con resto 13. El resto 13

(D en hexadecimal) se convierte en el LSD del número hexadecimal. El cociente (2) se

transfiere a la posición del dividendo y se divide por 16. Así se obtiene un cociente de O

con un resto de 2. El 2 se convierte en el siguiente dígito del número hexadecimal. El proceso

finaliza cuando la parte entera del cociente es O. El proceso de la Figura 1.9a convierte el

número decimal 45 en el número hexadecimal 2D.

Convertir el número decimal 250.25 a hexadecimal. La conversión debe hacerse utilizando dos procesos como muestra la Figura 1.9b. La parte entera del número decimal (250)

se convierte en hexadecimal utilizando el proceso de división repetida por 16. Los restos

de 10 (A en hexadecimal) y 15 (F en hexadecimal) forman el número hexadecimal entero FA.

Otra conve

dígito hexadec

hexadecimal es

//

9

NUMEROS UTILIZADOS

UTILIZADOS EN ELECTRONICA

ELECTRONICA DIGITAL

DIGIT AL

NUMEROS

1 número

a la línea

15 = 15.

ecimal e,

ontenidos

12623.75.

-;- 16

16 == 15

15 resto de 10

1O-¡

250 -;~

-1 11

15 -;-;- 16

16 == O resto de 1

15 5 (

15

250.251010 =

= FA·

FA·

416

250.25

416

45 -;-;- 16

16 == 2 resto

resto de 1

13~3 = ; 1

45

I

.¡;

.¡;

-i- 16

16 == O resto de 2

2 -;-

JJ

11

II

0.25 x 16

16 == 4.00

0.25

I

J;¡

451(i

= 2

45

1ó =

16 == 0.00

0.00 x 16

DI6

DI6

(b) Conversión

Conversión decimal fraccionario-hexadecimal

fraccionario-hexadecimal

Conversión decimal-hexadecimal

decimal-hexadecimal

(a) Conversión

1.9.

Figura 1.9.

parte fraccionaria

fraccionaria del 250.25

250.25 se multiplica

multiplica por

por 16 (0.25 x 16). El resultado

resultado es 4.00.

4.00. El

La parte

entero 4 es transferido

transferido a la posición

posición mostrada

mostrada en la Figura

Figura 1.9b. La

La conversión

conversión completa

completa

entero

muestra que

que el número

número decimal

decimal 250.25

250.25 es igual

igual al hexadecimal

hexadecimal F A.4.

AA.

muestra

La principal

principal ventaja

sistema hexadecimal

hexadecimal es su fácil conversión

conversión al binario.

La FiguFiguLa

ventaja del sistema

binario. La

1. lOa muestra

muestra el número

convertido a binario.

Observar que

que cada

cada dígito

dígito

ra 1.1Oa

número hexadecimal

hexadecimal 3B9 convertido

binario. Observar

hexadecimal

forma un grupo

cuatro dígitos

dígitos binarios

binarios o bits.

bits. Los

Los grupos

grupos de bits

hexadecimal forma

grupo de cuatro

bits son

son

entonces

combinados para

para formar

formar el número

En este

este ca30

caso 3B916

es

igual

número binario.

binario. En

igual

a

entonces combinados

16

1110111001

1110

111 00 122. .

3

B

t

1

t

1

0011

1011

1011

9 16

1

3B9

11101110012

3B91616 == 1110111001

1001

(a) Conversión

Conversión hexadecimal-binario

hexadecimal-binario

4

7 . F

7

1t

1t

0100 0111.

0111

E

47.FE

= = 1000111.1111111

1000111.l11111122

47.FEI616

1t

1t

IIII

1111

1110

1110

(b)

(b) Conversión

Conversión hexadecimal

hexadecimal fraccionario-binario

fraccionario-binario

1010

hexadeci1 número

resto 13

te (2) se

ente de O

1proceso

nvierte el

rse utilimal (250)

os restos

tero FA.

1000

1000 0101

0101.

1!

!

1

t1

A

A

88

55

101010000101

101010000101 22

=

=

A851616

(e)

(e) Conversión

Conversión binario-hexadecimal

binario-hexadecimal

0(:(;1

:::(:(;1 0010

0010.• 0110

IlGC:

110:;

t 1t

t

1

1

t1

1

C

C

2 •

• 6

10010.011011

10010.011011 22

=

=

12.6C16

16

(d)

(d) Conversión

Conversión binario

binario fraccionario-hexadecimal

fraccionario-hexadecimal

Figura 1.10.

1.10.

Otra

Otra conversión

conversión hexadecimal

hexadecimal a binario

binario se detalla

detalla en

en la

la Figura

Figura 1.1Ob.

1.10b. De

De nuevo,

nuevo, cada

cada

dígito

dígito hexadecimal

hexadecimal forma

forma un

un grupo

grupo de

de cuatro

cuatro bits

bits en

en el número

número binario.

binario. El

El punto

punto

hexadecimal

bajado para

para formar

formar el punto

punto binario.

binario. El

El número

número hexadecimal

hexadecimal 47.FE

47.FE se

hexadecimal es bajado

-------------------------------------"""::"'--------10

TEORIA

DE PROBLEMAS

DE PRINCIPIOS

DIGITALES

convierte en el número binario 1000111.1111111. Es claro que los números hexadecimales,

debido a su compactación, son mucho más fáciles de escribir que largas cadenas de 1 y O

en binario. El sistema hexadecimal puede considerarse como un método abreviado de

escribir números binarios.

La Figura 1.l0c muestra la conversión del número binario 101010000101 a hexadecimal.

Primero dividir el número binario en grupos de cuatro bits comenzando en el punto binario.

Cada grupo de cuatro bits se traduce a su dígito hexadecimal equivalente. La Figura 1.10c

muestra que el número binario 101010000101 es igual al hexadecimal A85.

Otra conversión binario a hexadecimal se ilustra en la Figura 1.10d. Aquí el número

binario 10010.011011 se traduce a hexadecimal. Primero el número binario se divide en

grupos de cuatro bits comenzando en el punto binario. Tres O se añaden al grupo de más

a la izquierda, formando 0001. Dos O se añaden al grupo de más a la derecha, formando

1100. Cada grupo tiene ahora 4 bits y se traduce a un dígito hexadecimal como muestra la

Figura 1.l0d. El número binario 10010.01101 es igual a 12.6C16.

En la práctica, muchas modernas calculadoras manuales realizan conversiones entre

sistemas de numeración. La mayoría pueden convertir entre decimal, hexadecimal, octal y

binario. Estas calculadoras también pueden realizar operaciones aritméticas en varias bases

(como por ejemplo hexadecimal).

1.19. Convertir

8,

(a)

los

(b)

Solución:

Seguir el p

hexadecimales

(a)

(b)

810 = 816

1010 = A

1.20. Convertir

(a)

lo:

204.125

Solución:

Seguir el ¡

hexadecimales

(a) 204.1251,

(b) 255.8751

1.21. Convertir

(a) B,

lo

(i

Solución:

Seguir el¡

lentes binario

PROBLEMAS

1.15. El sistema

de numeración

hexadecimal,

RESUELTOS

a veces, se denomina

(a)

(b)

sistema

de base

(a)

1.16. Listar los dieciséis

hexadecimal, a veces, se denomina

símbolos

usados

en el sistema

(a)

los siguientes

números

(b)

?F,

(e) D52,

C,

enteros hexadecimales

a sus equivalentes

(d)

67E,

(e) ABCD.

hexadecimal

son O, 1,

Seguir el procedimiento mostrado en la Figura 1.8a. Acudir también a la Figura 1.7. Los equivalentes

decimales de los números hexadecimales son:

(b)

CI6

9FI6

= 1210

= 159

1.18. Convertir

(a)

FA,

10

(e)

(d)

los siguientes

(b)

D3.E,

D5216

67EI6

=

=

341010

166210

(e)

números

hexadecimales

(e)

1111,1,

(d)

ABCDI6

=

le

1001.1

10000C

decimales:

Solución:

(a)

= \(

= l

Solución:

Seguir el

lentes hexade

(a) 1001.11

(b) 1000000

hexadecimal.

Solución:

Acudir a la Figura 1.7. Los dieciséis símbolos usados en el sistema de numeración

2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E Y F.

1.17. Convertir

(b)

sistema de base 16.

de numeración

E16

1.22. Convertir

Solución:

El sistema de numeración

BI6

4398110

a sus equivalentes

decimales:

888.8,

(e)

EBA.C.

Solución:

Seguir el procedimiento mostrado en la Figura 1.8b. Acudir también a la Figura 1.7. Los equivalentes

decimales de los números hexadecimales son:

(a)

F.416 = 15.2510

(e)

1111.116 = 4369.062510

(e)

EBA.CI6 = 3770.7510

(b)

D3.E16 = 211.87510

(d)

888.816 = 2184.510

1.4.

NUMEE

El método de r

basados en mic

positivos. Sin e

negativos. Utili:

la magnitud de

Suponer un

más significativ

positivo. Sin el

7 bits restantes

La tabla dé

algunos númen

NUMERO

EN ELECTRONICA

ELECTRONICA DIGITAL

DIGITAL

NUMERO S UTILIZADOS

UTILIZADOS EN

xadecimales,

as de l y

breviado de

°

hexadecimal.

unto binario.

Figura 1.1Oc

í el número

se divide en

upo de más

a, formando

o muestra la

siones entre

'mal, octal y

varias bases

11

1.19.

equivalentes hexadecimales:

hexadecimales:

1.19. Convertir

Convertir los siguientes

siguientes números

números enteros

enteros decimales

decimales a sus equivalentes

(a)

(a)

8,

(b)

(b)

10,

lO,

(e)

(e)

14,

(d)

(d)

Solución:

Solución:

Seguir el procedimiento

procedimiento mostrado

mostrado en

Seguir

hexadecimales

hexadecimales de los números

números decimales

decimales

(a)

810

=

8

(e)

14

=

(a)

(e)

14

16

10

10

16

10 E16

16

(b)

10

(d)

16

(b)

1010

(d)

1610 = 10 16

10 = A16

16

16

16,

(e)

(e)

80,

(f)

(f)

2560,

2560,

(g)

(g)

3000,

3000,

(h)

(h)

62500.

62500.

Figura 1.9a. Acudir

Acudir también

equivalentes

la Figura

también a la Figura

Figura 1.7. Los

Los equivalentes

son:

(e)

8010

(e)

(g)

(g)

300010

10 = 50 16

16

10 = BB816

16

(f)

256010

(h)

62 5001010 = F424

F4241616

(f)

(h) 62500

10 = A0016

16

1.20. Convertir

Convertir los siguientes

siguientes números

números decimales

decimales a sus equivalentes

equivalentes hexadecimales:

1.20.

hexadecimales:

(a)

204.125,,

204.125

(b)

(b)

255.875,

255.875,

(e)

631.25,

631.25,

(d)

(d)

10 000.003

000.003 90625.

90625.

Solución:

Solución:

Seguir el procedimiento

procedimiento mostrado

mostrado en la Figura

Figura 1.9b. Acudir

Acudir también

también a la Figura

Figura 1.7. Los

Los equivalentes

equivalentes

Seguir

hexadecimales

hexadecimales de los números

números decimales

decimales son:

204.1251010 = CC.2

CC.21616

631.2510

277.416

(a) 204.125

(e) 631.25

10 = 277.4

16

(b) 255.875

(d) 10000.00390625

255.8751010 = FF.E

FF.EI6I6

10000.0039062510 10 = 2710.011616

1.21. Convertir

Convertir los siguientes

siguientes números

números hexadecimales

hexadecimales a sus equivalentes

1.21.

equivalentes binarios:

binarios:

(a)

(b)

E,

(d)

(e)

lF.C,

(f)

239.4.

(a)

B,

(b)

(e) lC,

IC,

(d)

A64,

(e)

IF.C,

(j)

239.4.

Solución:

Solución:

procedimiento mostrado

Acudir también

también a la Figura

Figura 1.7. Los

Los equivaequivaSeguir

Seguir el procedimiento

mostrado en la Figura

Figura 1.l0a

1.I0a yy b. Acudir

lentes

números hexadecimales

hexadecimales son:

lentes binarios

binarios de los números

(a)

B16

0022

(e)

(e) IC16

(a)

101122

11100

IF,C

= = 11111.1122

IF.CI6I6

16 = 1011

16 = 111

1000111001.012 2

(f) 239.4

239.416

E16 = 111022

(d)

10100110010022

(b) EI6

(d)

A6416

16 = 101001100100

16 = 1000111001.01

1.22. Convertir

Convertir los siguientes

siguientes números

números binarios

binarios a sus equivalentes

equivalentes hexadecimales:

hexadecimales:

1.22.

(a)

(a)

(b)

cimal son O, 1,

1001.1111

10000001.110 1

10000001.110

(e)

(e)

(d)

110101.011001

110101.011001

10000. 1

(e)

(e)

(f)

(f)

10100111.111011

10100111.111011

1000000.0000111

1000000.0000111

Solución:

Solución:

lOe yy d. Acudir

Acudir también

también a la Figura

Figura 1.7. Los

Los equivaequivaSeguir

Seguir el procedimiento

procedimiento mostrado

mostrado en la Figura

Figura 1.

I.I0e

decimales binarios

lentes

lentes hexadecimales

hexadecimales de los números

números decimales

binarios son:

son:

(a)

1001.l1112=9.FI6 I6

(e)

110.101.0110012 z = 35.64

10100111.1110112=A7.EC

(e)

110.IOI.OIIOOl

35.6416

(e) 10100111.III011

.EC I6

(a)

100l.l1112=9.F

16

z = A7I6

(b)

81.D1616

(b)

I10000001.1101

000000 l.l 1012 2 = 81.D

(d)

(d) 10000.1 22 = 10.8 16

(f)

1000000.00001112 2 = 40.0E

(f)

1000000.0000111

40.0E1616

16

1.4. NUMEROS

NUMEROS EN COMPLEMENTO

COMPLEMENTO A 2

1.4.

s equivalentes

s equivalentes

El método

muy utilizado

utilizado en los equipos

equipos

El

método de representar

representar números

números en complemento

complemento a 2 es muy

basados en microprocesador.

microprocesador.

Hasta ahora,

ahora, hemos

hemos supuesto

supuesto que

son

basados

Hasta

que todos

todos los

los números

números son

positivos.

tratar tanto

tanto números

positivos como

como

positivos. Sin embargo,

embargo, los microprocesadores

microprocesadores deben

deben tratar

números positivos

del

pueden determinarse

determinarse el signo

signo yy

negativos.

negativos. Utilizando

Utilizando la representación

representación

del complemento

complemento a 2, pueden

la magnitud

magnitud de un número

número. .

Suponer

como el de la Figura

Figura 1.11

l.11 a.

a. El bit

bit

Suponer un registro

registro de 8 bits

bits de un microprocesador

microprocesador como

más significativo

bit es 0,

O, entonces

entonces el número

número es (+)

significativo (MSB)

(MSB) es el bit

bit de signo.

signo. Si este

este bit

(+)

positivo.

número es (-)

negativo. Los

Los

positivo. Sin embargo,

embargo, si el bit

bit de signo

signo es 1, entonces

entonces el número

(-) negativo.

7 bits restantes

representan la magnitud

número.

restantes del registro

registro ."representan

magnitud del número.

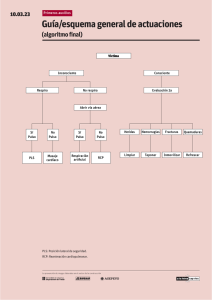

tabla de la Figura

Figura l.11

1.11 b muestra

muestra las representaciones

representaciones en complemento

La tabla

complemento a 2 para

para

algunos números

números positivos

positivos y negativos.

negativos. Por

Por ejemplo,

ejemplo, + 127 está

algunos

está representado

representado en complecomple-

12

TEORIA

DE PROBLEMAS

DE PRINCIPIOS

1

DIGIT ALES

Bit de signo O = (+)

1=(-)

mento a 2 pe

a 2 por el nr

todos los valo

Convertir

Figura 1.12 s

Magnitud

(a)

El MSB de un registro de 8 bits es el bit de signo

Decimal

con signo

Representación

en complemento

a 2, con 8 bits

+ 127

O

III

+126

O

111

1110

+ 125

O

111

1101

+ 124

O

111

1100

+5

O

000

0101

+4

O

000

0100

+3

O

000

0011

+2

000

0010

+1

O

O

000

0001

+0

O

000

0000

-1

1

111

1111

-2

1

111

1110

-3

1

II1

1101

-4

1

1I J

1100

-5

J

I !1

1011

-125

1

000

0011

-126

1

000

0010

-127

1

000

0001

-128

1

000

0000

Signo

(b)

1111

Paso 1. ~

signo será 1 e

Paso 2. (

decimal 1 es

Paso 3. (

el binario OO

por 1 y cada

Paso 4. (

este ejemplo

al complemei

Paso 5. 1

correspondiei

El resultado

a 2. El núm

Figura 1.12.

Igual que

los números

binarios

Magnitud

Representaciones en complemento

positivos y negativos

Figura 1.11.

a 2 de números

Fi

NUMERO

ELECTRO NI CA DIGIT

DIGITAL

NUMEROSS UTILIZADOS