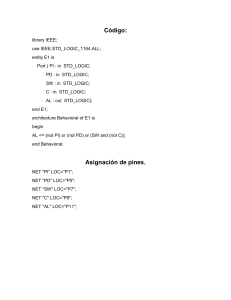

DECODIFICADOR library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity codigo is Port ( CLK : in STD_LOGIC; Q : inout STD_LOGIC_VECTOR (3 downto 0); S : out STD_LOGIC_VECTOR (15 downto 0)); end codigo; architecture Behavioral of codigo is signal con: STD_LOGIC_VECTOR (25 DOWNTO 0):= (others => '0'); signal clk1: STD_LOGIC; signal D: STD_LOGIC_VECTOR (3 DOWNTO 0); begin D(0)<= (NOT Q(0)); D(1)<= ((NOT Q(1) AND Q(0)) OR (Q(1) AND NOT Q(0))); D(2)<= ((Q(2) AND NOT Q(0)) OR (Q(2) AND NOT Q(1)) OR (NOT Q(2) AND Q(1) AND Q(0))); D(3)<= ((Q(3) AND NOT Q(0)) OR (Q(3) AND NOT Q(1)) OR (Q(3) AND NOT Q(2)) OR (NOT Q(3) AND Q(2) AND Q(1) AND Q(0))); -----------------------------proces clock process (clk) begin if clk 'event and clk = '1' then if con = "01011111010111100001000000" then -- 50 MHZ. A BINARIO PERIODO DE 1 HZ- 1 SEG. con <= "00000000000000000000000000"; clk1 <= (NOT clk1); else con <= con + '1'; end if; end if; end process; -----------------------------proceso clock process (clk1) BEGIN IF clk1 'event and clk1='1' then Q<=D; END IF; END PROCESS; -----------------------------Proceso para el decodificador process (Q) begin case Q is --AA1A2BCD2D1EFHJKG1G2LMN -- ORDEN PINES when "0000" => S <= "1111111100000000"; -- O . when "0001" => S <= "0011001110100000"; -- M . when "0010" => S <= "1111001100011000"; -- A . when "0011" => S <= "1110001100011100"; -- R . when "0100" => S <= "0000000000011000"; -- - . when "0101" => S <= "1100111100000000"; -- C . when "0110" => S <= "1110001100011100"; -- R . when "0111" => S <= "0011111100000000"; -- U . when "1000" => S <= "1100110000100001"; -- Z . when "1001" => S <= "0000000000011000"; -- - . when "1010" => S <= "1110001100011100"; -- R . when "1011" => S <= "1111111100000000"; -- O . when "1100" => S <= "0011001110100000"; -- M . when "1101" => S <= "1100111100011000"; -- E . when "1110" => S <= "1110001100011100"; -- R . when "1111" => S <= "1111111100000000"; -- O . when others => S <= "0000000000000000"; end case; end process; end Behavioral; Asignación de Pines NET "CLK" LOC=P56; NET "Q(3)" LOC=P131; NET "Q(2)" LOC=P133; NET "Q(1)" LOC=P137; NET "Q(0)" LOC=P139; //CONFIGURACION PINES DISPLAY NET "S(0)" LOC=P2; //N NET "S(1)" LOC=P6; //M NET "S(2)" LOC=P8; //L NET "S(3)" LOC=P10; //G2 NET "S(4)" LOC=P12;//G1 NET "S(5)" LOC=P15;//K NET "S(6)" LOC=P17;//J NET "S(7)" LOC=P22;//H NET "S(8)" LOC=P24;//F NET "S(9)" LOC=P27;//E NET "S(10)" LOC=P30;//D1 NET "S(11)" LOC=P33;//D2 NET "S(12)" LOC=P35;//C NET "S(13)" LOC=P41;//B NET "S(14)" LOC=P51;//A2 NET "S(15)" LOC=P144;//A1