La caché de instrucciones de un ordenador memoria separada

Anuncio

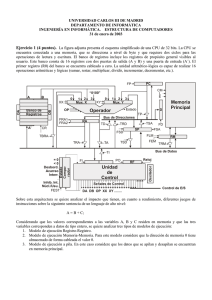

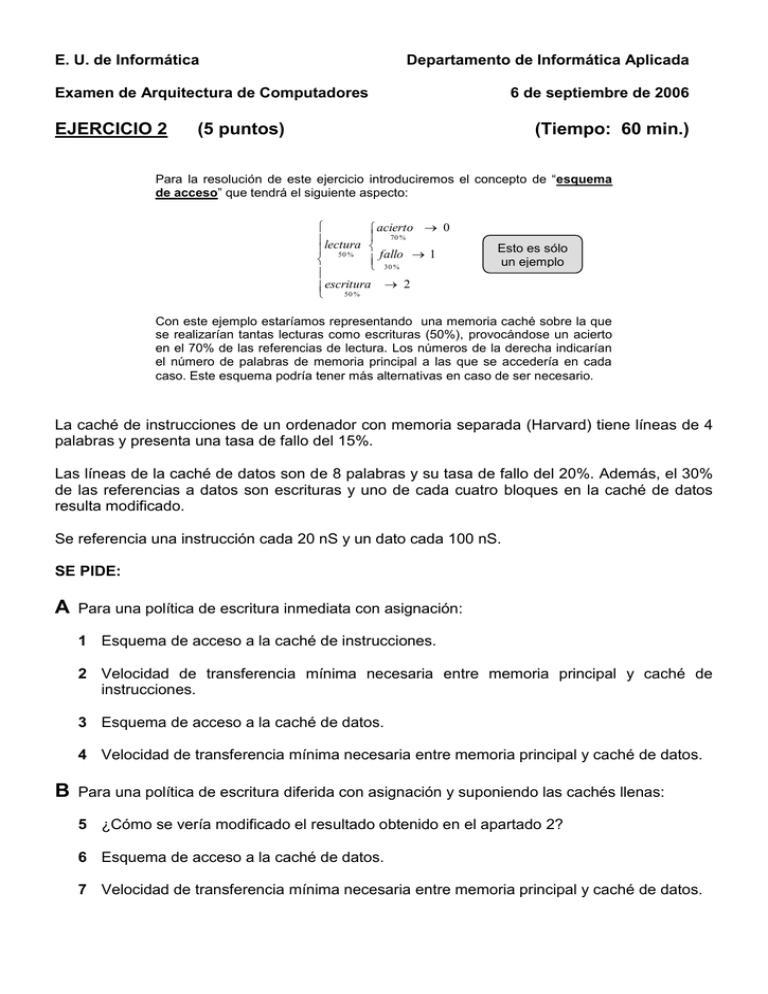

E. U. de Informática Departamento de Informática Aplicada Examen de Arquitectura de Computadores EJERCICIO 2 6 de septiembre de 2006 (5 puntos) (Tiempo: 60 min.) Para la resolución de este ejercicio introduciremos el concepto de “esquema de acceso” que tendrá el siguiente aspecto: acierto 0 lectura 70 % 50 % fallo 1 30 % 2 escritura 50 % Esto es sólo un ejemplo Con este ejemplo estaríamos representando una memoria caché sobre la que se realizarían tantas lecturas como escrituras (50%), provocándose un acierto en el 70% de las referencias de lectura. Los números de la derecha indicarían el número de palabras de memoria principal a las que se accedería en cada caso. Este esquema podría tener más alternativas en caso de ser necesario. La caché de instrucciones de un ordenador con memoria separada (Harvard) tiene líneas de 4 palabras y presenta una tasa de fallo del 15%. Las líneas de la caché de datos son de 8 palabras y su tasa de fallo del 20%. Además, el 30% de las referencias a datos son escrituras y uno de cada cuatro bloques en la caché de datos resulta modificado. Se referencia una instrucción cada 20 nS y un dato cada 100 nS. SE PIDE: A Para una política de escritura inmediata con asignación: 1 Esquema de acceso a la caché de instrucciones. 2 Velocidad de transferencia mínima necesaria entre memoria principal y caché de instrucciones. 3 Esquema de acceso a la caché de datos. 4 Velocidad de transferencia mínima necesaria entre memoria principal y caché de datos. B Para una política de escritura diferida con asignación y suponiendo las cachés llenas: 5 ¿Cómo se vería modificado el resultado obtenido en el apartado 2? 6 Esquema de acceso a la caché de datos. 7 Velocidad de transferencia mínima necesaria entre memoria principal y caché de datos.