Circuito TTL (Transistor-Transistor Logic)

Anuncio

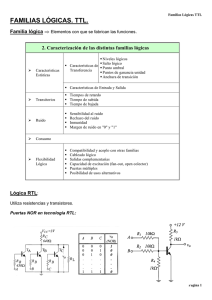

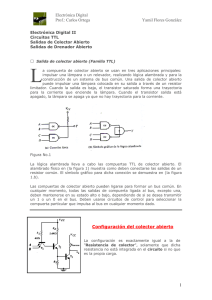

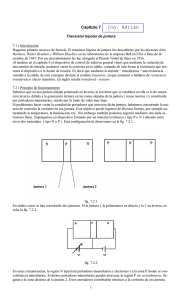

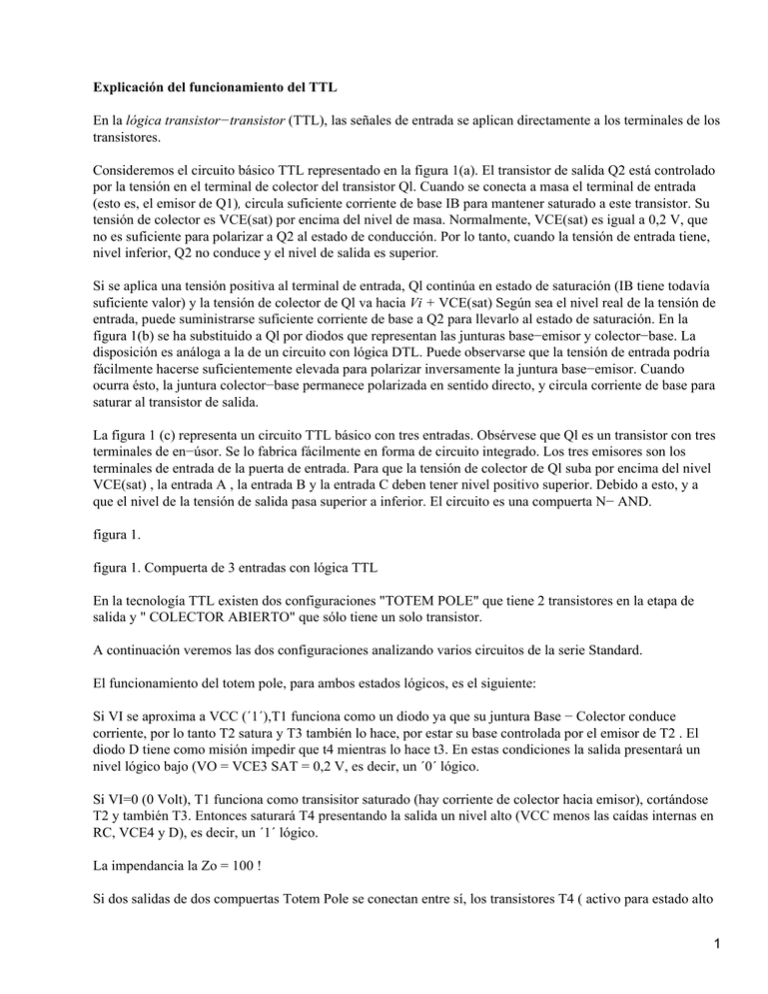

Explicación del funcionamiento del TTL En la lógica transistor−transistor (TTL), las señales de entrada se aplican directamente a los terminales de los transistores. Consideremos el circuito básico TTL representado en la figura 1(a). El transistor de salida Q2 está controlado por la tensión en el terminal de colector del transistor Ql. Cuando se conecta a masa el terminal de entrada (esto es, el emisor de Q1), circula suficiente corriente de base IB para mantener saturado a este transistor. Su tensión de colector es VCE(sat) por encima del nivel de masa. Normalmente, VCE(sat) es igual a 0,2 V, que no es suficiente para polarizar a Q2 al estado de conducción. Por lo tanto, cuando la tensión de entrada tiene, nivel inferior, Q2 no conduce y el nivel de salida es superior. Si se aplica una tensión positiva al terminal de entrada, Ql continúa en estado de saturación (IB tiene todavía suficiente valor) y la tensión de colector de Ql va hacia Vi + VCE(sat) Según sea el nivel real de la tensión de entrada, puede suministrarse suficiente corriente de base a Q2 para llevarlo al estado de saturación. En la figura 1(b) se ha substituido a Ql por diodos que representan las junturas base−emisor y colector−base. La disposición es análoga a la de un circuito con lógica DTL. Puede observarse que la tensión de entrada podría fácilmente hacerse suficientemente elevada para polarizar inversamente la juntura base−emisor. Cuando ocurra ésto, la juntura colector−base permanece polarizada en sentido directo, y circula corriente de base para saturar al transistor de salida. La figura 1 (c) representa un circuito TTL básico con tres entradas. Obsérvese que Ql es un transistor con tres terminales de en−úsor. Se lo fabrica fácilmente en forma de circuito integrado. Los tres emisores son los terminales de entrada de la puerta de entrada. Para que la tensión de colector de Ql suba por encima del nivel VCE(sat) , la entrada A , la entrada B y la entrada C deben tener nivel positivo superior. Debido a esto, y a que el nivel de la tensión de salida pasa superior a inferior. El circuito es una compuerta N− AND. figura 1. figura 1. Compuerta de 3 entradas con lógica TTL En la tecnología TTL existen dos configuraciones "TOTEM POLE" que tiene 2 transistores en la etapa de salida y " COLECTOR ABIERTO" que sólo tiene un solo transistor. A continuación veremos las dos configuraciones analizando varios circuitos de la serie Standard. El funcionamiento del totem pole, para ambos estados lógicos, es el siguiente: Si VI se aproxima a VCC (´1´),T1 funciona como un diodo ya que su juntura Base − Colector conduce corriente, por lo tanto T2 satura y T3 también lo hace, por estar su base controlada por el emisor de T2 . El diodo D tiene como misión impedir que t4 mientras lo hace t3. En estas condiciones la salida presentará un nivel lógico bajo (VO = VCE3 SAT = 0,2 V, es decir, un ´0´ lógico. Si VI=0 (0 Volt), T1 funciona como transisitor saturado (hay corriente de colector hacia emisor), cortándose T2 y también T3. Entonces saturará T4 presentando la salida un nivel alto (VCC menos las caídas internas en RC, VCE4 y D), es decir, un ´1´ lógico. La impendancia la Zo = 100 ! Si dos salidas de dos compuertas Totem Pole se conectan entre sí, los transistores T4 ( activo para estado alto 1 de una compuerta) y T3 (activo para el estado bajo de la otra compuerta), este último componetente se sobrecalentará cor exceso de corriente hasta quemarse. INVERSOR COLECTOR ABIERTO La configuración Open Colector es similar a la vista, con la diferencia que necesita un resistor externo para funcionar, cuyo valor depende de las condiciones de consumo y velocidad que se deseen lograr. Otros casos de compuertas TTL El siguiente circuito corresponde una TTL con TRI−STATE o HZ ( Alta Impedancia ) Circuitos TTL Open Colector 1 5 2