apuntes - Pontificia Universidad Católica de Chile

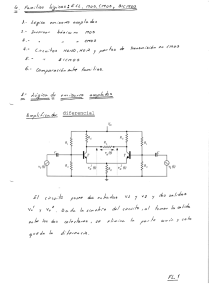

Anuncio