¿En el diseño de nuesrto microprocesador cuál de los siguientes

Anuncio

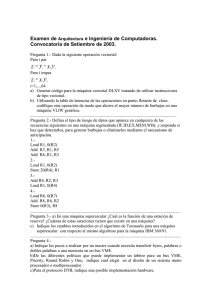

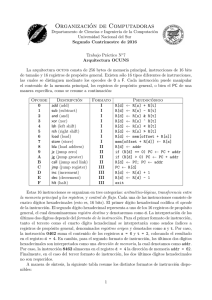

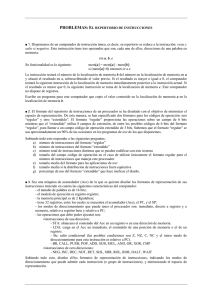

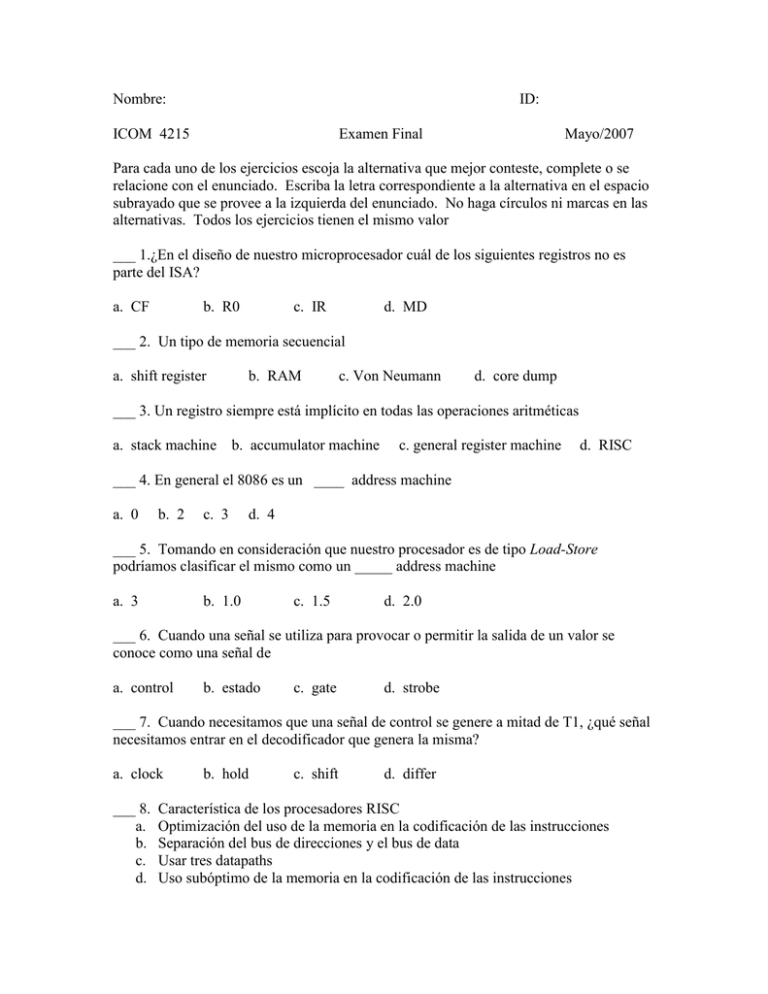

Nombre: ID: ICOM 4215 Examen Final Mayo/2007 Para cada uno de los ejercicios escoja la alternativa que mejor conteste, complete o se relacione con el enunciado. Escriba la letra correspondiente a la alternativa en el espacio subrayado que se provee a la izquierda del enunciado. No haga círculos ni marcas en las alternativas. Todos los ejercicios tienen el mismo valor ___ 1.¿En el diseño de nuestro microprocesador cuál de los siguientes registros no es parte del ISA? a. CF b. R0 c. IR d. MD ___ 2. Un tipo de memoria secuencial a. shift register b. RAM c. Von Neumann d. core dump ___ 3. Un registro siempre está implícito en todas las operaciones aritméticas a. stack machine b. accumulator machine c. general register machine d. RISC ___ 4. En general el 8086 es un ____ address machine a. 0 b. 2 c. 3 d. 4 ___ 5. Tomando en consideración que nuestro procesador es de tipo Load-Store podríamos clasificar el mismo como un _____ address machine a. 3 b. 1.0 c. 1.5 d. 2.0 ___ 6. Cuando una señal se utiliza para provocar o permitir la salida de un valor se conoce como una señal de a. control b. estado c. gate d. strobe ___ 7. Cuando necesitamos que una señal de control se genere a mitad de T1, ¿qué señal necesitamos entrar en el decodificador que genera la misma? a. clock ___ 8. a. b. c. d. b. hold c. shift d. differ Característica de los procesadores RISC Optimización del uso de la memoria en la codificación de las instrucciones Separación del bus de direcciones y el bus de data Usar tres datapaths Uso subóptimo de la memoria en la codificación de las instrucciones ___ 9. Por “gufear” a. Whetstones b. Dhrystones c. MIPS d. MFLOPS ___ 10. No es típico de CISC ni de RISC a. b. c. d. Tamaño igual para todas las instrucciones Uso de memoria cache Uso de registros temporeros Uso de ventanas de registros ___ 11. No es ambiguo a. CISC b. RISC c. RTN d. SparcArq ___ 12. No necesita latches para almacenar los valores que entran y salen del ALU a. 1 data path b. 2 data paths c. 3 data paths d. RISC ___ 13. Podría crear un problema de data hazard a. push r1 push r2 b. pop r1 pop r2 c. add r1, r2, r3 add r3, r2, r1 d. add r1, r2, r3 add r4, r5, r6 ___ 14. Provee más flexibilidad durante la etapa de desarrollo a. 1 datapah b. general register c. microcódigo d. SPARC ___ 15. Factor que por el que existen los data hazards a. tener más de un bus b. tener pipeline c. tener instrucciones de largo fijo d. no tener stack e. ser super escalar ___ 16. Circuito no combinacional según las especificaciones de nuestro proyecto a. generador de estados d. incrementador del PC b. módulo para shift/rotate c. decodificador de opcodes ___ 17. Se necesita para poder conectar entre sí la salida de varios circuitos a. buffers b. latches c. gates d. tri-state ___ 18. Puede haber un delayed load a. load r1,10 add r2, r3, r4 b. add r2, r3, r4 load r1, alfa c. load r1, alfa load r2, beta d. load r1, alfa add r2, r3, r4 ___ 19. ¿Qué operación establece el siguiente RTN? n r1 r 2 r 3 r 3 31..n # (n @ r 0 ) a. b. c. d. añade n ceros al final del registro r3 añade n veces el bit r<0> al final del registro r3 no hace nada sustituye los n bits menos significativos de r3 por el valor del bit menos significativo del mismo e. sustituye los n bits menos significativos de r3 por el mismo bit ___ 20. Memoria más rápida del procesador a. cache b. RAM c. ROM d. registros ___ 21. Mirando el contenido de una localización de memoria cómo sabemos si tiene una instrucción o un dato a. comparando su contenido con el formato de las instrucciones b. el mismo valor podría fungir a veces como dato y oras como instrucción Los siguientes ejercicios están relacionados con la arquitectura discutida en clase para el diseño de los proyectos del curso ___ 22. Lluego de ejecutar OR R2,R1,R0 el valor de R2 será a. el valor original de R2 b. R1 c. R0 d. no se puede determinar ___ 23. Al ejecutar la instrucción STR, ¿qué valor tiene que tener el campo C de la misma para que la ejecución de la instrucción modifique a la misma en la memoria? a. 00B b. 01B c. 10B d. 11B e. No se puede determinar ___ 24. Al ejecutar la instrucción LDR, ¿qué valor tiene que tener el campo RCX para para provocar un loop infinito? a. -1 b. 0 c. 1 d. 2 e. No se puede determinar ___ 25.. ¿Cuál de las siguientes instrucciones podría utilizarse para sustituir una instrucción de NOP sin requerir ayuda de otras instrucciones? a. stop b. not c. ldi d. br