Contador

Anuncio

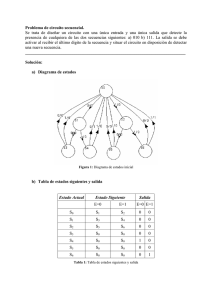

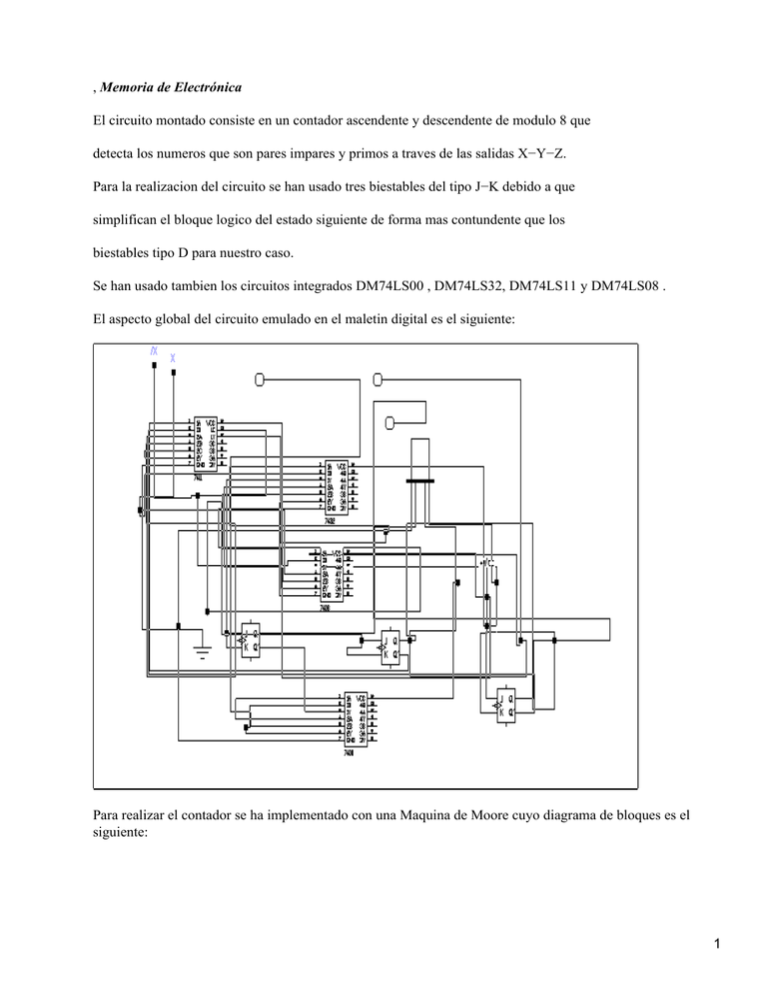

, Memoria de Electrónica El circuito montado consiste en un contador ascendente y descendente de modulo 8 que detecta los numeros que son pares impares y primos a traves de las salidas X−Y−Z. Para la realizacion del circuito se han usado tres biestables del tipo J−K debido a que simplifican el bloque logico del estado siguiente de forma mas contundente que los biestables tipo D para nuestro caso. Se han usado tambien los circuitos integrados DM74LS00 , DM74LS32, DM74LS11 y DM74LS08 . El aspecto global del circuito emulado en el maletin digital es el siguiente: Para realizar el contador se ha implementado con una Maquina de Moore cuyo diagrama de bloques es el siguiente: 1 El diagrama de estados que define el paso de unos estados a otros dependiendo de la variable x se ilustra en la siguiente figura: X=0 descendente X=1ascendente La tabla de excitación para el contador es: 2 Para la implementacion de las entradas de los biestables se han usado 2 tablas de Karnaugh siendo las entradas del biestable Jc=Kc=1,como evidentemente se puede apreciar en la tabla de excitación. Para Ja=Ka y Jb=Kb respectivamente, tenemos: 3 Para el bloque logico de salida tenemos,ademas de Qa,Qb y Qc, tres salidas mas: Xdetecta los numeros pares=/Qc Ydetecta los numeros impares=Qc Zdetecta los numeros primos y viene dada por: Qb −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− Qc −−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−−− 1 1 1 1 1 Z=/QaQb + Qc. Z ha sido implementado con puertas logicas Nand quedando de la siguiente manera: 4 5