Plantillas VHDL – Digital II – ECA 2010 library IEEE; use IEEE.std_logic_1164.all;

Anuncio

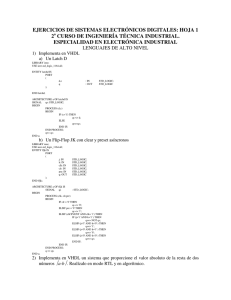

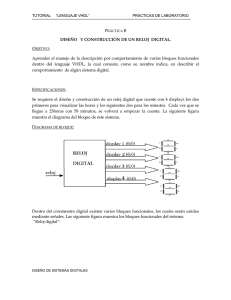

Plantillas VHDL – Digital II – ECA 2010 Declaración de bibliotecas y visibilidad de paquetes usuales library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; use IEEE.std_logic_signed.all; Declaración de entidad entity nombre_entidad is port ( nombre_puerto1 : modo tipo; …………………….. nombre_puerton: modo tipo ); end nombre_entidad; Declaración de arquitectura architecture nombre_arquitectura of nombre_entidad is -- declaración de señales begin -- cuerpo de la arquitectura end nombre_arquitectura; Declaración de señal signal nombre_señal: tipo ; Declaración de variable variable nombre_variable: tipo ; Asignación a señal nombre_señal <= expresión _o_valor; Asignación a variable nombre_variable := expresión _o_valor; Asignación condicional a señal nombre_señal <= expresión _o_valor when condición else expresión _o_valor when condición else expresión _o_valor ; -1- Plantillas VHDL – Digital II – ECA 2010 Asignación con selección a señal with expresión_de_selección select nombre_señal <= expresión _o_valor when opciones_separadas_por_|, expresión _o_valor when opciones_separadas_por_|, expresión _o_valor when others; Bloque process process ( señal1 , señal2, …, señaln) --declaración de variables begin --cuerpo del proceso end process; If – then - else if condición then sentencia1; .. ; sentencian; elsif condición then sentencia1; .. ; sentencian; else sentencia1; .. ; sentencian; end if; Case con selección de dos bits case selección_2bits is when "00" => sentencia1; .. ; sentencian; when "01" => sentencia1; .. ; sentencian; when "10" => sentencia1; .. ; sentencian; when "11" => sentencia1; .. ; sentencian; when others => sentencia1; .. ; sentencian; end case; Declaración de un tipo arreglo de std_logic_vector para bloques de memoria type nombre is array ( 0 to m) of std_logic_vector(n-1 downto 0); Asignación de valores a las locaciones del bloque de memoria -2- Plantillas VHDL – Digital II – ECA 2010 nombre_memoria <= ( 0 => “valor0”, 1 => “valor1”, 2 => "valor2", … => …, m-1 => "valorm-1"); Nota importante: algunas de estas plantillas están simplificadas, teniendo en cuenta el alcance definido para VHDL en la asignatura. Todas son correctas sintácticamente y sintetizables en el ambiente de trabajo, si se las aplica sin errores. -3-