EXAMEN CIRCUITOS ELECTRNICOS

Anuncio

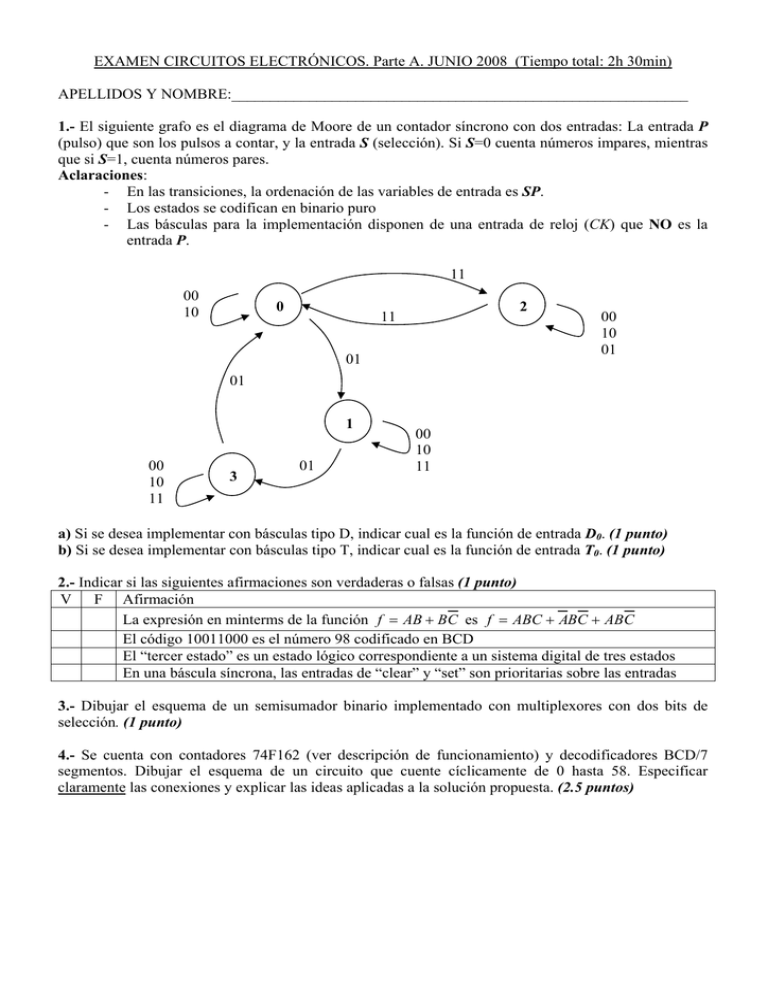

EXAMEN CIRCUITOS ELECTRÓNICOS. Parte A. JUNIO 2008 (Tiempo total: 2h 30min) APELLIDOS Y NOMBRE:___________________________________________________________ 1.- El siguiente grafo es el diagrama de Moore de un contador síncrono con dos entradas: La entrada P (pulso) que son los pulsos a contar, y la entrada S (selección). Si S=0 cuenta números impares, mientras que si S=1, cuenta números pares. Aclaraciones: - En las transiciones, la ordenación de las variables de entrada es SP. - Los estados se codifican en binario puro - Las básculas para la implementación disponen de una entrada de reloj (CK) que NO es la entrada P. 11 00 10 0 2 11 01 00 10 01 01 1 00 10 11 3 01 00 10 11 a) Si se desea implementar con básculas tipo D, indicar cual es la función de entrada D0. (1 punto) b) Si se desea implementar con básculas tipo T, indicar cual es la función de entrada T0. (1 punto) 2.- Indicar si las siguientes afirmaciones son verdaderas o falsas (1 punto) V F Afirmación La expresión en minterms de la función f = AB + BC es f = ABC + ABC + ABC El código 10011000 es el número 98 codificado en BCD El “tercer estado” es un estado lógico correspondiente a un sistema digital de tres estados En una báscula síncrona, las entradas de “clear” y “set” son prioritarias sobre las entradas 3.- Dibujar el esquema de un semisumador binario implementado con multiplexores con dos bits de selección. (1 punto) 4.- Se cuenta con contadores 74F162 (ver descripción de funcionamiento) y decodificadores BCD/7 segmentos. Dibujar el esquema de un circuito que cuente cíclicamente de 0 hasta 58. Especificar claramente las conexiones y explicar las ideas aplicadas a la solución propuesta. (2.5 puntos) EXAMEN CIRCUITOS ELECTRÓNICOS. Parte B. JUNIO 2008 (Tiempo total: 2h 30min) APELLIDOS Y NOMBRE:___________________________________________________________ 5 - Realice la programación en lenguaje VHDL del sistema de la pregunta 1, completando la plantilla adjunta. (2.5 puntos) Por claridad se repite aquí la descripción del sistema: El siguiente grafo es el diagrama de Moore de un contador síncrono con dos entradas: La entrada P (pulso) que son los pulsos a contar, y la entrada S (selección). Si S=0 cuenta números impares, mientras que si S=1, cuenta números pares. Aclaraciones: - En las transiciones, la ordenación de las variables de entrada es SP. - Los estados se codifican en binario puro - Las básculas para la implementación disponen de una entrada de reloj (CK) que NO es la entrada P. 11 00 10 0 2 11 01 01 1 00 10 11 3 01 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ejercicio5 is Port ( S : in STD_LOGIC; P : in STD_LOGIC; Reset : in STD_LOGIC; Q0 : out STD_LOGIC; Q1: out STD_LOGIC); end ejercicio2; architecture Behavioral of ejercicio2 is type estados_posibles IS (cero,uno,dos,tres); signal estado: estados_posibles; begin end Behavioral; 00 10 11 00 10 01 6.- Respecto del siguiente código en VHDL, indicar si las siguientes afirmaciones son verdaderas o falsas (1.0 punto) V F Afirmación La expresión Z<= (A and (not C)) or (B and C) seria otra alternativa a la hora de describir la salida Z en VHDL . La sentencia entrada <= A&B&C no es correcta, se debería de definir las entradas A,B y C dentro de un vector de tres elementos en la lista de puertos. Falta especificar el valor que toma la salida Z para algunos valores de las entradas (“011”, “100”, “110” y “111”). La expresión Z<= A when (C=’0’) else B seria otra alternativa a la hora de describir la salida Z en VHDL . LIBRARY IEEE; USE IEEE.std_logic_1164.all; ENTITY sistema_combinacional IS PORT(A, B, C : in std_logic; Z: out std_logic); END sistema_combinacional; ARCHITECTURE arquitectura OF sistema_combinacional IS SIGNAL entrada : std_logic_vector (2 downto 0); BEGIN entrada <= A & B & C; WITH entrada SELECT Z <= ‘0’ WHEN “000”, ‘0’ WHEN “001”, ‘0’ WHEN “010”, ‘0’ WHEN “101”, ‘1’ WHEN OTHERS; END arquitectura; Solución 1.- a) D0 = P·Q0 + S·P·Q1 + S·Q0 b) T0 = S·P··Q1·Q0 + S·P·Q1·Q0 2.- 3.- EXAMEN CIRCUITOS ELECTRÓNICOS. JUNIO 2008 (2h 30min) APELLIDOS Y NOMBRE:___________________________________________________________ 5 - Realice la programación en lenguaje VHDL del sistema de la pregunta 1, completando la plantilla adjunta. (2.5 puntos) (Por claridad se repite aquí la descripción del sistema: El siguiente grafo es el diagrama de Moore de un contador con dos entradas: La entrada P (pulso) que son los pulsos a contar, y la entrada S (selección) y dos salidas Q0 y Q1. Si S=0 cuenta números impares, mientras que si S=1, cuenta números pares. (En las transiciones, la ordenación de las variables de entrada es SP).) 11 00 10 0 2 11 01 01 1 00 10 11 3 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ejercicio5 is Port ( S : in STD_LOGIC; P : in STD_LOGIC; CLK: in STD_LOGIC; Reset : in STD_LOGIC; Q0 : out STD_LOGIC; Q1: out STD_LOGIC); end ejercicio2; 01 00 10 11 00 10 01 architecture Behavioral of ejercicio2 is type estados_posibles IS (cero,uno,dos,tres); signal estado: estados_posibles; signal entrada: STD_LOGIC_VECTOR(1 downto 0); begin entrada<=S&P; --Definimos un proceso sensible al reloj y al reset para modificar el estado. process(CLK, Reset) begin --Reset asíncrono de nivel activo alto. if (Reset='1') then estado <= cero; elsif (CLK 'event and CLK='1') then case estado is when cero => --Estado cero. if (entrada=”11”) then estado <= dos; elsif(entrada=”01”) then estado <= uno; end if; when uno=> --Estado uno. if (entrada=”01”) then estado <= tres; end if; when dos=> --estado dos. if (entrada=”11”) then estado <= cero; end if; when tres=> --estado tres. if (entrada=”01”) then estado <= cero; end if; end case; end if; end process; --Ahora en función del estado, generamos la salida Q0<='1' when (estado = uno or estado= tres) else '0'; Q1<='1' when (estado = dos or estado= tres) else '0'; end Behavioral; 6.- Respecto del siguiente código en VHDL, indicar si las siguientes afirmaciones son verdaderas o falsas (1.0 punto) V x F x x x Afirmación La expresión Z<= (A and (not C)) or (B and C) seria otra alternativa a la hora de describir la salida Z en VHDL . La sentencia entrada <= A&B&C no es correcta, se debería de definir las entradas A,B y C dentro de un vector de tres elementos en la lista de puertos. Falta especificar el valor que toma la salida Z para algunos valores de las entradas (“011”, “100”, “110” y “111”). La expresión Z<= A when (C=’0’) else B seria otra alternativa a la hora de describir la salida Z en VHDL . LIBRARY IEEE; USE IEEE.std_logic_1164.all; ENTITY sistema_combinacional IS PORT(A, B, C : in std_logic; Z: out std_logic); END sistema_combinacional; ARCHITECTURE arquitectura OF sistema_combinacional IS SIGNAL entrada : std_logic_vector (2 downto 0); BEGIN entrada <= A & B & C; WITH entrada SELECT Z <= ‘0’ WHEN “000”, ‘0’ WHEN “001”, ‘0’ WHEN “010”, ‘0’ WHEN “101”, ‘1’ WHEN OTHERS; END arquitectura;