EjercicioClasesLab20..

Anuncio

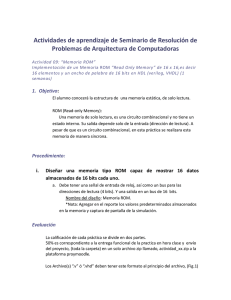

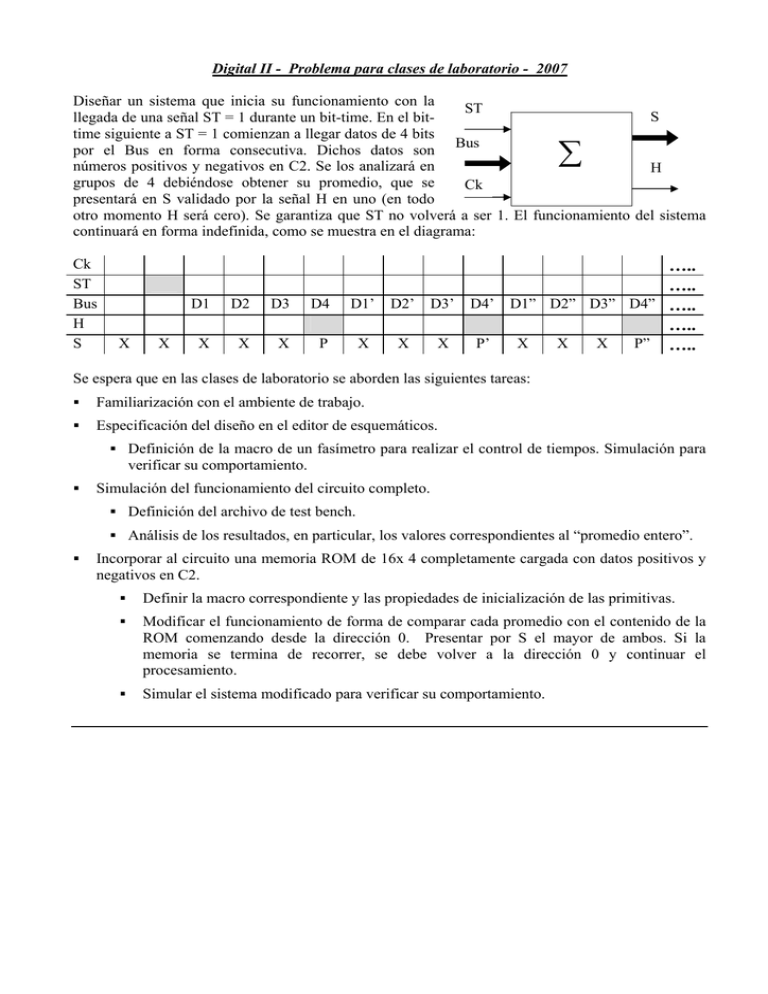

Digital II - Problema para clases de laboratorio - 2007 Diseñar un sistema que inicia su funcionamiento con la ST S llegada de una señal ST = 1 durante un bit-time. En el bittime siguiente a ST = 1 comienzan a llegar datos de 4 bits por el Bus en forma consecutiva. Dichos datos son Bus números positivos y negativos en C2. Se los analizará en H grupos de 4 debiéndose obtener su promedio, que se Ck presentará en S validado por la señal H en uno (en todo otro momento H será cero). Se garantiza que ST no volverá a ser 1. El funcionamiento del sistema continuará en forma indefinida, como se muestra en el diagrama: ∑ Ck ST Bus H S X X D1 D2 D3 D4 X X X P ….. ….. D1’ D2’ D3’ D4’ D1” D2” D3” D4” ….. ….. X X X P’ X X X P” ….. Se espera que en las clases de laboratorio se aborden las siguientes tareas: Familiarización con el ambiente de trabajo. Especificación del diseño en el editor de esquemáticos. Definición de la macro de un fasímetro para realizar el control de tiempos. Simulación para verificar su comportamiento. Simulación del funcionamiento del circuito completo. Definición del archivo de test bench. Análisis de los resultados, en particular, los valores correspondientes al “promedio entero”. Incorporar al circuito una memoria ROM de 16x 4 completamente cargada con datos positivos y negativos en C2. Definir la macro correspondiente y las propiedades de inicialización de las primitivas. Modificar el funcionamiento de forma de comparar cada promedio con el contenido de la ROM comenzando desde la dirección 0. Presentar por S el mayor de ambos. Si la memoria se termina de recorrer, se debe volver a la dirección 0 y continuar el procesamiento. Simular el sistema modificado para verificar su comportamiento.