Semana 9

Anuncio

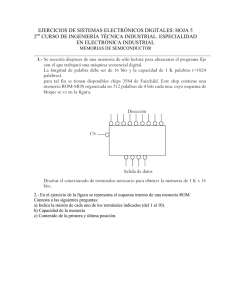

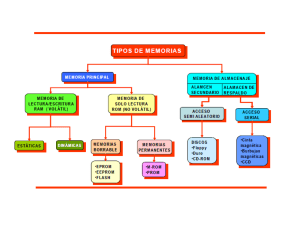

Actividades de aprendizaje de Seminario de Resolución de Problemas de Arquitectura de Computadoras Actividad 09: “Memoria ROM” Implementación de un Memoria ROM “Read Only Memory” de 16 x 16,es decir 16 elementos y un ancho de palabra de 16 bits en HDL (verilog, VHDL) (1 semanas) 1. Objetivo: El alumno conocerá la estructura de una memoria estática, de solo lectura. ROM (Read-only Memory): Una memoria de solo lectura, es una circuito combinacional y no tiene un estado interno. Su salida depende solo de la entrada (dirección de lectura). A pesar de que es un circuito combinacional, en esta práctica se realizara esta memoria de manera síncrona. Procedimiento: i. Diseñar una memoria tipo ROM capaz de mostrar 16 datos almacenados de 16 bits cada uno. a. Debe tener una señal de entrada de reloj, así como un bus para las direcciones de lectura (4 bits). Y una salida en un bus de 16 bits. Nombre del diseño: Memoria ROM. *Nota: Agregar en el reporte los valores predeterminados almacenados en la memoria y captura de pantalla de la simulación. Evaluación La calificación de cada práctica se divide en dos partes. 50% es correspondiente a la entrega funcional de la practica en hora clase y envío del proyecto, (toda la carpeta) en un solo archivo zip llamado, actividad_xx.zip a la plataforma proymoodle. Los Archivo(s) “.v” ó “.vhd” deben tener este formato al principio del archivo, (Fig.1) Fig. 1 Ejemplo de la cabecera de archivos .v/.vhd. La práctica se entregara con un reporte que debe contener al menos lo siguiente: Introducción Objetivos Desarrollo Conclusiones Se tomaran en consideración para la evaluación de la práctica además del contenido técnico de la misma, la escritura y formato de ésta.