sintetizador de frecuncia

Anuncio

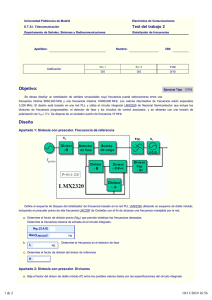

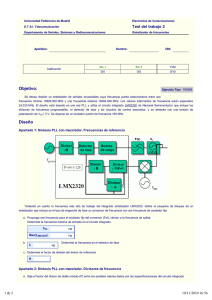

DISEÑO DE UN SINTETIZADOR DE FRECUENCIA INTEGRADO PARA RF (2.4 GHz) EN TECNOLOGÍA CMOS DE 0.35 µm Angel María Gómez Argüello, João Navarro Soares Jr. Escola Politécnica da Universidade de São Paulo, Brasil angelma@lsi.usp.br, navarro@lsi.usp.br SUMMARY The implementation of a CMOS Frequency Synthesizer for RF in 2.4 GHz (standar ISM – Industrial, Scientific and Medicine), using 0.35 µm CMOS technology (four metal levels and two polysilicon levels) is described. The Synthesizer employs the integer-N architecture and PLL, and is able to select sixteen different frequencies. The blocks composing the circuit are fully integrated and they include: a voltage controlled oscillator (VCO), a frequency divider, a phase frequency detector, a pump charge, and a low pass filter. Most of these blocks have design requirements that should be followed to assure the circuit correct operation. Particularly, the dual-modulus prescaler, one of the most demanding blocks in terms of speed and power consumption, was implemented using the Extended True Single Phase Clock Technique, and as result we obtained for this block high operation frequencies with reasonable power consumptions. In addition to the blocks descriptions and layouts, details of some system problems were presented and discussed, as for example: the need of amplifying the VCO output before applying it in the prescaler input to have the correct operation, the ripple generated in the charge pump that corrupts the VCO control voltage and degrades the phase noise characteristics, etc. RESUMEN La implementación de un Sintetizador de Frecuencia CMOS para RF en 2.4 GHz (estándar ISM – Industrial, Scientific and Medicine), utilizando tecnología CMOS de 0.35 µm (cuatro niveles de metal y dos niveles de polisilicio) es descrita. El Sintetizador emplea la arquitectura con PLL tipo integer-N, y es capaz de seleccionar entre 16 diferentes frecuencias. Los bloques que conforman el circuito son completamente integrados e incluyen: un oscilador controlado por voltaje (VCO), un divisor de frecuencia, un detector de fase y frecuencia, una bomba de carga, y un filtro pasa bajos. La mayoría de estos bloques tienen requerimientos de diseño que deben ser seguidos para asegurar la correcta operación del circuito. Particularmente, el dual-modulus prescaler, uno de los bloques más demandantes en términos de velocidad y consumo de potencia, fue implementado usando la técnica Extended True Single Phase Clock, y como resultado se obtuvo para este bloque, frecuencias de operación altas con razonable consumo de potencia. Además de las descripciones de los bloques y los layouts, detalles de algunos problemas del sistema completo son presentados y discutidos, como por ejemplo: la necesidad de amplificar la salida del VCO antes de ser aplicadas a la entrada del prescaler para la correcta operación, el ripple generado en la bomba de carga que corrompe el voltaje de control del VCO y degrada las características de ruido de fase, etc. DISEÑO DE UN SINTETIZADOR DE FRECUENCIA INTEGRADO PARA RF (2.4 GHz) EN TECNOLOGÍA CMOS DE 0.35 µm Angel María Gómez Argüello, João Navarro Escola Politécnica da Universidade de São Paulo, Brasil angelma@lsi.usp.br, navarro@lsi.usp.br RESUMEN Este paper describe el diseño de un sintetizador de frecuencia integrado para Radio Frecuencia (RF) utilizando tecnología CMOS de 0.35 µm. Este sintetizador está basado en una arquitectura con Phase-Locked Loop (PLL) tipo integer-N. Fueron implementados los siguientes bloques: Oscilador Controlado por Voltaje (VCO), divisor programable de frecuencia, detector de frecuencia y fase (PFD), bomba de carga e filtro pasa bajos; todos ellos completamente integrados dentro del circuito integrado (chip). El sintetizador genera 16 diferentes frecuencias dentro de un rango ISM (Industrial, Scientific and Medicine) de 2.4 GHz, espaciadas 4.5 MHz (valor definido para la frecuencia del reloj de referencia del circuito). Utilizando simulaciones realizadas después del postlayout del circuito se obtuvo un ruido de fase de -117 dBc/Hz con un offset de 1 MHz @ 2.4 GHz. Además de presentar la implementación del sintetizador de frecuencia, un objetivo importante de este trabajo es resaltar los problemas que limitan el desempeño y eficiencia del circuito, y como pueden ser mejorados. 1. INTRODUCCIÓN Los sistemas de telecomunicación inalámbricos han encontrado bastante aplicación en los últimos años y su avance se ha acelerado también. Cada vez es mayor la necesidad de diseñar circuitos que alcancen altas frecuencias de operación y además de eso, que operen con exigencias técnicas superiores, como por ejemplo: bajo consumo de potencia, poca utilización de área del chip y bajos niveles de ruido. Sólo hasta hace poco el diseño de circuitos integrados para RF comenzó a utilizar la tecnología CMOS para su implementación, ya que ahora es posible proyectar circuitos en CMOS con altas frecuencias de operación y bajos niveles de ruido. Además su bajo costo de producción y la posibilidad de implementar funciones analógicas y digitales en el mismo chip aceleró más su utilización. Uno de los bloques más importantes para un transceiver (circuito que desempeña las funciones de transmisor y receptor al mismo tiempo) es un sintetizador de frecuencia, ya que el genera la frecuencia base de operación del circuito, con la que operaran todos los demás bloques del transceiver. Es poco probable encontrar en la literatura técnica (papers o libros) información completa sobre algunos detalles específicos para el diseño de un sintetizador de frecuencia. La información encontrada es de carácter bastante general o sobre un campo específico de la implementación (por ejemplo el diseño del VCO, del divisor de frecuencia, del detector de fase, etc…). El presente estudio mostrará consideraciones globales así como particulares cuya implementación requiere especial cuidado para el buen desempeño de todo el circuito. 2. ESPECIFICACIONES DE DISEÑO El diseño de un sintetizador de frecuencia para altas frecuencias presenta un número elevado de dificultades de diseño, ya que cada bloque integrante del mismo debe ofrecer el mejor desempeño y al mismo tiempo contribuir lo menos posible con los niveles de ruido de todo el sistema. Algunos de los requerimientos del sintetizador proyectado son los siguientes: 2.1. Frecuencia de salida y resolución Fue escogida una frecuencia de salida nominal dentro del rango ISM de 2,4 GHz. Con el fin de poder acomodar información como datos, voz y video se escogió también una frecuencia en el orden de 4 MHz. Esta frecuencia también favorece la posterior prueba del chip. 2.2. Ruido de fase En la figura 1 se puede ver la diferencia de espectros entre un oscilador ideal y un oscilador real. Mientras en un oscilador ideal se espera tener sólo un impulso en frecuencia, en un oscilador real el espectro de frecuencia presenta componentes en un rango continuo alrededor de la frecuencia central. Esto debido a fluctuaciones aleatorias en las fuentes de oscilación. La señal deseada puede estar acompañada de una interferencia grande en un canal adyacente. Cuando las dos señales son mixturadas con la salida del Oscilador Local (LO), debido al ruido de fase de este, la señal resultante downconverted consiste de dos espectros sobrepuestos, con la señal deseada sufriendo de ruido no despreciable debido al efecto de la interferencia. Esto en el camino de recepción [ver figura 2 (a)]. Oscilador ideal Oscilador real ωc ωc ω ω Figura 1. Espectro de salida de un oscilador ideal y un oscilador real. Este trabajo fue soportado en parte por CNPq y FAPESP, Brasil. 1 (a) Señal deseada RF fref Señales downconverted Oscilador local Señal Interferencia deseada Interferencia LO Señal transmitida ω Señal deseada ω1 ω2 Figura 2. Efecto del ruido de fase en los caminos de: (a) recepción, y (b) transmisión. 3. ASPECTOS TEÓRICOS Existen diferentes arquitecturas para implementar un sintetizador de frecuencia [1]. De entre ellas se escogió una arquitectura comúnmente usada debido a su sencillez de implementación: la arquitectura tipo integer-N (ver figura 3). Esta arquitectura se caracteriza por ser un PLL que incorpora en el lazo de realimentación un divisor N, que divide por un factor entero la frecuencia de salida del Oscilador Controlado por Voltaje (VCO), fosc, comparando este valor con la frecuencia de referencia. De esta forma la separación entre canales será igual a la frecuencia de referencia. Este divisor está compuesto de: un contador principal, un prescaler, un swallow counter y la lógica de control necesaria. Inicialmente, los dos contadores, el contador principal y el swallow counter, son cargados con los valores P y S respectivamente, donde S ≤ P, la señal modulus control es alta, de tal forma que el prescaler dividirá por (V+1). Los dos contadores disminuyen su valor por cada ciclo de la salida del prescaler, hasta que el swallow counter llega a cero, cambiando el valor de la señal modulus control. El prescaler divide por V hasta que el contador principal llega a cero también. En este punto los dos contadores son inicializados nuevamente y el proceso comienza de nuevo. Así, el prescaler divide por (V+1), S veces, y divide por V, (P-S) veces. N=VP+S Prescaler ÷(V+1)/ ÷V Modulus Control ÷S Swallow Counter Selección de canal (b) 2.3. Tiempo de conmutación Inicialmente el sintetizador será controlado por medio de 4 datos digitales introducidos en un contador descendente programable, de tal forma que es posible obtener 16 diferentes frecuencias. Un tiempo de conmutación razonable entre cada frecuencia seleccionada permite utilizar el sintetizador en aplicaciones donde las conmutaciones de frecuencia sean constantes, de tal forma que el sintetizador de frecuencia no se convierta en el cuello de botella de un circuito transceiver. Se estableció un tiempo de conmutación máximo de 2 ms. fosc VCO Contador principal ÷P ω En el camino de transmisión el efecto es algo diferente [ver figura 2 (b)]. Suponiendo que un receptor ideal sin ruido tiene que detectar una señal en ω2, mientras que un transmisor cercano y potente genera una señal en ω1 con bastante ruido de fase, entonces la señal deseada será corrompida por el efecto del ruido de fase de este transmisor. El sintetizador de frecuencia proyectado corresponde a un estándar abierto. Se optó por tomar una especificación típica para el ruido de fase inferior a -110 dBc/Hz a un offset de 1 MHz. LPF ÷N IF ωc ω PD Figura 3. Arquitectura Integer-N. Por lo tanto, el factor de división total del divisor será: N=(V+1)S + V(P-S) = VP + S. Cuando el sintetizador está en estado locked, la frecuencia de salida del VCO será: fosc=N fref = (VP+S)fref. De esta forma, la frecuencia de salida del VCO será controlada por medio del valor programado S en el swallow counter. 4. BLOQUES CONSTITUTIVOS 4.1. Oscilador Controlado por Voltaje (VCO) Un Oscilador Controlado por Voltaje (VCO) genera una señal periódica con frecuencia dependiente de un voltaje de control. Los osciladores más utilizados en aplicaciones de circuitos integrados con PLLs son el oscilador LC sintonizado y el oscilador en anillo. El oscilador LC sintonizado ha tenido preferencia en los últimos años por su mejor desempeño en lo relativo a ruido de fase. Un esquema del circuito puede verse en la figura 4. Dos inductores son utilizados en serie en una configuración diferencial. Dos transistores NMOS, M1 e M2, son acoplados con realimentación positiva con el fin de proveer resistencia negativa. La salida del VCO debe ser alimentada después en la entrada del divisor de frecuencia, que utiliza como primer bloque, un prescaler, que requiere una amplitud pico a pico de la señal de entrada entre 0 V y el voltaje de alimentación, en este caso 3.3 V. La amplitud de la señal de salida del VCO es bastante baja, de 0.85 V, y por tanto es indispensable colocar un buffer amplificador entre la salida del VCO y la entrada del divisor (prescaler). Aquí se utilizó la solución presentada en la figura 5, que hace uso de tres buffers inversores con auto polarización. Estos buffers limitan el desempeño del circuito ya que consumen una potencia no despreciable (12.9 mW a VDD M3 3,1 nH Ibias=2 mA M4 Vc Vout- Vout+ M1 100/0,35 µm M2 Figura 4. Esquema del circuito oscilador LC sintonizado. 2 1 MΩ Salida 500 del fF VCO 30/15 20/10 Contador divisor por 4/5 20/10 Entrada del divisor Frecuencia de oscilación (Hz) Figura 5. Buffer inversor auto polarizado. D Q D-FF B D Q D-FF A C D Q D-FF clock 2,5G 2,4G sm 2,4G div8 2,3G 2,3G ckn8 D Q D-FF C Q 2,2G 2,1G 1,0 1,5 2,0 2,5 3,0 3,5 Voltaje de control (V) Figura 6. Resultado de la simulación del VCO: Frecuencia de oscilación vs. Voltaje de control. ELDO 5.6 Modelo MOS BSIM3v3. Parámetros típicos. 2.5 GHz) y además aumentan la carga capacitiva en la salida del VCO, lo que hace más lento el oscilador y para alcanzar frecuencias de oscilación grandes tendría que sacrificarse el margen de voltaje de control, aumentando la influencia de cualquier ruido sobre el VCO. El VCO fue implementado en tecnología CMOS de 0.35 µm, y con base en simulaciones post-layout se obtuvo la curva Frecuencia vs. Voltaje de Control mostrada en la figura 6. Con base en esta curva se obtiene la constante de transferencia del VCO igual a KVCO = 112 MHz/V = 709 Mrad/s. 4.2. Divisor de frecuencia El tipo de divisor de frecuencia define la arquitectura utilizada para el sintetizador de frecuencia. Fue explicado en la sección de aspectos teóricos como funciona el mismo. Considerando que la frecuencia nominal del sintetizador es de 2.4 GHz y la frecuencia de referencia está en el orden de los 4 MHz; en este caso los valores más convenientes para configurar el divisor son: • • • El prescaler dividirá por 32 o 33 (V=32); El contador principal tendrá um valor fijo de P=16; El swallow counter tendrá valores S entre 0 y 15 (así tendrá 4 bits para seleccionar la frecuencia). Así con N=VP+S, N variará entre 512 y 527 y: 512Fref ≤Fosc ≤ 527Fref. 4.2.1. Prescaler El bloque más importante del divisor es el prescaler pues tiene que trabajar con la frecuencia de operación más alta que es la salida del VCO. En este caso se utilizó un dual-modulus prescaler (que divide por 32 o por 33) implementado con la técnica Extended – True Single Phase Clock (E-TSPC) [2]. La figura 7 muestra el diagrama esquemático del mismo. Dos partes pueden identificarse en el diagrama: la primera parte, dentro de la caja sombreada, se compone de tres D-flip flops (D-FF) sensibles al flanco de bajada y ckn32 ckn16 2,2G D Q D-FF C Q D Q D-FF C Q Out 32/33 Figura 7. Diagrama esquemático del Dual-Modulus Prescaler (divisor por 32/33). dos puertas lógicas, que forman un contador divisor por 4/5 sincrónico; la otra parte, en la parte inferior de la figura, se compone de tres D-FFs sensibles al flanco de subida, y forman un contador divisor por 8 asincrónico. La señal div8, generada por el contador asincrónico, selecciona si el contador divisor por 4/5 cuenta por 4 (div8 = alto) o por 5 (div8 = bajo). El factor de división fraccional del prescaler, 32 o 33, es seleccionado de acuerdo al valor de la señal sm. Las dimensiones óptimas de los transistores que conforman el prescaler fueron calculadas y ajustadas por medio de simulación (ELDO 5.6 Modelo MOS de los transistores: BSIM3v3). La figura 8 muestra el esquema a nivel de transistores del prescaler con las 2.5 1.7 1.4 2.0 2.2 1.7 1.4 2.5 1.0 2.2 1.7 1.4 ckin ckin 1.0/0.8 3.1 1.01.0/0.8 3.1 2.6 ckin ckin 2.6 1.0 ckin ckin 2.6 1.0 ckin 3.1 1.0/0.8 ckin ckin ckassyncr D 1.0 1.0 3.0 div8 Q sm 2.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 C Q 1.0 ckn8 1.0 ckn16 D Q D-FF C Q 1.0 D Q D-FF C Q ckn32 out 32/33 Figura 8. Esquema a nivel de transistores del prescaler. El ancho del transistor o, cuando la longitud es diferente de 0.35 µm, la relación ancho/longitud en µm, es indicada también en la figura. 3 dimensiones de todos los transistores. fosc 4.2.2. Contador Principal El contador principal trabaja con un valor fijo, mientras el swallow counter trabaja con un valor programado. El contador principal fue implementado por medio de 4 TSPC D-FFs en serie, de forma análoga a la parte asincrónica del prescaler, y su conteo es de 16 (ver figura 9). 4.2.3. Swallow Counter Este contador es básicamente un contador descendente programable, cuyo valor S es cargado inicialmente, y después si está activa la señal de habilitación, comienza a contar en sentido descendente. Cuando su valor llega a cero, el swallow counter puede volver a contar o no desde el valor S, dependiendo del estado de la señal de habilitación. Existen diversas arquitecturas para implementar este contador. Aquí se implementó la arquitectura mostrada en la figura 10 [3] utilizando TSPC D-FFs convencionales. 4.2.4. Lógica de control La lógica de control maneja las diferentes señales en el momento exacto de tal forma que el divisor funcione como es esperado. El control usado en este trabajo consiste básicamente de un multiplexor y una puerta lógica OR de 4 entradas (ver figura 11). El funcionamiento de la lógica de control es el siguiente: comenzando el análisis por la salida del swallow counter, si en el primer ciclo de reloj todas sus salidas son cero, entonces la salida de la puerta OR será también cero. Como resultado, /lo=“low”, el swallow counter es inicializado con los valores (IA … ID), e inmediatamente la salida de la puerta OR es forzada a un valor Fin D Q D Q D Q D Q D-FF D-FF D-FF D-FF C Q C Q C Q C Q Fin /8 Fin /16 Fin /4 Fin /2 fout out Contador Principal VCO Prescaler sm 32/33 out32/33 outMux swallow counter mux ck QA /lo Q B IA Dato QC I B “S” QD IC ID Figura 11. Esquema de la lógica de control. “alto”. El proceso de inicialización es interrumpido. Con sm=/lo=”alto”, el prescaler dividirá por 33. El swallow counter recibirá como reloj los pulsos provenientes de la salida del prescaler (por medio del multiplexor mux). Cuando el swallow counter alcanza el valor cero, sm=/lo=”0”, el prescaler dividirá por 32, y el reloj del swallow counter será la salida del contador principal que aún está en cero. En este momento, el swallow counter tiene la señal /lo=”0”, y está esperando el pulso de salida del contador principal para inicializarse con el dato (IA … ID) y comenzar el conteo de nuevo. En la figura 12, el layout de todo el divisor es presentado. Fue agrupado el contador asincrónico del prescaler, el contador principal, el swallow counter y la lógica de control lo más cerca posible para evitar demoras en los caminos de las señales (parte derecha de la figura). El contador sincrónico esta aislado en la parte izquierda, rodeado de un anillo de guarda para reducir el ruído de conmutación introducido en el substrato. La simulación de la lógica de control es mostrada en la figura 13. Los datos programados en el swallow counter usando las Figura 9. Contador Principal. clock /load IA Figura 12. Layout del divisor completo (arquitectura Integer-N). DQ QA 4 2 0 DQ QB volts IB IC DQ QC 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 4 2 0 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 4 2 0 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 4 2 0 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 4 2 0 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 0,0 100,0n 200,0n 300,0n 400,0n 500,0n 600,0n 4 2 0 ID DQ QD ckout32 4 2 0 4 2 0 out outmux sm Qa Qb Qc Qd t (sec) Figura 10. Esquema del Swallow Counter. Figura 13. Simulación de las señales de la lógica de control. ELDO 5.6, modelo del transistor BSIM3v3, parámetros típicos. 4 entradas IA a ID fueron: IA=”alto”, IB=”alto”, IC=”alto” and ID=”bajo”. Con estos datos S=7 y N=519. 4.3. Detector de fase y frecuencia La diferencia de fase entre la señal de referencia y la salida del oscilador después de pasar por el divisor es detectada en un circuito detector de fase y frecuencia, PFD. Tal diferencia de fase es convertida en corriente o voltaje para controlar el VCO. Existen diversas configuraciones para realizar esta labor [4]. Dentro de ellas la más popular es la configuración mostrada en la figura 14 (a), cuyo funcionamiento es de la siguiente forma: El PFD tiene dos salidas, Up e Dn, que abren o cierran las dos fuentes de corriente de la bomba de carga. Hay cuatro posibles estados de funcionamiento: en el primer estado, una señal activa en Up origina que la fuente de corriente superior sea activada, resultando una corriente de salida Ic positiva. Esta corriente causa que el voltaje de salida C crezca. Este es el estado de pump-up. En el segundo estado, una señal activa en Dn origina que la fuente de corriente inferior sea activada, resultando una corriente de salida Ic negativa. Esta corriente causa que el voltaje de salida C disminuya. Este es el estado de pump-down. El tercer posible estado de la bomba de carga es aquel donde ninguna de las señales Up o Dn está activa. La corriente de salida es cero y el nodo C es un nodo de alta impedancia. El cuarto estado, aquel con las dos fuentes de (a) 1 Ref Div 1 VDD Q D D-FF CLK R reset Up I R CLK D-FF Q D C Zlf I Dn T τ (b) IC Ref Div IC (c) Valor medio de C -1 -0.5 0 0.5 1 τ /T corriente activas, nunca sucede debido a un mecanismo de reset. La corriente de salida es convertida a voltaje en la impedancia Zlf . El principio de operación del PFD es mostrado es la figura 14 (b). Un flanco de subida del pulso de referencia origina que la señal Up sea activada y con eso la tensión de salida comience a aumentar; similarmente, un flanco de subida del pulso del divisor de loop origina que la sinal Dn sea activada y con eso la tensión de salida comience a disminuir. Cuando las dos señales, Up e Dn, están simultáneamente activadas, una puerta AND origina que estas señales sean desactivadas (reset del PFD) La salida media del voltaje en función de la fase es mostrada en la figura 14 (c). El rango de trabajo linear es de 720o. El problema mas importante de este circuito tiene relación com la llamada “zona muerta”, que ocurre cerca del error de fase cero [5], [6]. Si los dos pulsos, el de referencia y el del divisor, aparecen en instantes próximos (diferencia de fase pequeña) el reset del PDF puede ser activado sin que ninguna de las fuentes de corriente haya conducido (dependiendo de los atrasos del circuito), lo que dejará la salida C en alta impedancia. Con eso, valores pequeños del error de fase no serán nunca corregidos. La característica del PFD tiene realmente una respuesta plana, una “zona muerta”, cerca de la diferencia de fase cero (ver figura 15). El PLL estará ahí efectivamente abierto, y el espectro de salida se modificará por lo tanto. Este fenómeno es solucionado de diversas formas [5], [6]. Una solución simple es la de no permitir el reset antes que un pulso de un ancho mínimo sea aplicado a la bomba de carga. De esta forma, aún si no hay una diferencia de fase entre las dos entradas del PFD, las dos salidas Up e Dn estarán activas durante un intervalo corto de tiempo [4]. Una forma bastante utilizada de implementar este PFD es con la arquitectura común y de bastante complejidad presentada en la figura 16 [7]. Esta configuración, sin embargo, tiene algunos problemas como una zona muerta grande. También, si este circuito trabaja a frecuencias no tan bajas, se presenta un consumo de potencia inevitable debido a que los nodos internos del PFD no son completamente llevados a estado pull up o pull down. Además de esto, el alto número de transistores necesarios para su implementación puede introducir ruido de fase dentro del circuito sintetizador completo, lo que se pretende evitar desde el principio. En este trabajo se utilizó una estructura para el PFD que hace uso de un número menor de transistores y está optimizada para trabajar a frecuencias de operación mayores y con menor consumo de potencia [5]. Este circuito está basado en una estructura TSPC [8] modificada con Flip-Flops tipo D edge triggered, cuya R (señal) Up Figura 14. (a) Detector de Frecuencia y Fase, (b) Operación, (c) Característica de Transferencia. Valor medio de C “zona muerta” (longitud exagerada) -1 -0.5 0 0.5 1 τ /T Figura 15. Característica de Transferencia del PFD con “zona muerta”. Dn V (VCO) Figura 16. Detector de Fase y Frecuencia convencional 5 detección de error de fase y frecuencia no está limitada (ver figura 17). Este flip-flop funciona de la siguiente forma: cuando las señales de reset y de entrada del reloj son bajas, el nodo A está conectado a VDD a través de m1 y mr1. En el flanco de subida de la señal de reloj, el nodo B está conectado a tierra a través de m3 y m4. Mientras el nodo A esté cargado a VDD, se previene que el nodo B sea pulled up a través de m2, y por tanto no tiene influencia una señal diferente de reloj de flanco de subida. Cuando se aplica la señal de reset, el nodo A se desconecta de VDD en mr1, y se conecta a tierra a través de mr2. Así que el nodo A es descargado, el nodo B es pulled up a través de m2. El circuito fue implementado utilizando tecnología CMOS de 0.35 µm (ver layout en la figura 18). En la mitad derecha de la figura se observan los dos flip-flops D, el flip-flop inferior recibe la señal del reloj de referencia, y el flip-flop superior recibe la señal de la salida del divisor de frecuencia. Posteriormente las salidas de los flip-flops son llevadas a una puerta AND (parte izquierda de la figura) que se encarga de generar la salida de reset. En la figura 19 (a) se puede observar los resultados de la simulación post-layout del circuito detector de fase y frecuencia. Fue colocado un buffer inversor en la entrada de cada flip-flop con el fin de mejorar las señales de entrada hacia el PFD. En la figura 19 (b) se presenta un detalle de la demora existente entre la orden de reset, debida a la aparición simultánea de las señales up y dn provenientes del PFD, y la generación del reset propiamente dicho. Esta demora, en este caso de 275 ps, tiene como fin aliviar el problema de la “zona muerta” inherente a este circuito, como ya fue explicado anteriormente. (a) (b) 3,5 3,0 dn reset 2,5 4.1.1. Entrada Clock de referencia Existen diferentes estándares para definir el ancho del canal para las diferentes bandas de transmisión o recepción en un sistema RF (ver tabla 1). Tal ancho de canal influye en la magnitud de la frecuencia de referencia dependiendo de la arquitectura volt 2,0 1,0 0,5 0,0 -0,5 ck ck m1 m2 mr1 in mr2 m3 1.0/1.5 3.0/1.0 m2 5.0/0.35 ck m7 m1 B out out mr1 m3 1.0/1.0 1.0/1.5 m6 Reset A m4 ck ck m5 m4 1.0/0.35 mr2 1.0/1.5 4.0/0.35 Figura 17. (a) Flip Flop Svenson Original, (b) Esquema del circuito Flip-Flop-D modificado para el detector de fase y frecuencia. Figura 18. Layout del circuito detector de fase y frecuencia. 275ps 1,5 752,5n 753,0n 753,5n 754,0n 754,5n 755,0n t (sec) Figura 19. (a) Simulación post-layout del PFD, (b) Detalle de la demora entre la aparición simultânea de up y dn y la generación de la señal de reset (solo se muestra dn por claridad). seleccionada para el sintetizador de frecuencia [1]. Para la arquitectura integer-N la magnitud del ancho del canal es igual a la magnitud de la frecuencia de referencia. Tabla 1. Bandas de Frecuencias y anchos de banda para diferentes estándares de RF. Estándar Banda TX Banda RX Ancho del canal BW IS-54 824-849 MHz 869-894 MHz 30 KHz IS-95 824-849 MHz 869-894 MHz 1.25 MHz GSM 890-915 MHz 935-960 MHz 200 KHz DECT 1.88-1.9 GHz 1.88-1.9 GHz 1.728 MHz 6 En este proyecto se optó por trabajar dentro del sistema ISM (Industrial, Scientific and Medicine) que es un sistema abierto dentro de cierto rango de frecuencias. Se trabajó en la frecuencia nominal de 2.4 GHz y se usó una frecuencia entre 4 y 4.5 MHz para la separación de canales, pensando en poder transmitir datos, audio o video; además con una frecuencia mayor el PLL es más estable y tiene menos problemas de ruido de fase [4]. 4.2. Bomba de carga y filtro pasa bajos En el numeral anterior se explicó junto con el PFD, el funcionamiento de la bomba de carga (ver figura 4). Gardner analizó en su paper clásico de 1980 [9] este circuito típico de bomba de carga, identificando características sobresalientes y proporcionando ecuaciones y gráficas para el diseño del mismo. Después de varios años de su utilización diversos problemas han sido estudiados y diversas soluciones han sido presentadas. Aquí se mostrará una solución propia para diseñar esta bomba de carga. El correcto diseño de la bomba de carga y el filtro pasa bajos está bastante influenciado por el comportamiento general de todo el sintetizador de frecuencia y por eso se hace necesario entender el modelo lineal del mismo (considerando correcto usar el modelo lineal cuando el PLL esté en estado locked) (ver figura 20). La función de transferencia del sintetizador, H(s), es igual a: H (s) = θ out ( s) θ ref ( s) = K PD KVCO F ( s ) K K F (s) s + PD VCO N Cuando se hace uso de la bomba de carga el filtro comúnmente usado para el loop está formado por un resistor y un condensador en serie, obteniendo la configuración mostrada en la figura 21. Es posible demostrar que la constante KPD de la bomba de carga [9] es igual a KPD =I/(2π) amp/rad, remplazando este valor y la función de transferencia del filtro RC se obtiene la siguiente función de transferencia: Filtro del loop Detector de fase θref + Σ θe F(s) KPD θfb vc VCO KVCO/s θout 1/N Divisor del loop Figura 20. Modelo lineal del sintetizador de frecuencia. VDD I Up x(t) PFD Dn IC CP I VCO y(t) R 1/N Figura 21. Sintetizador de frecuencia com bomba de carga. I ( RCP s + 1) KVCO 2π C P H ( s) = I 1 I 1 s2 + KVCO Rs + KVCO 2π N 2π C P N De donde la frecuencia natural del circuito es igual a: ωn = KVCO I 2π C P N (1) (independiente del valor de R), con un factor de amortiguamiento dado por: R IC P KVCO ω n RC P (2) = N 2 2π 2 Normalmente se escoge el factor de amortiguamiento, ζ, igual a 0,7 por cuestiones de estabilidad del loop [10]. Gardner también derivó un límite de estabilidad, haciendo análisis de tiempo discreto, lo que implica un valor máximo para ωn. En proyectos típicos, el ancho de banda del loop es fijado en un décimo de la frecuencia de entrada para garantizar estabilidad [11]. El ancho de banda del loop anterior, puede ser encontrado y tiene la siguiente forma [12]: ζ = ω 3dB = ω n 2ζ 2 + 1 + ( 2ζ 2 + 1) 2 + 1 1 2 (3) La interacción debida a la conmutación entre la bomba de carga y el filtro del loop causa una gran cantidad de ripple en el voltaje de control del VCO. Este ripple puede ser suprimido agregando un pequeño condensador C2 en paralelo con el filtro del loop. La adición de este condensador C2 agrega otro polo a la función de transferencia y convierte el sistema en un sistema de tercer orden. Por otro lado si el condensador es pequeño lo suficiente (C2 < 0,1 CP) el sistema puede continuar siendo analizado como un sistema de segundo orden [13]. El valor de este condensador C2 se obtiene de la capacitancia presente en la entrada de control del VCO: capacitancias parásitas presentes en las líneas de metal, de la capacitancia de pozo y de la capacitancia de los varactores. De los datos del layout se obtiene que C2=1.9 pF. Tomando ωref = 4.5 MHz, entonces, el ancho de banda del PLL será por recomendación: ω3 dB = ωref / 10 = 4.5 MHz/10 = 0.45 MHz = 2.8274 Mrad/s. De la ecuación (3), reemplazando ζ por 0.7 se obtiene ωn = 1372.5 Krad/s. En el numeral 4.2 se encontró que el factor de división N varía entre 512 y 528; se utilizó una media de este valor N = √(512*528) = 520. El valor del condensador CP se escoge 10 veces mayor que el valor de C2, y así CP=19 pF. También en el numeral 4.1 se encontró KVCO=709 Mrad/s. Usando ecuación (1) se obtiene la corriente necesaria en la bomba de carga como I=165 µA. Finalmente de la ecuación (2) se obtiene R=103 KΩ. Con estos valores se consigue la bomba de carga básica mostrada en la figura 22. Sin embargo, después de implementarse este circuito se encontraron diversos problemas ya bastante documentados en la literatura [14], [15], [16]. • Cuando los dos interruptores (transistores m1 y m2) están en estado “off” (up y dn en estado “bajo”) hay fugas de corriente entrando y saliendo del nodo de control. Las dos corrientes pueden no ser iguales resultando en una carga neta saliendo o entrando del filtro. • Cuando ambos interruptores están en estado “on” el efecto es parecido al anterior. 7 VDD VDD m1 235/2 up m2 235/2 A m3 10.0/1.0 m7 67/2 m6 m4 B CP m5 R 20.0/0.4 20.0/0.4 VC1 VREF C2 10.0/1.0 67/2 67/2 120.0/1.0 Vc 165 µA dn 10.0/1.0 10.0/1.0 10.0/1.0 15 µA Figura 22. Esquema de la bomba de carga básica. Dimensiones de los transistores en µm. • Existe un desbalance dinámico cuando los interruptores tienen diferentes tiempos de conmutación para abrir o cerrar las fuentes de corriente. • Nuevamente cuando los dos interruptores están “off”, el voltaje de control VC está flotando. Aunque el voltaje de control no varía, el voltaje en el nodo A es “pulled up” a VDD y el voltaje en el nodo B es “pulled down” a VSS. Los fenómenos anteriores causan discontinuidades en el voltaje de control que aumentan los problemas de ruido de fase del oscilador así como originan tonos “espurios” que modifican el espectro de salida del VCO. Estos problemas fueron disminuidos con la arquitectura implementada mostrada en la figura 23, de la siguiente forma: Cuando las fuentes de corriente son conmutadas durante el estado “off” su corriente es llevada a un voltaje de referencia VREF, por medio de un amplificador operacional cuya implementación se observa en la figura 24. De esta forma se disminuye el valor de los saltos de voltaje cada vez que ocurre el estado “off” evitando que el valor de voltaje de los nodos A o B se aleje del valor del voltaje de control. Fue necesario entonces colocar otra sección de switches del lado izquierdo para esta función. Cada switch es implementado por medio de la señal up o dn necesaria y su complemento, para disminuir problemas de inyección de cargas hacia y desde el nodo de voltaje de control. VDD m2 m1 235/2 165 µA up2 235/2 nup2 A up2 ω up m3 nup2 nup VREF ndn2 m7 67/2 67/2 dn dn2 m4 B m5 m6 67/2 dn2 ndn VC1 R2 Figura 24. Esquema del amplificador operacional. Dimensiones de los transistores en µm. Por medio de simulaciones se encontró que debido a las diferencias en los tiempos de conmutación se presentaban algunos problemas de saltos de voltaje si se utilizaban las mismas señales up y dn en las dos secciones de switches, por tal razón las señales de los switches de la sección izquierda presentan una demora con respecto a las señales de la sección derecha. Finalmente, con el fin de atenuar aún más la presencia de “espurios” que inevitablemente pasan hacia la tensión de control, se agregó un polo adicional pasa bajos al filtro del loop. Este filtro adicional está siendo más utilizado en aplicaciones exigentes de sintetizadores de frecuencia para estándares de telefonía celular digital TDMA, como por ejemplo GSM, PDC, PHS o IS-54 [17]. Este polo adicional debe ser más bajo que la frecuencia de referencia, con el fin de atenuar los “espurios”, y 5 veces más grande que el ancho de banda del loop con el fin de evitar inestabilidad. Normalmente se escoge el valor del producto de R2 y C3, como al menos un décimo del producto de CP y R [18]. Aquí se escogió R2=103 KΩ y C3=1.9 pF. 5. RESULTADOS DE SIMULACIÓN GENERALES Tiempo de conmutación: 20 µs. VC CP R C2 C3 ndn2 Figura 23. Esquema de la bomba de carga mejorada. Dimensiones de los transistores en µm. Figura 25. Simulación de la respuesta del voltaje de control contra el tiempo, para medir el tiempo de conmutación del sintetizador de frecuencia. ELDO 5.6 Modelo MOS BSIM3v3. Parámetros típicos. 8 [3] G. Reehal, “A Digital Frequency Synthesizer Using Phase Locked Loop Technique”, Tesis (Maestría), The Ohio State University, 1998. Ruido de Fase (dBc/Hz) 0 -20 -40 -60 -80 -100 -117 dBc/Hz @ 1M Hz -120 -140 -160 100 1k 10k 100k 1M 10M 100M Offset (Hz) Figura 26. Simulación de ruído de fase del sintetizador de frecuencia para 2.4 GHz: -117 dBc/Hz @ 1 MHz. ELDO 5.6 Modelo MOS BSIM3v3. Parámetros típicos. Todo el sintetizador fue diseñado, realizándose su layout para un proceso AMS CMOS de 0.35 µm (C35B4/CSI). Se obtuvo un tiempo de conmutación para que el voltaje de control se estabilice en el valor deseado de 20 µs, muy por debajo de los 20 ms de la especificación (figura 25). Igualmente la simulación del ruido de fase arrojó un ruido de -117 dBc/Hz a un offset de 1MHz, para una frecuencia de oscilación de 2.4 GHz del oscilador, también por debajo de -110 dBc/Hz de la especificación (figura 26). El circuito consume una potencia total de 120 mW, distribuidos así: • VCO con buffer para amplificación de señal al divisor: 95 mW. • Divisor de frecuencia: 7 mW. • PFD más bomba de carga más filtro: 18 mW. Finalmente el área total del circuito, incluyendo pads externos fue de: 1450 µm x 1145 µm. 6. CONCLUSIONES Fue implementado un sintetizador de frecuencia completamente integrado para 2.4 GHz, en tecnología CMOS de 0.35 µm. Se mostró el proyecto de un divisor de frecuencia utilizando dualmodulus prescaler, de un detector de frecuencia y fase, asi como la bomba de carga junto con el filtro pasa bajos. También se usó un oscilador LC para el VCO. Cada bloque del diseño de este circuito demanda criterios de diseño específico, más que deben tener en cuenta el desempeño global de todo el conjunto. Dentro de este trabajo se presentó una forma de obtener este objetivo, resaltando algunos problemas que hacen que sea difícil obtener las especificaciones buscadas de antemano. 7. REFERENCIAS [1] B. Razavi, “Challenges in the Design of Frequency Synthesizers for Wireless Applications”, Custom Integrated Circuits Conference, IEEE 1997. [4] J. Cranickx; M. Steyaert, “Wireless CMOS Frequency Synthesizer Design”, Boston, Kluwer Academic Publishers, 1998. [5] W. Lee; et al. “A High-Speed, Low-Power Phase Frequency Detector and Charge-Pump Circuits for High Frequency Phase-Locked Loops”, IEICE Trans. Fundamentals, Vol. E82-A, No. 11, Nov. 1999. [6] O. Chen; R. Sheen, “A Power-Efficient Wide-Range PhaseLocked Loop”, IEEE Journal of Solid-State Circuits. Vol. 37, No. 1, Jan. 2002. [7] R. E. Best, “Phase-Locked Loops: Design, Simulation, and Applications, 4th Edition”, New York, McGraw-Hill, 1999. [8] I. Karlsson; C. Svensson, “A True Single-Phase-Clock Dynamic CMOS Circuit Technique”, IEEE Journal of SolidState Circuits, Vol. SC-22, No. 5, Oct. 1987. [9] F. M. Gardner, “Charge-Pump Phase-Lock Loops”, IEEE Transactions on Communications, Vol. COM-28, No. 11, Nov. 1980. [10] K. Ogata, “Modern Control Engineering”, New Jersey, Prentice Hall International, 1970. [11] B. Razavi, “RF Microelectronics”, New Jersey, Prentice Hall, 1998. [12] U. L. Rohde, “Microwave and Wireless Synthesizers: Theory and Design”, New York, John Wiley & Sons, 1997. [13] R. J. Baker; H.W. Li; D. Boyce, “CMOS: Circuit Design, Layout and Simulation”, New Jersey, IEEE Press, Piscataway, 1998. [14] W. Rhee, “Design of High-Performance CMOS Charge Pumps in Phase-Locked Loops”, IEEE International Symposium on Circuits and Systems (ISCAS), may 1999. Vol. 2, p. 545 – 548. [15] R.C. Chang; L. Kuo, “A New Low-Voltage Charge Pump Circuit for PLL”, IEEE International Symposium on Circuits and Systems (ISCAS), may 2000. p. 701 – 704. [16] E. Juárez, A. Diaz, “A Novel CMOS Charge-Pump Circuit with Positive Feedback for PLL Applications”, The 8th IEEE International Conference on Electronics, Circuits and Systems. ICECS, sep 2001. Vol 1. p. 349 – 352. [17] “An Analysis and Performance Evaluation of a Passive Filter Design Technique for Charge Pump PLL’s”, National Semiconductor Application Note 1001 July 2001. [18] “Design Loop Filters for PLL Frequency Synthesizers”, Microwaves & RF, Sep. 1999. [2] J. Navarro; W. Van Noije, “A 1.6-GHz Dual Modulus Prescaler Using the Extended True-Single-Phase-Clock CMOS Circuit Technique (E-TSPC)”, IEEE Journal of SolidState Circuits. Vol. 34, No. 1, Jan 1999. 9