Tema 9. SISTEMAS COMBINACIONALES PROGRAMABLES

Anuncio

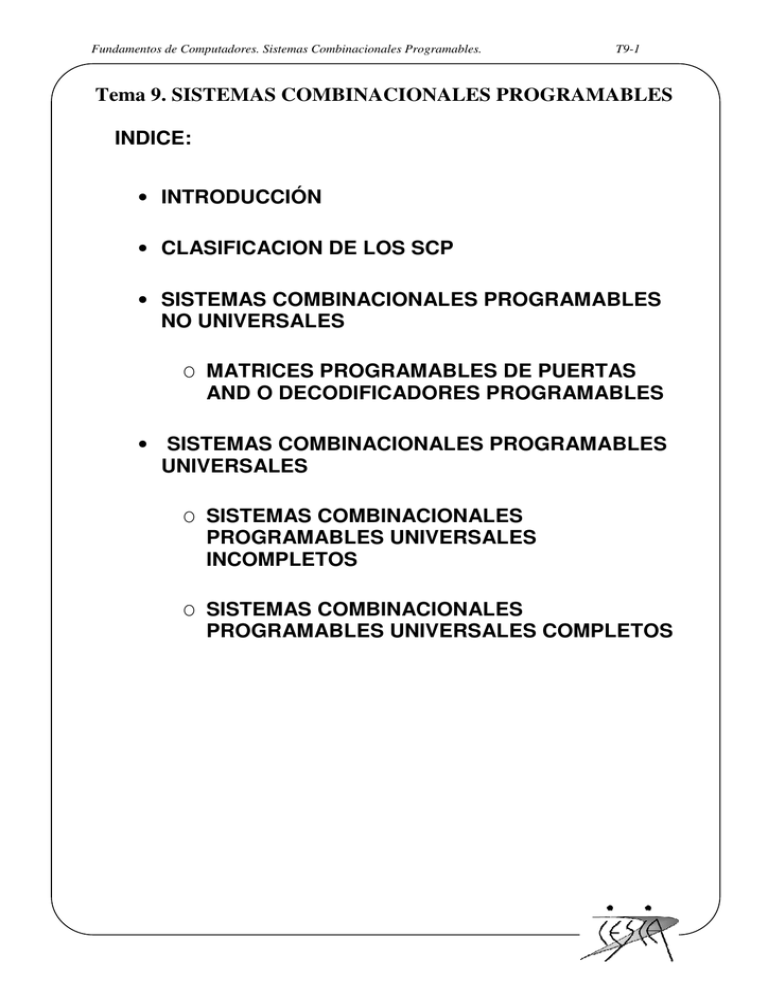

Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-1 Tema 9. SISTEMAS COMBINACIONALES PROGRAMABLES INDICE: • INTRODUCCIÓN • CLASIFICACION DE LOS SCP • SISTEMAS COMBINACIONALES PROGRAMABLES NO UNIVERSALES O MATRICES PROGRAMABLES DE PUERTAS AND O DECODIFICADORES PROGRAMABLES • SISTEMAS COMBINACIONALES PROGRAMABLES UNIVERSALES O SISTEMAS COMBINACIONALES PROGRAMABLES UNIVERSALES INCOMPLETOS O SISTEMAS COMBINACIONALES PROGRAMABLES UNIVERSALES COMPLETOS Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-2 INTRODUCCION Un sistema combinacional programable puede definirse como aquel cuya tabla de verdad puede ser cambiada, sin modificar el cableado entre los elementos que lo constituyen. Los dispositivos lógicos programables incorporan una matriz lógica genérica, que puede programarse de forma que el dispositivo (circuito integrado) realice las funciones que se desee. Normalmente la estructura programable principal consiste en una estructura combinacional, formada por una matriz de puertas AND, a cuyas entradas se conectan las entradas del dispositivo tanto de forma directa como negada. Según el tipo de dispositivo del que dispongamos, esta primera matriz estará o no seguida de una segunda matriz formada en el caso más general por puertas OR, de manera que pueda realizarse fácilmente una suma de productos. Las matrices programables están formadas por fusibles, que el usuario puede eliminar o dejar intactos para generar la lógica deseada. Para simplificar la representación de estas estructuras, las diferentes entradas de una puerta AND se representan con una sola línea denominada línea producto. En la figura 1a se representan cómo se sitúan los fusibles y en la figura 1b la representación gráfica, donde se observa que un fusible intacto se representa con una 'X' y un fusible eliminado sin ningún símbolo especial en la unión correspondiente. Figura 1. Fusibles y línea producto en una puerta AND. Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-3 CLASIFICACION DE LOS SCP En la figura siguiente se presenta una clasificación general de los sistemas combinacionales programables: • No universales • Matrices programables de puertas Y (Programmable Gate Array [PGA] ) • Matrices Lógicas programables (Programmable Logic Array [PLA] ) SISTEMAS • Incompletos COMBINACIONALES PROGRAMABLES • Matrices lógicas Y - programables (Programmable Array Logic [PAL] ) • Universales • Completos • Memorias de acceso aleatorio pasivas (ROM, PROM, EPROM, EEPROM) • Memorias de acceso aleatorio activas (Random Access Memory [RAM] ) Clasificación de los sistemas combinacionales programables. Sistemas combinacionales programables no universales Los sistemas combinacionales programables no universales son dispositivos programables que realizan funciones específicas de aplicación general. Existen ciertas funciones lógicas que, a pesar de no ser universales, presentan numerosas aplicaciones y por tanto resulta interesante su programación. Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-4 Matrices programables de puertas AND o decodificadores programables Las matrices programables de puertas AND, constan de un conjunto n’ de dichas puertas, conectadas a un número n de variables de entrada y a sus inversas. El número de puertas n’ es inferior a 2n y, mediante la supresión de las conexiones adecuadas, se logra que la salida de cada una de ellas constituya un producto canónico de entre los 2n posibles. De lo expuesto anteriormente puede deducirse que este circuito constituye un decodificador programable. La estructura interna general de un circuito de este tipo puede observarse en la figura siguiente: I0 I1 .. .. . ... ... ... In-1 ........ Pi O0 Pj O1 Pk On’- Como puede apreciarse en la figura, cada puerta AND posee 2n entradas que se conectan a cada una de las n variables de entrada, tanto en su forma directa como invertida. La figura anterior puede representarse también de la forma que se explicó en la introducción, en la cual, todas las conexiones de entrada de las puertas AND se representan mediante una sola línea (línea producto). Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-5 I0 I1 .. .. . In-1 ........ Pi O Pj Pk ’ On’- O Estructura interna general simplificada de una PGA. El símbolo lógico de una PGA con cuatro entradas y ocho salidas se representa a continuación: PGA I0 I1 I2 I3 (8) 0 1 2 3 4 5 6 7 La estructura interna de la PGA anterior, programada para generar los términos producto P0, P3, P6, P8, P10, P12, P14 y P15 es la siguiente: I0 I1 I2 I3 P0 O0 P3 O1 P6 O2 P8 O3 P10 O4 P12 O5 P14 O6 P15 O7 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-6 Y la tabla de programación correspondiente es: O0 O1 O2 O3 O4 O5 O6 O7 I3 L L L H H H H H I2 L L H L L H H H I1 L H H L H L H H I0 L H L L L L L H VAR En la siguiente figura se observa la estructura de una PGA real, concretamente la PLS103. Es un dispositivo 16 x 9 x 9), es decir, dispone de 15 entradas, y es capaz de generar hasta 9 términos producto, tanto en su forma directa (tipo AND) como en su forma inversa (equivalente a puertas NAND). Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-7 A continuación se muestra la tabla de programación del dispositivo PLS103. Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-8 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-9 Sistemas combinacionales programables universales Los sistemas combinacionales programables universales son aquellos dispositivos programables que permiten la implementación de cualquier función lógica. Existen dos tipos de sistemas combinacionales programables universales: • S. C. P. incompletos. • S. C. P. completos. Sistemas combinacionales programables universales incompletos Son aquellos dispositivos en los que no es posible programar el valor de las variables de salida, de manera individual, para cada combinación de las variables de entrada. Estos dispositivos están constituidos por una matriz de puertas AND conectada a otra matriz de puertas OR, tal como se representa en la figura. Variables de entrada n MATRIZ DE PUERTAS AND n’ MATRIZ DE PUERTAS OR m Variables de salida Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-10 Según la forma en que se realiza la conexión entre las puertas AND y las OR, pueden considerarse dos tipos de sistemas combinacionales programables universales incompletos: -Arquitectura "AND Programable - OR Programable". Ambas matrices son programables. Se conoce como PLA (Programmable Logic Array: 'Matriz lógica programable'). -Arquitectura "AND Programable - OR Fija". Sólo la matriz AND es programable. Se conoce como PAL (Programmable AND Array Logic: 'Matriz lógica "Y" programable'). Matrices lógicas programables (PLA) Una PLA está constituida por una matriz de n’ (n’ < 2n, donde n el número de entradas) puertas AND y una matriz de puertas OR, ambas programables. Las puertas AND poseen 2n entradas que se unen a cada variable de entrada a través de conexiones que pueden ser eliminadas. Las puertas OR poseen tantas entradas como puertas AND existen en el circuito (n’), y se conectan a las salidas de estas mediante conexiones igualmente suprimibles. El símbolo lógico de una PLA con tres entradas, seis términos producto y dos salidas es el que sigue: PLA (6) I0 I1 I2 O0 O1 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-11 La estructura interna general de una PLA se representa en la figura. I0 I1 .. .. . In-1 ........ P0 P1 Pn’-1 O0 O1 .. .. . Om1 Un ejemplo de dispositivo PLA es el que se muestra a continuación. Se trata del PLS 161. Consta de 12 entradas, 48 términos producto y 8 salidas (12 x 48 x 8). Obsérvese cómo es posible invertir las salidas, e incluso colocarlas en estado de alta impedancia. Después del esquema lógico, se representa su tabla de programación. Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-12 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-13 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-14 Ejemplo de diseño con una PLA: Implementar mediante una PLA el sistema combinacional formado por las siguientes funciones: f1 = 3 (0,2,3,5,6,7) f2 = 3 (0,2,3,7) La PLA mínima necesaria para la implementación de esta multifunción, deberá tener tres entradas (número de entradas del sistema), seis términos producto (número de términos producto distintos del sistema) y dos salidas (número de salidas del sistema). Una vez programada, su estructura interna quedaría como sigue: a b c P0 P2 P3 P5 P6 P7 f1 f2 A veces, la simplificación de las expresiones en forma de sumatorio de las funciones a implementar, permite la reducción del tamaño de la PLA necesaria para la implementación del sistema. Así, si simplificamos por Karnaugh las funciones anteriores obtendremos: f1 = c a + b + c a f2= c a + b a Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-15 El tamaño mínimo de la PLA necesaria para la implementación del sistema, utilizando las expresiones simplificadas, será ahora 3 x 4 x 2 (3 entradas, 4 términos producto distintos entre las dos expresiones y 2 salidas). El circuito, una vez programado, quedará como se muestra en la figura. a b c c’a’ ca b ba f1 f2 Y la tabla de programación correspondiente será: AND 1 2 3 4 VAR I2 L H c I1 H H b I0 L H H a O1 A • • A f2 O0 A A A • f1 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-16 Matrices lógicas Y - programables (PAL) Una PAL es un sistema combinacional programable universal incompleto, de estructura similar a la de una PLA, de la cual se diferencia en que cada una de las puertas OR están conectadas rígidamente a un conjunto de puertas AND cada una. En general, si el número de términos producto es n’ y el de salidas m, cada una de estas últimas irá conectada a n’/m puertas AND. Las PAL son dispositivos menos flexibles que las PLA y necesitan más puertas AND que éstas, ya que si un producto forma parte de varias funciones, deberá ser programado para cada una de ellas. En compensación, su tiempo de programación es más pequeño, disipan menos potencia, ocupan memos superficie de silicio y su programación es más sencilla. La estructura interna general de una PAL, con 6 términos producto y dos salidas, se representa en la siguiente figura. I0 I1 .. .. . In-1 f1 f2 El símbolo lógico de una PAL con tres entradas, ocho términos producto y dos salidas es el que sigue: PAL I0 I1 I2 (6) O0 O1 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-17 En la siguiente figura se representa la estructura interna de una PAL programada para implementar el sistema del ejemplo anterior. f1 = c a + b + c a f2= c a + b a a b c f1 f2 Estructura interna de la PAL programada para generar f1 y f2 simplificadas. La tabla de programación de la PAL será en este caso: AND 1 2 3 4 5 6 VAR I2 L H L - I1 H H I0 L H L H c b a O1 A A • f2 O0 A A A f1 Como hemos podido apreciar en el ejemplo anterior, para implementar un sistema combinacional mediante una PAL, ésta deberá tener al menos tantas entradas y salidas como dicho sistema, y tantas puertas AND como el resultado de multiplicar el número de funciones de salida por el número de términos producto de la función que más términos posea. Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-18 Ejemplo de dispositivo PAL real. Como ejemplo de arquitectura PAL se muestra en la figura 6 la estructura interna de la PAL18P8. En este dispositivo sólo puede programarse la matriz AND, ya que la matriz OR tiene conexiones fijas. Este dispositivo puede configurarse para cambiar el número de entradas y de salidas. Como ejercicio, defina en qué forma una salida puede convertirse en una entrada en este dispositivo. Fundamentos de Computadores. Sistemas Combinacionales Programables. La tabla de programación de la PAL18P8 se muestra a continuación. T9-19 Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-20 PROCEDIMIENTO DE DISEÑO CON DISPOSITIVOS LÓGICOS PROGRAMABLES El procedimiento de diseño basado en estos dispositivos pasa por los siguientes puntos: 1. Especificación de la función que el circuito debe realizar. Esta especificación puede consistir en ecuaciones booleanas, tablas de verdad, diagramas de estados, diagramas lógicos, VHDL y otros formatos. 2. Generación de ecuaciones. A partir de las especificaciones iniciales, se generan las ecuaciones que las representan. 3. Simplificación de las ecuaciones lógicas. Este paso es necesario para asegurar que la lógica a implementar puede realizarse en un dispositivo concreto, ya que éstos tienen un número limitado de recursos. 4. Generación del mapa de fusibles. Consiste en proporcionar una matriz que indique qué fusibles han de eliminarse y cuales deben dejarse intactos para generar la lógica en el dispositivo elegido. 5. Simulación lógica. Este paso es opcional, aunque muy importante en el diseño de circuitos secuenciales. Consiste en determinar el funcionamiento exacto que tendrá el dispositivo una vez grabado, pero sin necesidad de programarlo. La simulación se realiza en el ordenador. 6. Programación del dispositivo seleccionado. Una vez comprobado el diseño, puede ya grabarse el dispositivo físicamente, labor que realiza el programador de dispositivos. Este instrumento recibe el mapa de fusibles y de él extrae la información necesaria para grabar el dispositivo aplicando ciertos impulsos eléctricos. 7. Chequeo o test del dispositivo ya programado. Este paso consiste en comprobar que un dispositivo ha sido grabado correctamente. Esta comprobación se realiza con la ayuda del mismo programador de dispositivos. Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-21 Sistemas combinacionales programables universales completos Estos sistemas proporcionan todos los términos posibles que podemos obtener con las variables de entrada. Su estructura es de tipo "AND Fija - OR Programable". Sólo la matriz OR es programable. Esta es una estructura PROM (Programmable Read Only Memory: 'Memoria programable de sólo lectura'). La figura muestra un ejemplo de esta estructura. Como ejemplo de representación gráfica de la programación interna de estas estructuras, se presenta en la figura 3 la realización de la función lógica de tres variables: F = A BC + AC , Fundamentos de Computadores. Sistemas Combinacionales Programables. T9-22 Esta memoria de sólo lectura tiene un tamaño de 8 x 1, es decir, genera 8 términos producto canónicos, que necesitan 3 entradas cada uno (23=8) y una salida. Estos elementos son los considerados en general memorias, y están organizados como una matriz de posiciones que guardan bits. En efecto, si en el ejemplo anterior tomamos las 3 entradas como entradas de direccionamiento, podemos considerar que la PROM es una matriz de 8 x 1, donde en cada una de sus posiciones de almacenamiento (desde la 0 hasta la 7, que seleccionamos con las tres entradas) se guarda un bit. Si, por ejemplo, tuviéramos una memora PROM de 16 x 8, esto significaría que disponemos de 16 posiciones de memoria, cada una de las cuales guarda 8 bits ( a los que accederíamos en paralelo en la salida).