VARIABLES Y SEÑALES

Anuncio

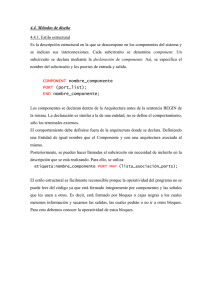

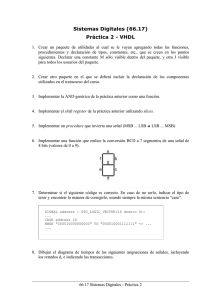

FUNCIONES Y PROCEDIMIENTOS 1 VARIABLES Y SEÑALES • Constantes • Variables • Señales • Señales de Resolución. Funciones de resolución FUNCIONES Y PROCEDIMIENTOS 2 Constantes • Objeto que almacena un único valor durante toda la simulación. • Se deben inicializar al ser declaradas. • Declaración en arquitecturas (visible en toda la arquitectura), antes de begin. FUNCIONES Y PROCEDIMIENTOS 3 Variables/señales • Variables y señales: almacenan información que puede cambiar durante la simulación. Transportan datos entre elementos. • Variables y señales: Tratamiento distinto en la simulación y en la síntesis. • Señales: Ligadas al carácter hardware del lenguaje. Son las conexiones o terminales físicos del circuito. FUNCIONES Y PROCEDIMIENTOS 4 Variables • Declaradas y usadas en sistemas secuenciales: funciones, procedimientos y procesos. • Dentro de un proceso: - En su parte de declaración. - Visibles sólo dentro del proceso. FUNCIONES Y PROCEDIMIENTOS 5 Variables: Declaración • Una vez declarada su valor puede cambiar durante la simulación: - La asignación a variables es inmediata: FUNCIONES Y PROCEDIMIENTOS 6 Variables: Asignación Cuando hay cambios en “a” el proceso se dispara y “count_a” se incrementa. FUNCIONES Y PROCEDIMIENTOS 7 Señales • Usadas para representar: • Puertos de entrada/salida de la entidad. • Señales internas en el cuerpo de una arquitectura. • Visibles en: • Puertos entrada/salida de una entidad: Visibles en todos los cuerpos de arquitecturas de esa entidad. • Señales internas: Accesibles en todo el cuerpo de la arquitectura. 8 FUNCIONES Y PROCEDIMIENTOS Señales: Declaración 9 FUNCIONES Y PROCEDIMIENTOS Variables vs señales • Sintaxis: • Variables: tienen un campo de acción limitado (proceso). • Señales: tienen un campo de acción más extenso (módulo). • Simulación: • Variables: asignación con efecto inmediato. • Señales: la asignación se produce en el siguiente ciclo de simulación (al final de la ejecución del proceso). • Síntesis: • Variables: a veces se sintetizan como cableados. • Señales: En sentencias con reloj pueden dar lugar a elementos de memorias. 10 FUNCIONES Y PROCEDIMIENTOS Variables vs señales FUNCIONES Y PROCEDIMIENTOS 11 Señales: Comportamiento • Las señales se utilizan para comunicación entre procesos. • Cuando se realiza una asignación a una señal se crea un driver para la misma. • No puede haber dos procesos escribiendo en la misma señal. • Excepción son las señales “resolved” . FUNCIONES Y PROCEDIMIENTOS 12 Señales: Comportamiento • La asignación a señales no se produce de forma inmediata. • La asignación es efectiva cuando se termina el “wait”. FUNCIONES Y PROCEDIMIENTOS 13 Señales: Comportamiento P1: process is begin … … x <= ‘1’ after 5 ns; wait for 7 ns; x <= ‘0’ after 5 ns; wait for 7 ns; x <= ‘1’ after 5 ns; wait for 7 ns; … end process; 0 5 ‘1’ 5 10 15 20 ‘0’ ‘1’ 12 19 25 FUNCIONES Y PROCEDIMIENTOS 14 Señales resueltas • Hasta ahora se ha asumido una asignación por señal sólo un proceso puede aplicar asignaciones a dicha señal. • Funciones de resolución: deciden qué valor ha de tomar la señal cuando se le aplican dos o más asignaciones. FUNCIONES Y PROCEDIMIENTOS 15 Señales resueltas architecture b of e is signal x: rbit; begin p1: process is begin … x <= ‘1’; … end process; p2: process is begin … x <= ‘0’; … end process; p3: process is begin … if x = ‘1’ then … end process end architecture; • Puesto que p1 y p2 asignan valores a x, x tiene que ser una señal de resolución. FUNCIONES Y PROCEDIMIENTOS 16 Funciones de resolución A net1 B signal net 1: resolv_and bit; and_1: port map(A,B,net1); inv_1: port map (C,net1); C Función de resolución: resuelve el valor que ha de tomar el nodo net1. FUNCIONES Y PROCEDIMIENTOS 17 Funciones de resolución function resolv_and (A:bit_vector) return bit is begin for I in A´range loop if A(I) = ´0´then return ´0´; end if; end for return ´1´; end resolv_and; Es una conexión AND FUNCIONES Y PROCEDIMIENTOS 18 Funciones de resolución type std_ulogic is ( ‘U’, -- unintialized ‘X’, -- forcing unknown ‘0’, -- forcing 0 ‘1’, -- forcing 1 ‘Z’, -- high impedance ‘W’, -- weak unknown ‘L’, -- weak 0 ‘H’, -- weak 1 ‘-’ -- don’t care); IEEE.std_logic_1164