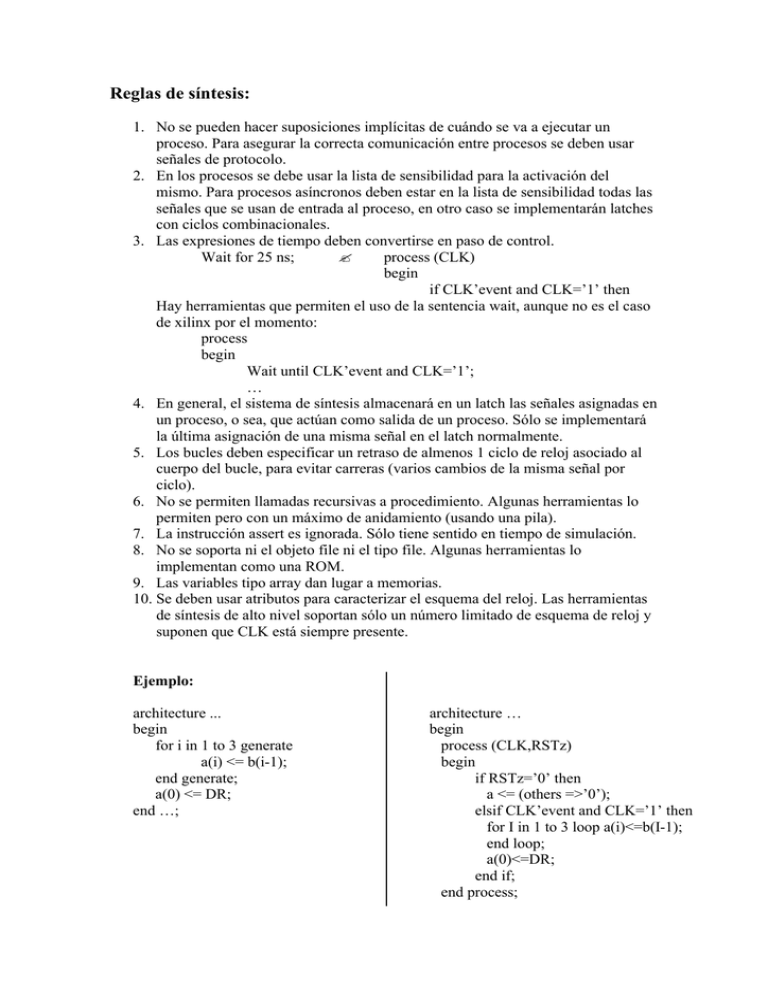

Reglas de síntesis:

Anuncio

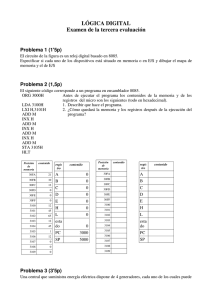

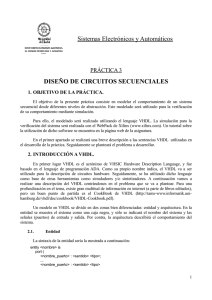

Reglas de síntesis: 1. No se pueden hacer suposiciones implícitas de cuándo se va a ejecutar un proceso. Para asegurar la correcta comunicación entre procesos se deben usar señales de protocolo. 2. En los procesos se debe usar la lista de sensibilidad para la activación del mismo. Para procesos asíncronos deben estar en la lista de sensibilidad todas las señales que se usan de entrada al proceso, en otro caso se implementarán latches con ciclos combinacionales. 3. Las expresiones de tiempo deben convertirse en paso de control. Wait for 25 ns; ? process (CLK) begin if CLK’event and CLK=’1’ then Hay herramientas que permiten el uso de la sentencia wait, aunque no es el caso de xilinx por el momento: process begin Wait until CLK’event and CLK=’1’; … 4. En general, el sistema de síntesis almacenará en un latch las señales asignadas en un proceso, o sea, que actúan como salida de un proceso. Sólo se implementará la última asignación de una misma señal en el latch normalmente. 5. Los bucles deben especificar un retraso de almenos 1 ciclo de reloj asociado al cuerpo del bucle, para evitar carreras (varios cambios de la misma señal por ciclo). 6. No se permiten llamadas recursivas a procedimiento. Algunas herramientas lo permiten pero con un máximo de anidamiento (usando una pila). 7. La instrucción assert es ignorada. Sólo tiene sentido en tiempo de simulación. 8. No se soporta ni el objeto file ni el tipo file. Algunas herramientas lo implementan como una ROM. 9. Las variables tipo array dan lugar a memorias. 10. Se deben usar atributos para caracterizar el esquema del reloj. Las herramientas de síntesis de alto nivel soportan sólo un número limitado de esquema de reloj y suponen que CLK está siempre presente. Ejemplo: architecture ... begin for i in 1 to 3 generate a(i) <= b(i-1); end generate; a(0) <= DR; end …; architecture … begin process (CLK,RSTz) begin if RSTz=’0’ then a <= (others =>’0’); elsif CLK’event and CLK=’1’ then for I in 1 to 3 loop a(i)<=b(I-1); end loop; a(0)<=DR; end if; end process;

![Duración 2:00 h 1.- [3 puntos] Inicialmente el registro A del circuito](http://s2.studylib.es/store/data/006054581_1-5bf5edf798f4d3df94d79777115bdac4-300x300.png)