Descripciones funcionales y estructurales Circuitos Electrónicos

Anuncio

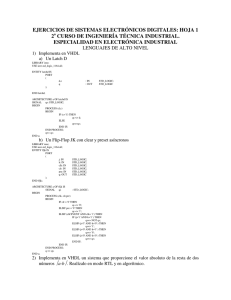

Circuitos Electrónicos Digitales E.T.S.I. Telecomunicación Universidad Politécnica de Madrid Descripciones funcionales y estructurales Descripciones funcionales y estructurales. Introducción al lenguaje VHDL. Descripciones en VHDL. Componentes sobre los que realizar la síntesis: CPLD y FPGA. Ejemplos adicionales y ejercicios CEDG - Tema 7 1 Niveles de abstracción • Permiten abordar el diseño de sistemas modernos que se caracterizan por: – Elevada y muy elevada complejidad (millones de puertas lógicas) – Diseñados por equipos de diseño en vez de diseñadores individuales • Se basan en simplificar el problema para manejar la complejidad Nivel funcional Nivel RTL Nivel lógico – Bajo nivel: mucho detalle – Alto nivel: poco detalle Nivel eléctrico • Imprescindible la elaboración de una metodología de diseño CEDG - Tema 7 2 Síntesis de circuitos • Se parte de una descripción funcional en un lenguaje de descripción de alto nivel (en nuestro caso VHDL) y se sigue un proceso de diseño hasta llegar a integrarlo en uno o varios circuitos integrados (FPGA o PLD) CEDG - Tema 7 3 Descripciones funcionales y estructurales Descripción Estructural Descripción Funcional library IEEE; use IEEE.std_logic_1164.all; entity BasculaRS is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; S Q R QN Báscula RS library IEEE; use IEEE.std_logic_1164.all; architecture BasculaRS _arch of BasculaRS is component nor2 port (I0, I1: in STD_LOGIC; O: out STD_LOGIC); end component; begin U1: nor2 port map (R,QN,Q); U2: nor2 port map (S,Q,QN); entity BasculaRS is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; architecture BasculaRS_arch of BasculaRS is begin QN <= S nor Q; Q <= R nor QN; end BasculaRS _arch; end BasculaRS_arch; CEDG - Tema 7 4 Estructura general en VHDL library IEEE; use IEEE.std_logic_1164.all; Báscula RS Librería IEEE.std_logic_1164.all Puertos: S, R, Q y QN Comportamiento o estructura de la caja: QN <= S nor Q; Q <= R nor QN; entity BasculaRS is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; architecture BasculaRS_arch of BasculaRS is begin QN <= S nor Q; Q <= R nor QN; end BasculaRS_arch; CEDG - Tema 7 5 Librerías (VHDL) Librería de uso, normalmente: IEEE.std_logic_1164.all estándar IEEE.std_logic_arith.all aritmética IEEE.std_logic_unsigned.all aritmética sin signo Y muchas más según las necesidades, definibles también por el usuario library IEEE; use IEEE.std_logic_1164.all; entity BasculaRS is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; architecture BasculaRS_arch of BasculaRS is begin QN <= S nor Q; Q <= R nor QN; end BasculaRS_arch; CEDG - Tema 7 6 Empaquetado I (VHDL) BasculaRS Nombre: BasculaRS Nombre de los puertos: S y R Tipo: in Señales: Lógicas estándar Nombre de los puertos: Q y QN Tipo: buffer Señales: Lógicas estándar library IEEE; use IEEE.std_logic_1164.all; entity BasculaRS is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; architecture BasculaRS_arch of BasculaRS is begin QN <= S nor Q; Q <= R nor QN; end BasculaRS_arch; CEDG - Tema 7 7 Empaquetado II (VHDL) • Nombre del componente, “case sensitive”: entity BasculaRS is port ( ); end BasculaRS; BasculaRS • Nombre de los puertos: port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); • Tipo de los puertos: – – – – in: Entrada de un componente out: Salida de un componente. No puede ser leída desde su interior. buffer: Salida de un componente. Puede ser leída desde su interior. inout: Puede actuar como entrada o salida, típicamente triestado. • Puertos simples y complejos: – De un solo bit: STD_LOGIC – Arrays de bits: STD_LOGIC_VECTOR (inferior to superior) STD_LOGIC_VECTOR (superior downto inferior) • Niveles de señal de los puertos: SDT_LOGIC – “0”, “1”,”Z”, “X” y algunos más para diseño avanzado CEDG - Tema 7 8 Comportamiento I (VHDL) library IEEE; use IEEE.std_logic_1164.all; Nombre de la realización: BasculaRS_arch Nombre del componente: BasculaRS Asignaciones: <= Funciones: nor Variables o señales: S, R, Q, QN entity BasculaRS is port (S,R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; architecture BasculaRS_arch of BasculaRS is begin QN <= S nor Q; Q <= R nor QN; end BasculaRS_arch; CEDG - Tema 7 9 Comportamiento II (VHDL) • Nombre de la arquitectura, puede haber varias realizaciones para una misma entidad: architecture BasculaRS_arch_NOR of BasculaRS is begin Cuerpo; end BasculaRS_arch_NOR • Nombre del componente al que corresponde esta realización (BasculaRS): • Asignaciones (concurrentes): variable_asignada <= variable o función que se asigna Q <= R nor QN; Salida <= ‘0’; variable_asignada <= ‘valor’ when condición else ‘valor’ Z <= ‘1’ when X=‘1’ and Y=‘0’ else ‘0’; CEDG - Tema 7 10 Comportamiento III (VHDL) – Funciones simples: Booleanas: and, or, nand, nor, xor, xnor, not Enteras: +, -, *, /, y otras más – Funciones complejas • If-then-else if condición then acción_1; elsif acción_2; ... else acción_n; end if; • select with expresión select señal <= valor_1 when condición_1, ….. valor_n when condición_n; • Procesos: Permiten definir acciones secuenciales en el Cuerpo process (señal_1, señal_2, … , señal_n) begin cuerpo end process; CEDG - Tema 7 11 Circuitos combinacionales • Descripción de algunos ejemplos de circuitos combinacionales – Decodificador 3_a_8 74xx138 – Variación de niveles sobre el 74xx138. Se muestra la flexibilidad de este tipo de descripciones y su elevada productividad – Multiplexor de 4 entradas de 8 bits – Multiplexor especializado 4 entradas de 3 bits. Se diseña un nuevo componente sobre el anterior – Comparador de 8 bits – Comparador de 8 bits (alternativo). Flexibilidad en las implementaciones – Barrel shifter de 16 bits con desplazamiento circular a la izquierda • Al final del tema se presentan como ejercicios para el alumno otros componentes CEDG - Tema 7 12 Decodificador 3_a_8 74xx138 library IEEE; use IEEE.std_logic_1164.all; entity V74x138 is port (G1, G2A_L, G2B_L: in STD_LOGIC; -- enable inputs A: in STD_LOGIC_VECTOR (2 downto 0); -- select inputs Y_L: out STD_LOGIC_VECTOR (0 to 7) ); -- decoded outputs end V74x138; architecture V74x138_a of V74x138 is signal Y_L_i: STD_LOGIC_VECTOR (0 to 7); begin with A select Y_L_i <= "01111111" when "000", "10111111" when "001", "11011111" when "010", "11101111" when "011", "11110111" when "100", "11111011" when "101", "11111101" when "110", "11111110" when "111", "11111111" when others; Y_L <= Y_L_i when (G1 and not G2A_L and not G2B_L)='1' else "11111111“; end V74x138_a; CEDG - Tema 7 13 Variación de niveles sobre el 74xx138 architecture V74x138_b of V74x138 is signal G2A, G2B: STD_LOGIC; -- active-high version of inputs signal Y: STD_LOGIC_VECTOR (0 to 7); -- active-high version of outputs signal Y_s: STD_LOGIC_VECTOR (0 to 7); -- internal signal begin G2A <= not G2A_L; -- convert inputs G2B <= not G2B_L; -- convert inputs Y_L <= Y; -- convert outputs with A select Y_s <= "10000000" when "000", "01000000" when "001", "00100000" when "010", "00010000" when "011", "00001000" when "100", "00000100" when "101", "00000010" when "110", "00000001" when "111", "00000000" when others; Y <= not Y_s when (G1 and G2A and G2B)='1' else "00000000"; end V74x138_b; CEDG - Tema 7 14 Multiplexor de 4 entradas de 8 bits library IEEE; use IEEE.std_logic_1164.all; entity mux4in8b is port ( S: in STD_LOGIC_VECTOR (1 downto 0); -- Select inputs, 0-3 ==> A-D A, B, C, D: in STD_LOGIC_VECTOR (1 to 8); -- Data bus input Y: out STD_LOGIC_VECTOR (1 to 8) -- Data bus output ); end mux4in8b; architecture mux4in8b of mux4in8b is begin with S select Y <= A when "00", B when "01", C when "10", D when "11", (others => 'U') when others; -- this creates an 8-bit vector of 'U' end mux4in8b; CEDG - Tema 7 15 Multiplexor especializado 4 entradas de 3 bits library IEEE; use IEEE.std_logic_1164.all; entity mux4in3b is port ( S: in STD_LOGIC_VECTOR (2 downto 0); -- Select inputs, 0-7 ==> ABACADAB A, B, C, D: in STD_LOGIC_VECTOR (1 to 18); -- Data bus inputs Y: out STD_LOGIC_VECTOR (1 to 18) -- Data bus output ); end mux4in3b; architecture mux4in3p of mux4in3b is begin process(S, A, B, C, D) variable i: INTEGER; begin case S is when "000" | "010" | "100" | "110" => Y <= A; when "001" | "111" => Y <= B; when "011" => Y <= C; when "101" => Y <= D; when others => Y <= (others => 'U'); -- 18-bit vector of 'U' end case; end process; end mux4in3p; CEDG - Tema 7 16 Comparador de 8 bits library IEEE; use IEEE.std_logic_1164.all; entity vcompare is port ( A, B: in STD_LOGIC_VECTOR (7 downto 0); EQ, NE, GT, GE, LT, LE: out STD_LOGIC ); end vcompare; architecture vcompare_arch of vcompare is begin process (A, B) begin EQ <= '0'; NE <= '0'; GT <= '0'; GE <= '0'; LT <= '0'; LE <= '0'; if A = B then EQ <= '1'; end if; if A /= B then NE <= '1'; end if; if A > B then GT <= '1'; end if; if A >= B then GE <= '1'; end if; if A < B then LT <= '1'; end if; if A <= B then LE <= '1'; end if; end process; end vcompare_arch CEDG - Tema 7 17 Comparador de 8 bits (alternativo) library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity comp8 is port ( A, B: in STD_LOGIC_VECTOR (7 downto 0); EQ, GT: out STD_LOGIC ); end comp8; architecture comp8_arch of comp8 is begin EQ <= '1' when A = B else '0'; GT <= '1' when A > B else '0'; end comp8_arch; CEDG - Tema 7 18 Barrel shifter 16 bits desplz. circ. izquierda library IEEE; use IEEE.std_logic_1164.all; entity rol16 is port ( DIN: in STD_LOGIC_VECTOR(15 downto 0); -- Data inputs S: in STD_LOGIC_VECTOR (3 downto 0); -- Shift amount, 0-15 DOUT: out STD_LOGIC_VECTOR(15 downto 0) -- Data bus output ); end rol16; architecture rol16_arch of rol16 is begin process(DIN, S) variable X, Y, Z: STD_LOGIC_VECTOR(15 downto 0); begin if S(0)='1' then X := DIN(14 downto 0) & DIN(15); else X := DIN; end if; if S(1)='1' then Y := X(13 downto 0) & X(15 downto 14); else Y := X; end if; if S(2)='1' then Z := Y(11 downto 0) & Y(15 downto 12); else Z := Y; end if; if S(3)='1' then DOUT <= Z(7 downto 0) & Z(15 downto 8); else DOUT <= Z; end if; end process; end rol16_arch; CEDG - Tema 7 19 Circuitos secuenciales • Descripción de algunos ejemplos de elementos biestables, circuitos secuenciales y máquinas de estados – Báscula R-S – Biestable D con flanco positivo – Biestable D con Preset y Clear 74xx74. Se muestra la elevada flexibilidad y productividad de estas descripciones – Contador binario de cuatro bits 74xx163 – Ejemplo de máquina de estados que muestra un formato genérico propuesto para la descripción de este tipo de máquinas – Máquina estados: intermitente Thunderbird, como ejemplo de implementación • Al final del tema se presentan como ejercicios para el alumno otros componentes CEDG - Tema 7 20 Báscula R-S library IEEE; use IEEE.std_logic_1164.all; entity Vsrlatch is port (S, R: in STD_LOGIC; Q, QN: buffer STD_LOGIC ); end Vsrlatch; architecture Vsrlatch_arch of Vsrlatch is begin QN <= S nor Q; Q <= R nor QN; end Vsrlatch_arch; CEDG - Tema 7 21 Biestable D con flanco positivo library IEEE; use IEEE.std_logic_1164.all; entity Vdff is port (D, CLK: in STD_LOGIC; Q: out STD_LOGIC ); end Vdff; architecture Vdff_b of Vdff is begin process(CLK) begin if (CLK'event and CLK='1') then Q <= D; end if; end process; end Vdff_b; CEDG - Tema 7 22 Biestable D con Preset y Clear 74xx74 library IEEE; use IEEE.std_logic_1164.all; entity Vdff74 is port (D, CLK, PR_L, CLR_L: in STD_LOGIC; Q, QN: out STD_LOGIC ); end Vdff74; architecture Vdff74_b of Vdff74 is signal PR, CLR: STD_LOGIC; begin process(CLR_L, CLR, PR_L, PR, CLK) begin PR <= not PR_L; CLR <= not CLR_L; if (CLR and PR) = '1' then Q <= '0'; QN <= '0'; elsif CLR = '1' then Q <= '0'; QN <= '1'; elsif PR = '1' then Q <= '1'; QN <= '0'; elsif (CLK'event and CLK='1') then Q <= D; QN <= not D; end if; end process; end Vdff74_b; CEDG - Tema 7 23 Contador binario de cuatro bits 74xx163 library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; entity V74x163 is port ( CLK, CLR_L, LD_L, ENP, ENT: in STD_LOGIC; D: in UNSIGNED (3 downto 0); Q: out UNSIGNED (3 downto 0); RCO: out STD_LOGIC ); end V74x163; architecture V74x163_arch of V74x163 is signal IQ: UNSIGNED (3 downto 0); begin process (CLK, ENT, IQ) begin if (CLK'event and CLK='1') then if CLR_L='0' then IQ <= (others => '0'); elsif LD_L='0' then IQ <= D; elsif (ENT and ENP)='1' then IQ <= IQ + 1; end if; end if; if (IQ=15) and (ENT='1') then RCO <= '1'; else RCO <= '0'; end if; Q <= IQ; end process; end V74x163_arch; CEDG - Tema 7 24 Ejemplo de máquina de estados library IEEE; use IEEE.std_logic_1164.all; entity smexamp is port ( CLOCK, A, B: in STD_LOGIC; Z: out STD_LOGIC ); end; architecture smexamp_arch of smexamp is type Sreg_type is (INIT, A0, A1, OK0, OK1); signal Sreg: Sreg_type; begin process (CLOCK) -- state-machine states and transitions begin if CLOCK'event and CLOCK = '1' then case Sreg is when INIT => if A='0' then Sreg <= A0; elsif A='1' then Sreg <= A1; end if; when A0 => if A='0' then Sreg <= OK0; elsif A='1' then Sreg <= A1; end if; when A1 => if A='0' then Sreg <= A0; elsif A='1' then Sreg <= OK1; end if; when OK0 => if A='0' then Sreg <= OK0; elsif A='1' and B='0' then Sreg <= A1; elsif A='1' and B='1' then Sreg <= OK1; end if; when OK1 => if A='0' and B='0' then Sreg <= A0; elsif A='0' and B='1' then Sreg <= OK0; elsif A='1' then Sreg <= OK1; end if; when others => Sreg <= INIT; end case; end if; end process; with Sreg select -- output values based on state Z <= '0' when INIT | A0 | A1, '1' when OK0 | OK1, '0' when others; end smexamp_arch; CEDG - Tema 7 25 Máquina estados: intermitente Thunderbird begin process (CLOCK) begin if CLOCK'event and CLOCK = '1' then if RESET = '1' then LIGHTS <= IDLE; else entity Vtbird is case LIGHTS is port ( CLOCK, RESET, LEFT, RIGHT, HAZ: in STD_LOGIC; when IDLE => if HAZ='1' or (LEFT='1' and RIGHT='1') then LIGHTS <= LR3; LIGHTS: buffer STD_LOGIC_VECTOR (1 to 6) ); elsif LEFT='1' then LIGHTS <= L1; end; elsif RIGHT='1' then LIGHTS <= R1; else LIGHTS <= IDLE; architecture Vtbird_arch of Vtbird is end if; constant IDLE: STD_LOGIC_VECTOR (1 to 6) := "000000"; when L1 => if HAZ='1' then LIGHTS <= LR3; else LIGHTS <= L2; end if; constant L3 : STD_LOGIC_VECTOR (1 to 6) := "111000"; when L2 => if HAZ='1' then LIGHTS <= LR3; else LIGHTS <= L3; end if; constant L2 : STD_LOGIC_VECTOR (1 to 6) := "110000"; when L3 => LIGHTS <= IDLE; constant L1 : STD_LOGIC_VECTOR (1 to 6) := "100000"; when R1 => if HAZ='1' then LIGHTS <= LR3; else LIGHTS <= R2; end if; constant R1 : STD_LOGIC_VECTOR (1 to 6) := "000001"; when R2 => if HAZ='1' then LIGHTS <= LR3; else LIGHTS <= R3; end if; constant R2 : STD_LOGIC_VECTOR (1 to 6) := "000011"; when R3 => LIGHTS <= IDLE; constant R3 : STD_LOGIC_VECTOR (1 to 6) := "000111"; when LR3 => LIGHTS <= IDLE; constant LR3 : STD_LOGIC_VECTOR (1 to 6) := "111111"; when others => null; end case; end if; end if; end process; end Vtbird_arch; CEDG - Tema 7 26 Introducción de la temporización (VHDL) • Permiten asignar retardos a las señales (habitualmente a las salidas respecto a las entradas) mediante la palabra clave after • Ejemplo library IEEE; use IEEE.std_logic_1164.all; entity BasculaRS is port (S,R: in STD_LOGIC; Q, QN: buffer STD_LOGIC); end BasculaRS; architecture BasculaRS_arch of BasculaRS is begin QN <= S nor Q after 4 ns; Q <= R nor QN after 4 ns; end BasculaRS_arch; CEDG - Tema 7 27 Descripciones estructurales (VHDL) library IEEE; use IEEE.std_logic_1164.all; entity Decodificador_2_a_4 is port (I0,I1,EN: in STD_LOGIC; Y0,Y1,Y2,Y3: out STD_LOGIC); end Decodificador_2_a_4; architecture Decodificador_2_a_4_arch of Decodificador_2_a_4 is signal NOTI0, NOTI1: STD_LOGIC; component inv port (I: in STD_LOGIC; O: out STD_LOGIC); end component; component and3 port (I0, I1, I2: in STD_LOGIC; O: out STD_LOGIC); end component; begin process (CLK,CLR) begin U1: inv port map (I0,NOTI0); U2: inv port map (I1,NOTI1); U3: and3 port map (NOTI0,NOTI1,EN,Y0); U4: and3 port map (I0,NOTI1,EN,Y1); U5: and3 port map (NOTI0,I1,EN,Y2); U6: and3 port map (I0,I1,EN,Y3); end Decodificador_2_a_4_arch; CEDG - Tema 7 28 PLD: Dispositivos Lógicos Programables • Se basan en el principio de que cualquier circuito combinacional puede realizarse como una suma de productos • La idea es construir dentro de un circuito integrado un array grande de puertas AND (para realizar los productos) y puertas OR (para realizar las sumas) con interconexiones programables – n entradas. Las puertas AND tienen 2n entradas, (cada variable y su complementada) – m salidas, que corresponden a las salidas de cada una de las puertas OR que realizan las sumas • Cada puerta AND puede conectarse por programación del dispositivo a entradas de las puertas OR • Los sintetizadores permiten pasar descripciones funcionales (i.e. VHDL) a este tipo de dispositivos CEDG - Tema 7 29 PLA 4X3 con 6 productos, p=6 • Las conexiones se realizan fundiendo los fusibles marcados en azul como X CEDG - Tema 7 30 Representación compacta CEDG - Tema 7 31 Ejemplo CEDG - Tema 7 32 PAL • Habitualmente no se utiliza la compartición de productos, lo que no justifica el array OR • En las PAL el array OR es fijo. Cada puerta AND está permanentemente conectada a una puerta OR determinada • Ejemplo: PAL16L8 CEDG - Tema 7 33 Ejemplo de PAL • 10 entradas • 8 salidas, con 7 AND por salida • 64 filas y 32 columnas (16 variables de entrada a AND) • 1 AND para salida triestado • 6 salidas disponibles como entradas – Mas entradas pero menos salidas – Pueden usarse como lógica en dos pasos CEDG - Tema 7 34 L lid i tid PAL secuenciales • Integran biestables a las salidas, lo que permite el diseño de circuitos síncronos • Ejemplo: PAL 16R8 CEDG - Tema 7 35 Detalle de una salida de la PAL 16R8 • 8 términos producto entran a un biestable tipo D – Reloj activado por flanco, común a todos los biestables • La salida Q se realimenta en el array AND para facilitar la realización de máquinas de estados • Salidas triestado con una señal común de “Enable” CEDG - Tema 7 36 GAL 16V8 • Una de las más comunes • Cada salida es programable para que funcione como combinacional o registrada con un biestable • El nivel de cada salida también es programable CEDG - Tema 7 37 Lógica de salida de la GAL 16V8 CEDG - Tema 7 38 Arquitectura general de una FPGA • Dispone de bloques lógicos complejos programables (CLB) • Dispone de una matriz de interconexión de bloques lógicos programable CEDG - Tema 7 39 Bloque configurable de la FPGA XC4000 • Los bloques F, G y H son elementos combinacionales que pueden implementar funciones de 4, 5, 6 y 9 variables • Las salidas pueden ser registradas o no CEDG - Tema 7 40 Diagrama general del conexionado XC4000 • Dispone de una gran variedad de posibilidades de conexionado para maximizar el uso del hardware CEDG - Tema 7 41 Ejemplos adicionales y ejercicios • Se presentan tres ejemplos adicionales: – Codificador de prioridad 8 entradas 74xx148 – Barrel shifter de16 bits y desplazamientos circulares a izquierda y derecha – Máquina de estados de las adivinanzas • Ejercicios: – Obtenga la función lógica y la tabla de comportamiento del codificador de prioridad 74xx148 – Obtenga la función lógica y la tabla de comportamiento del registro de desplazamiento del segundo ejemplo – Obtenga el diagrama de estados de la máquina de estados del tercer ejemplo CEDG - Tema 7 42 Codificador de prioridad 8 entradas 74xx148 library IEEE; use IEEE.std_logic_1164.all; entity V74x148 is port ( EI_L: in STD_LOGIC; I_L: in STD_LOGIC_VECTOR (7 downto 0); A_L: out STD_LOGIC_VECTOR (2 downto 0); EO_L, GS_L: out STD_LOGIC ); end V74x148; architecture V74x148p of V74x148 is signal EI: STD_LOGIC; -- active-high version of input signal I: STD_LOGIC_VECTOR (7 downto 0); -- active-high version of inputs signal EO, GS: STD_LOGIC; -- active-high version of outputs signal A: STD_LOGIC_VECTOR (2 downto 0); -- active-high version of outputs begin process (EI_L, I_L, EI, EO, GS, I, A) variable j: INTEGER range 7 downto 0; begin EI <= not EI_L; -- convert input I <= not I_L; -- convert inputs EO <= '1'; GS <= '0'; A <= "000"; if (EI)='0' then EO <= '0'; else for j in 7 downto 0 loop if I(j)='1' then GS <= '1'; EO <= '0'; A <= CONV_STD_LOGIC_VECTOR(j,3); exit; end if; end loop; end if; EO_L <= not EO; -- convert output GS_L <= not GS; -- convert output A_L <= not A; -- convert outputs end process; end V74x148p; CEDG - Tema 7 43 Barrel shifter 16 bitsarchitecture despz. circ. izq. y dcha. rol16r_arch of rolr16 is library IEEE; use IEEE.std_logic_1164.all; entity rolr16 is port ( DIN: in STD_LOGIC_VECTOR(15 downto 0); -Data inputs S: in STD_LOGIC_VECTOR (3 downto 0); -- Shift amount, 0-15 DIR: in STD_LOGIC; -- Shift direction, 0=>L, 1=>R DOUT: out STD_LOGIC_VECTOR(15 downto 0) -Data bus output ); end rolr16; begin process(DIN, S, DIR) variable X, Y, Z: STD_LOGIC_VECTOR(15 downto 0); variable CTRL0, CTRL1, CTRL2, CTRL3: STD_LOGIC_VECTOR(1 downto 0); begin CTRL0 := S(0) & DIR; CTRL1 := S(1) & DIR; CTRL2 := S(2) & DIR; CTRL3 := S(3) & DIR; case CTRL0 is when "00" | "01" => X := DIN; when "10" => X := DIN(14 downto 0) & DIN(15); when "11" => X := DIN(0) & DIN(15 downto 1); when others => null; end case; case CTRL1 is when "00" | "01" => Y := X; when "10" => Y := X(13 downto 0) & X(15 downto 14); when "11" => Y := X(1 downto 0) & X(15 downto 2); when others => null; end case; case CTRL2 is when "00" | "01" => Z := Y; when "10" => Z := Y(11 downto 0) & Y(15 downto 12); when "11" => Z := Y(3 downto 0) & Y(15 downto 4); when others => null; end case; case CTRL3 is when "00" | "01" => DOUT <= Z; when "10" | "11" => DOUT <= Z(7 downto 0) & Z(15 downto 8); when others => null; end case; end process; end rol16r_arch; CEDG - Tema 7 44 Máquina de estados de las adivinanzas library IEEE; use IEEE.std_logic_1164.all; entity Vggame is port ( CLOCK, RESET, G1, G2, G3, G4: in STD_LOGIC; L1, L2, L3, L4, ERR: out STD_LOGIC ); end; architecture Vggame_arch of Vggame is type Sreg_type is (S1, S2, S3, S4, SOK, SERR); signal Sreg: Sreg_type; begin process (CLOCK) begin if CLOCK'event and CLOCK = '1' then if RESET = '1' then Sreg <= SOK; else case Sreg is when S1 => if G2='1' or G3='1' or G4='1' then Sreg <= SERR; elsif G1='1' then Sreg <= SOK; else Sreg <= S2; end if; when S2 => if G1='1' or G3='1' or G4='1' then Sreg <= SERR, elsif G1='1' then Sreg <= SOK; else Sreg <= S3; end if; when S3 => if G1='1' or G2='1' or G4='1' then Sreg <= SERR; elsif G1='1' then Sreg <= SOK; else Sreg <= S4; end if; when S4 => if G1='1' or G2='1' or G3='1' then Sreg <= SERR; elsif G1='1' then Sreg <= SOK; else Sreg <= S1; end if; when SOK | SERR => if G1='0' and G2='0' and G3='0' and G4='0' then Sreg <= S1; end if; when others => Sreg <= S1; end case; end if; end if; end process; L1 <= '1' when Sreg = S1 else '0'; L2 <= '1' when Sreg = S2 else '0'; L3 <= '1' when Sreg = S3 else '0'; L4 <= '1' when Sreg = S4 else '0'; ERR <= '1' when Sreg = SERR else '0'; end Vggame_arch; CEDG - Tema 7 45