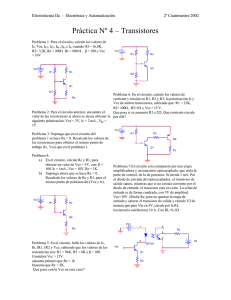

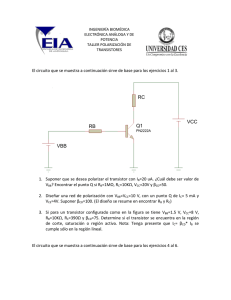

circuitos con dispositivos de dos terminales

Anuncio