INTERFACE CON MEMORIA y E/S

Anuncio

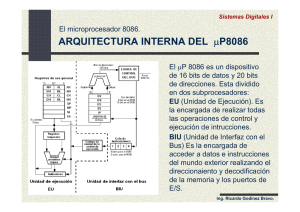

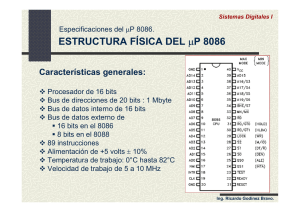

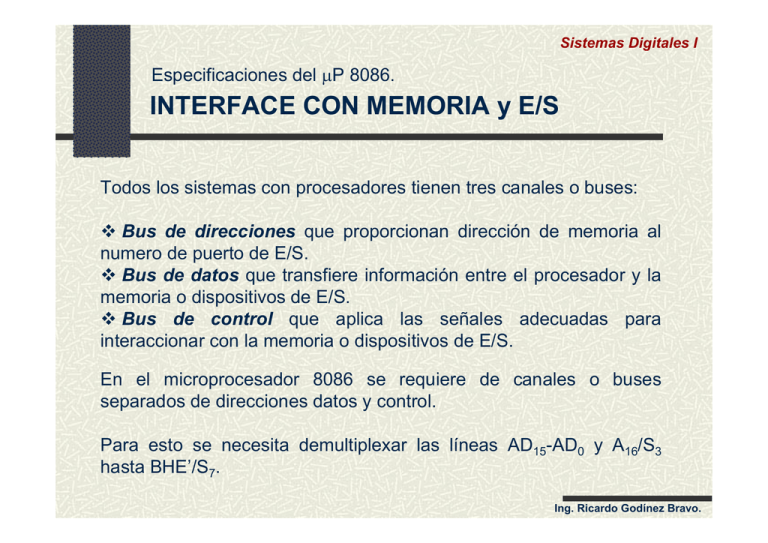

Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Todos los sistemas con procesadores tienen tres canales o buses: Bus de direcciones que proporcionan dirección de memoria al numero de puerto de E/S. Bus de datos que transfiere información entre el procesador y la memoria o dispositivos de E/S. Bus de control que aplica las señales adecuadas para interaccionar con la memoria o dispositivos de E/S. En el microprocesador 8086 se requiere de canales o buses separados de direcciones datos y control. Para esto se necesita demultiplexar las líneas AD15-AD0 y A16/S3 hasta BHE’/S7. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S C.I. 74LS373 (Latch 3er estado) Para esta función se requieren C.I. 74LS373 (Latch con tercer estado o alta impedancia) para acoplar y demultiplexar el bus de direcciones. Este circuito contiene un arreglo de 8 flip-flop que transfieren los datos de entrada al FF cuando la terminal LE = 1. La información sólo es vista en el bus cuando OE’ = 0. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S C.I. 74LS373 (Latch 3er estado) Diagrama lógico. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Diagrama de multiplexado del bus de direcciones en el µP 8086. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S C.I. 74LS245 (Transceiver) Es un transmisor / receptor octal diseñado para comunicaciones asíncronas de dos vías entre buses de datos. La entrada de dirección (DR) controla la transmisión del bus A al bus B ó del bus B al bus A, dependiendo de su valor lógico. La entrada de habilitación (E’) sirve para aislar los buses. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S C.I. 74LS245 (Transceiver) Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S C.I. 74LS244 (Buffer 3er estado) Este dispositivo esta diseñado para proveer el acondicionamiento necesario entre buses en sistemas con procesadores. Se emplea con dispositivos de memoria, transmisores – receptores de bus, etc. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S C.I. 74LS244 (Buffer 3er estado) Diagrama lógico. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Diagrama de multiplexado de los buses de direcciones, datos y control en el µP 8086. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Ciclo de lectura y escritura a memoria El procesador se comunica con el exterior a través de 20 bits multiplexados en tiempo para direcciones, datos y control. Para poder transferir información el procesador ejecuta un ciclo de bus, el cual consiste en cuatro ciclos o periodos de reloj llamados ESTADOS Ti. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Ciclo de lectura y escritura a memoria ESTADO T1. Durante este ciclo se colocan las líneas de direcciones y se activan las señales de control ALE, DT/R’ y M/IO’. ESTADO T2. Durante este ciclo el procesador proporciona las señales de control DEN’ y RD’ o WR’. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Ciclo de lectura y escritura a memoria ESTADO T3. Este periodo de reloj se produce para dar tiempo a la memoria para acceder los datos. ESTADO T4. En este ciclo de reloj se desactivan todas las señales del bus para el siguiente ciclo de bus. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. INTERFACE CON MEMORIA y E/S Ciclo de lectura y escritura a memoria Ing. Ricardo Godínez Bravo.