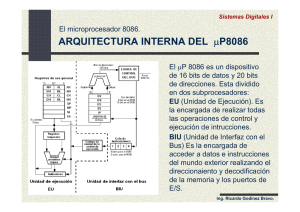

Sistemas Digitales I

Anuncio

Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Características generales: Procesador de 16 bits Bus de direcciones de 20 bits : 1 Mbyte Bus de datos interno de 16 bits Bus de datos externo de 16 bits en el 8086 8 bits en el 8088 89 instrucciones Alimentación de +5 volts ± 10% Temperatura de trabajo: 0°C hasta 82°C Velocidad de trabajo de 5 a 10 MHz Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 AD0-AD7 y AD8-AD15 (pines 2-16 y 39). Parte baja y alta de direcciones y datos. Estas terminales son bidireccionales. A16/S3 – A19/S6 (pines 35-38). Lineas altas de direcciones y bus de estado del procesador. Estas terminales son sólo de salida. Cuando se direcciona el bus de estado, la terminal S6 siempre es cero y la terminal S5 indica el estado de la bandera IF. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 A16/S3 – A19/S6 (pines 35-38). Las terminales S4 y S3 muestran el segmento que se esta accesando durante la solicitud de canal: S4 S3 Segmento 0 0 Extra 0 1 Pila 1 0 Código 1 1 Datos Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 RD’ (pin 32). Línea de lectura de datos de la memoria o de los dispositivos de E/S. Esta terminal es sólo de salida. BHE’/S7. (Bus High Enable, pin 34). Se utilíza para habilitar las líneas más significtivas del bus de datos (D8-D15). El estado de S7 siempre es en nivel alto. Esta terminal es sólo de salida. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 MN/MX’ (pin 33). Terminal de selecciónde modo mínimo ó modo máximo. Es una terminal de entrada. En modo mímino (MN=1) el procesdor genera las señales de control del bus. En modo máximo (MX’=0) las señales de control del bus son generadas externamente por dispositivos controladores de bus. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 TEST’ (pin 23). Es la terminal de entrada para probar la instrucción WAIT. Si TEST’=0, la instrucción WAIT funciona como una instrucción NOP. Si TEST’=1, la instrucción WAIT espra hasta que la terminal TEST’ sea igual a cero. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 READY (pin 22). Es una terminal de entrada que se emplea para control de espera en la temporización del µP. Si READY=0 el procesador introduce estados de espera en los ciclos de lectura y escritura. Si READY=1 entonces no se tiene ningun efecto en el funcionamiento del procesador, es decir, los ciclos de lectura y escritura son normales. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 RESET (pin 21). Esta terminal reinicia al procesador cuando se mantiene por lo menos 4 ciclos de reloj en un nivel alto. Registros del CPU Estado en RESET Banderas (PSW) Limpias a CERO IP 0000H CS FFFFH DS 0000H ES 0000H SS 0000H Cola de Instrucciones Vacia Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 INTR (pin 18). Es la terminal de entrada para la solicitud de interrupciones mascarables por hardware. NMI (pin 17). Es la terminal de entrada para la solicitud de interrupciones NO mascarables por hardware. VCC (pin 40). Terminal de alimentación al procesador. Su valor debe ser de Vcc=5 volts ± 10%. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 GND (pines 1 y 20). Es la terminal de referencia de voltaje. Su valor debe ser GND=0 volts. CLK (pin 19). Es la terminal de entrada para generar los tiempos de trabajo en el procesador (ciclos de máquina). Esta señal debe tener por lo menos un ciclo de trabajo del 33%. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 1) HOLD (pin 31). Terminal de entrada de retención. En esta terminal se solicita acceso directo a memoria (DMA) por un dispositivo. Si HOLD=1 el procesador deja de ejecutar el programa y lleva a los buses de direcciones y datos a un estado de alta impedancia para que se realice el DMA. Si HOLD=0 el procesador sigue ejecutando normalmente el programa. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 1) HLDA (pin 30). Terminal de salida de reconocimiento. Indica que el procesador ha cedido los buses de direcciones, datos y control para acceso directo a memoria (DMA). WR’ (pin 29). Línea de escritura de datos a memoria o dispositivos de E/S. Es una terminal de salida. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 1) M/IO’ (pin 28). Terminal de salida para indicar que se esta accesando a memoria o a dispositivos de E/S. DT/R’ (pin 27). Esta terminal de salida indica la dirección del bus de datos (entrada o salida) para habilitar dispositivos externos como BUFFER, LATCH ó TRANSEIVER. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 1) DEN’ (pin 26). Terminal de salida para habilitar el bus de datos para dispositivos externos. ALE (pin 25). Esta terminal de salida habilita y multiplexa el bus de datos con las líneas de dirección. INTA’ (pin 24). Es la señal de reconocimiento de interrupciones mascarables. Responde a la entrada INTR. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 0) LOCK’ (pin 29). Es una terminal de salida para bloquear periféricos del sistema. Para activar esta terminal se emplea el prefijo LOCK en cualquier instrucción del programa. (RQ/GT0,1)’ (pines 30 y 31). Estas terminales sirven para solicitar y otorgar una operación de DMA. Estas terminales son bidireccionales. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 0) QS0,1 (pines 24 y 25). Estas terminales muestran el estado de la cola de instrucciones. Se usan para proporcionar información a un coprocesador. QS1 QS0 Función 0 0 No hay Operación 0 1 1er Byte de C.O. 1 0 La cola esta vacia 1 1 2° Byte de C.O. Ing. Ricardo Godínez Bravo. Sistemas Digitales I Especificaciones del µP 8086. ESTRUCTURA FÍSICA DEL µP 8086 Terminales del µP8086 (MN/MX’ = 0) (S0,1,2)’ (pines 26-28). Bits de estado. Indican la función del ciclo de bus actual. Se suelen decodificar con el controlador de bus CI8288. S2 S1 S0 Función 0 0 0 Reconocer interrupción 0 0 1 Leer E/S 0 1 0 Escribir E/S 0 1 1 Detener 1 0 0 Acceder a Código 1 0 1 Leer memoria 1 1 0 Escribir a Memoria 1 1 1 Pasiva Ing. Ricardo Godínez Bravo.