1 Características Las principales características que debe satisfacer

Anuncio

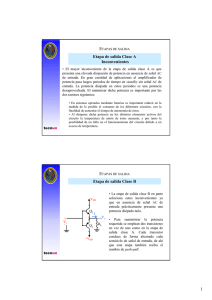

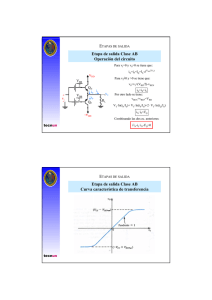

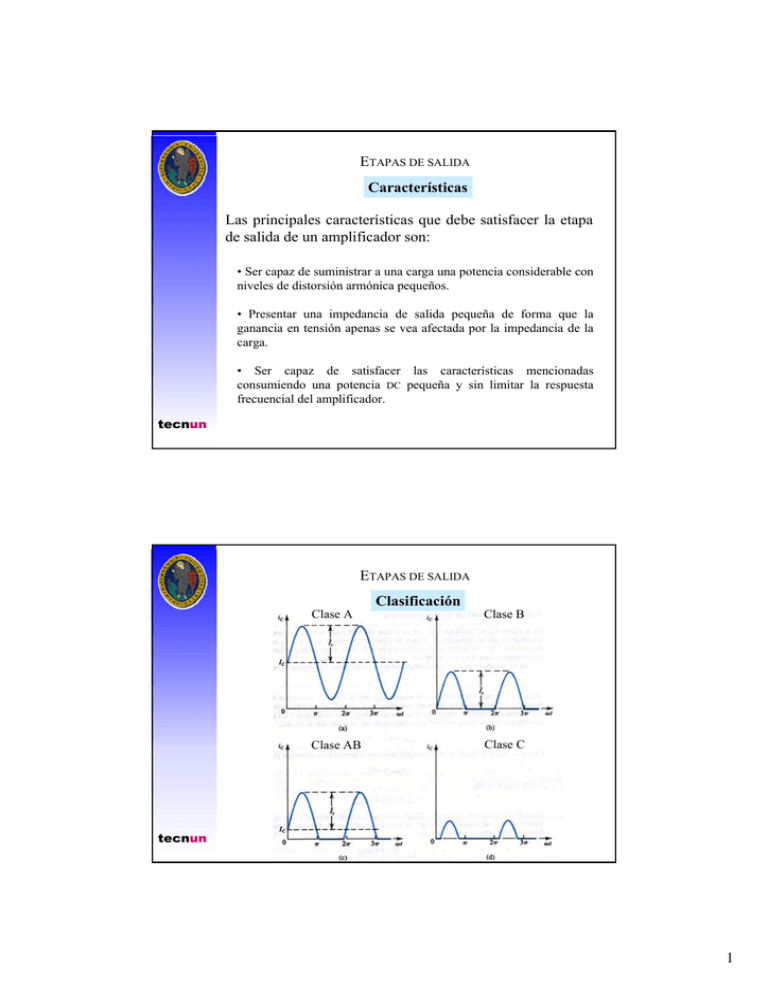

ETAPAS DE SALIDA Características Las principales características que debe satisfacer la etapa de salida de un amplificador son: • Ser capaz de suministrar a una carga una potencia considerable con niveles de distorsión armónica pequeños. • Presentar una impedancia de salida pequeña de forma que la ganancia en tensión apenas se vea afectada por la impedancia de la carga. • Ser capaz de satisfacer las características mencionadas consumiendo una potencia DC pequeña y sin limitar la respuesta frecuencial del amplificador. tecnun ETAPAS DE SALIDA Clase A Clase AB Clasificación Clase B Clase C tecnun 1 ETAPAS DE SALIDA El seguidor de emisor como etapa de salida (Clase A) vDD + Vi - Q1 Io R3 Q2 IR Q3 R1 Vo RL Normalmente IR será menor que IQ por lo que la resistencia R2 será menor que R1, como se vio en el capítulo anterior. IQ R2 -vDD tecnun ETAPAS DE SALIDA Etapa de salida Clase A Curva característica de transferencia vDD + Vi - Q1 Io R3 Q2 IR Q3 R1 tecnun R2 -vDD Vi=Vbe1+V0 En este caso no puede considerarse Vbe1 Cte. ya que se trata de gran señal, por lo que deberá expresarse en función de IC1 e IS. También se supone R0>>RL. Vo I kT Vbe1= q ln C1 IS RL Si Q1 se encuentra en la región activa y βF>>: IQ IC1=IQ+ Entonces: kT Vi= q ln V0 RL IQ+ V0 RL IS + V0 2 ETAPAS DE SALIDA Etapa de salida Clase A Curva característica de transferencia kT Vi= q ln V IQ+ 0 RL IS + V0 IQ> VDD-VCE2sat RL RL> VDD-VCE2sat IQ tecnun ETAPAS DE SALIDA Etapa de salida Clase A Curva característica de transferencia tecnun 3 ETAPAS DE SALIDA Etapa de salida Clase A Formas de onda de la señal Si se asume que VCEsat= 0 por simplicidad, y que la corriente de polarización (IQ) se escoge de forma que: IQ> VDD-VCE2sat RL tecnun ETAPAS DE SALIDA Etapa de salida Clase A Disipación de potencia • En la transparencia anterior se ha observado como la máx. disipación de potencia instantánea en Q1 es igual a VDD· IC1. Esto es igual a la disipación de potencia en reposo de Q1. Entonces el transistor Q1 disipa la máx. cantidad de potencia cuando v0=0. Como esta condición puede fácilmente prevalecer durante tiempos de periodos prolongados, el transistor Q1 debe tener capacidad para resistir una continua disipación de potencia de VDD·IC1. tecnun • La disipación de potencia en Q1 depende del valor de RL. Consideremos el caso extremo de RL=∞. En este caso iC1=IQ, y la máxima disipación de potencia se dará para v0=-VDD, ya que en este caso vCE1 presenta un valor máximo de 2VDD y la pD1=2VDD·IQ. Esta condición normalmente no persistiría durante un intervalo prolongado, por lo cual el diseño no necesita ser así de conservativo. El promedio de disipación de potencia en Q1 es VDD·IQ. 4 ETAPAS DE SALIDA Etapa de salida Clase A Disipación de potencia • Una situación de mucho más riesgo se presentaría en el otro extremo cuando RL=0, es decir un cortocircuito a la salida. En este caso un voltaje positivo de entrada teóricamente resultaría en una corriente infinita de carga. En la práctica circularía una corriente muy elevada por Q1, llegando a producir su destrucción si la situación persiste en el tiempo. Para evitar esta situación, las etapas de salida suelen estar equipadas con protección contra cortocircuitos, como veremos más adelante. tecnun • En cuanto al transistor Q2, éste conduce una corriente Cte. IQ, y el máx. valor de vCE2 es 2·VDD, por lo que la máx. potencia instantánea disipada será pD1=2·VDD·IQ. Al igual que antes esta condición no suele prevalecer durante periodos prolongados de tiempo, por lo que una cantidad más significativa para fines de diseño es el promedio de la disipación de potencia en Q2, que es VDD·IQ. ETAPAS DE SALIDA Etapa de salida Clase A Eficiencia de conversión de potencia La eficiencia de conversión de potencia de una etapa de salida se define como: η= potencia de carga (PL) potencia de alimentación (PS) Para el seguidor de emisor considerado si se supone que el voltaje de salida es una senoide con valor de pico V0, el promedio de potencia en la carga será: P L= 2 1 (V0) 2 RL La potencia suministrada por la fuente de alimentación es: PS=2· VDD·IQ Por tanto la eficiencia de conversión de potencia será: tecnun η= (V0)2 4· VDD·IQ· RL 5 ETAPAS DE SALIDA Etapa de salida Clase A Eficiencia de conversión de potencia Como se ha visto anteriormente la amplitud máx. de señal de salida que puede obtenerse, considerando vCE1=0 es: V0=VDD=RL·I Q Por tanto la máx. eficiencia de conversión de potencia que se puede obtener mediante una etapa de salida clase A es: (VDD)2 (V0)2 η= = 0.25 Æ 25% = 4· VDD·IQ· RL 4· (VDD)2 tecnun La eficiencia máx. alcanzable del 25% es más bien baja, por lo que no suele emplearse como etapa de salida en aplicaciones de gran potencia (>1W). Por otra parte la tensión de salida suele limitarse a valores más pequeños para evitar la saturación de los transistores y la consiguiente distorsión no lineal, por lo que la eficiencia que se alcanza normalmente es de 10% a 20%. 6