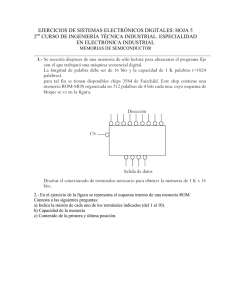

Memorias

Anuncio

Memorias

a3 a2 a1 a0 d3

1 1 1 1 0

1 1 1 0 0

1 1 0 1 1

1 1 0 0 1

1 0 1 1 0

1 0 1 0 1

1 0 0 1 0

1 0 0 0 1

0 1 1 1 0

0 1 1 0 1

0 1 0 1 0

0 1 0 0 0

0 0 1 1 0

0 0 1 0 1

0 0 0 1 1

0 0 0 0 1

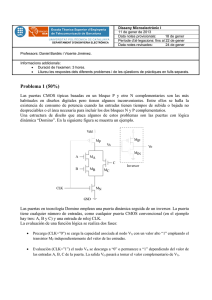

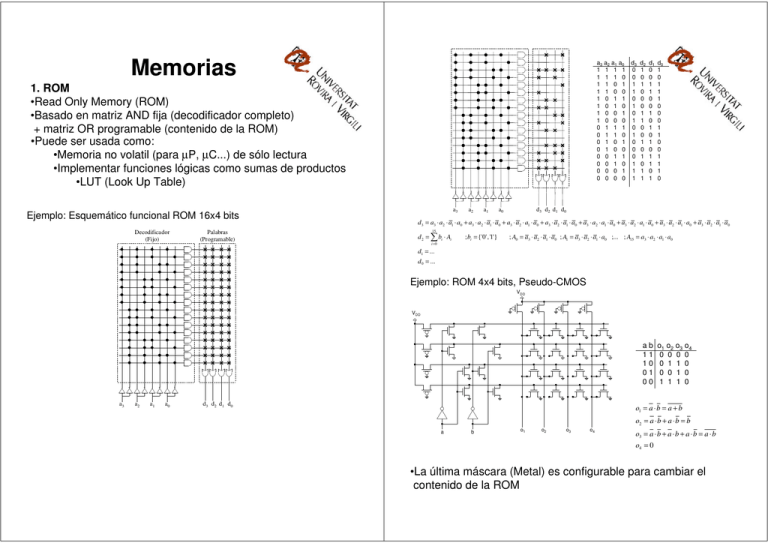

1. ROM

•Read Only Memory (ROM)

•Basado en matriz AND fija (decodificador completo)

+ matriz OR programable (contenido de la ROM)

•Puede ser usada como:

•Memoria no volatil (para µP, µC...) de sólo lectura

•Implementar funciones lógicas como sumas de productos

•LUT (Look Up Table)

Ejemplo: Esquemático funcional ROM 16x4 bits

Decodificador

(Fijo)

Palabras

(Programable)

a3

a2

a1

a0

d2

1

0

1

0

0

0

1

1

0

0

1

0

1

0

1

1

d1

0

0

1

1

0

0

1

0

1

0

1

0

1

1

0

1

d0

1

0

1

1

1

0

0

0

1

1

0

0

1

1

1

0

d3 d2 d1 d0

d 3 = a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0 + a3 ⋅ a2 ⋅ a1 ⋅ a0

15

d 2 = ∑ bi ⋅ Ai

; bi = {'0' , '1'}

; A0 = a3 ⋅ a2 ⋅ a1 ⋅ a0 ; A1 = a3 ⋅ a2 ⋅ a1 ⋅ a0 ;... ; A15 = a3 ⋅ a2 ⋅ a1 ⋅ a0

i =0

d1 = ...

d 0 = ...

Ejemplo: ROM 4x4 bits, Pseudo-CMOS

VDD

VDD

ab

11

10

01

00

a3

a2

a1

a0

d3 d2 d1 d0

o1 o2 o3 o4

0 0 0 0

0 1 1 0

0 0 1 0

1 1 1 0

o1 = a ⋅ b = a + b

o2 = a ⋅ b + a ⋅ b = b

a

b

o1

o2

o3

o4

o3 = a ⋅ b + a ⋅ b + a ⋅ b = a ⋅ b

o4 = 0

•La última máscara (Metal) es configurable para cambiar el

contenido de la ROM

Ejemplo: ROM 4x4 bits, precharge-evaluation

Ejemplo: EPROM 4x4 bits, pseudo-CMOS

•VPP/VDD es la tensión de programación (fase de programación)

o alimentación (fase ejecución)

•Los puertos o[1:4] son de entrada a ‘0’ o ‘1’ durante la fase de

grabación

VDD

φ

VDD

VDD

Prog

VPP/VDD

φ

a

o1

b

o2

o3

o4

•En una ROM:

•La última máscara (Metal) es configurable para cambiar el

contenido de la ROM

•En una EPROM:

•Se usa un transistor con puerta flotante

•Para la grabación se usa una tensión Vpp, para acumular

o no electrones en la puerta flotante

•Aquellos transistores con la puerta flotante cargada, no

conducen

•Borrado con ultravioleta (20 minutos)

VGS=VPP

-

GND

n+

e- - p

VGS=V DD

VDD

n+

B

Programación

GND

- - -

n+

UV

VDD

n+

p

B

Ejecución

- n+

n+

p

B

Borrado

a

b

o1

o2

o3

o4

2. SRAM

•Static Random Access Memory (SRAM)

•Bit basado en biestable (6 MOS por bit)

•Es una memoria volátil, de lectura/escritura

•Para ampliar el número de bits por palabra, se usan varias

matrices, con un amplificador R/W por bit y compartiendo

los decodificadores

•Puede usarse:

•Memoria de datos (para µP, µC...)

•Implementar funciones lógicas como LUT

Ejemplo: Amplificador R/W diferencial

VDD

VDD

WE

VDD

OE

b

b

d

b

b

OE

WE

aL

d

Lectura (OE=‘0’)

VDD

b

VDD

VDD

WE

OE

b

Amplificador b

R/W

b

OE

WE

Decodicador

columnas

WE OE CS

d

aH

Ciclo lectura / escritura SRAM (asíncrona)

...

......

... ...

...

...

...

...

...

...

A

... ...

... ...

... ...

... ...

...

CS

...

...

...

...

aL

Decodificador de filas

d

Decodicador

filas

Escritura (WE=‘0’)

dm-1

d1

d0

A1

A2

WE

OE

D

D1

D2

Decodificador de columnas

aH

Escritura

Lectura

3. DRAM

•Dynamic Random Access Memory (DRAM)

•Bit basado en carga en capacidad (1 MOS + 1 Cbit por bit)

•La capacidad Cbit suele ser una Cj parásita

•Es una memoria volátil, de lectura/escritura

•Necesita refresco periódico, para evitar la descarga de Cbit

•La lectura es destructiva. Necesita una escritura después

•Puede usarse:

•Memoria de datos (para µP, µC...)

•Implementar funciones lógicas como LUT

•El bus de direcciones suele ir multiplexado (filas/columnas)

•Método rápido de acceso sin cambiar columna

(misma página)

Capacidad Cj

Parásita

(0.30 fF)

Data

Data

Select

Select

a

d

Vbit

n+

Decodicador

filas

Registro

RAS

V bit(t ) = VDD − VTn −

∆Vbit

= 1.6

∆Vbit ⋅ t = 0.4V

RAS CAS

CS

Amplificadores

R/W y refresco

Decodicador

columnas

CS

CAS

Registro

VF

-

Cj

ID-INV

B(VSS)

V

ID

N

ID

P

ID-INV

Cj0/A

A

VF

Cj =

p

µs Trefresco = 250ns ⇒ f refresco = 4MHz

Cj/A

+

WE OE

Cj = 0.3 fF

I D − INV = 0.5 nA

I D − INV

⋅ t = VDD − VTn − ∆Vbit ⋅ t

Cj

n+

C j0

1 − VF

φ B

n

⋅A

1/2 step junction

1/3 linear junction

φB ≈ 0.7V n =

C BS1 ≈ C BM 0 ⋅ AS

ID-INV

C BD1 ≈ C BM 0 ⋅ AD

VD

+

VD

_

Ciclo lectura / escritura DRAM (asíncrona)

CS

A

A1ROW

A1COL

A2ROW

A2COL

RAS

CAS

WE

OE

Vbit=VDD-VTn

Cbit

‘0’

Vbit

Cbit

‘1’

‘1’

Vbit=VDD -VTn

Cbit

D1

D

D2

Escritura

Lectura

Ciclo refresco DRAM (asíncrona)

Ccol

Vcol=0V

Vcol

Ccol

Amplificador

lectura

Amplificador

+

Vbit =

Qbit

= VDD − VTn

Cbit

_

Vcol=VDD

Ccol

Amplificador

escritura

Ccol

A

A1ROW

RAS

CAS

+

Cbit

CS

Vcol = 0V

WE

_

OE

Vbit =

Vbit = Vcol ⇒

Qbit − Qcol

Cbit

_

D

+

+

Cbit

Ccol

Vcol =

_

Qcol

= Vbit

Ccol

Qbit − Qcol Qcol

Ccol

Cbit

=

⇒ Qcol =

⋅ Qcol ⇒ Vcol =

⋅ (VDD − VTn ) ≈ 0V

Cbit

Ccol

Cbit + Ccol

Cbit + Ccol

Refresco