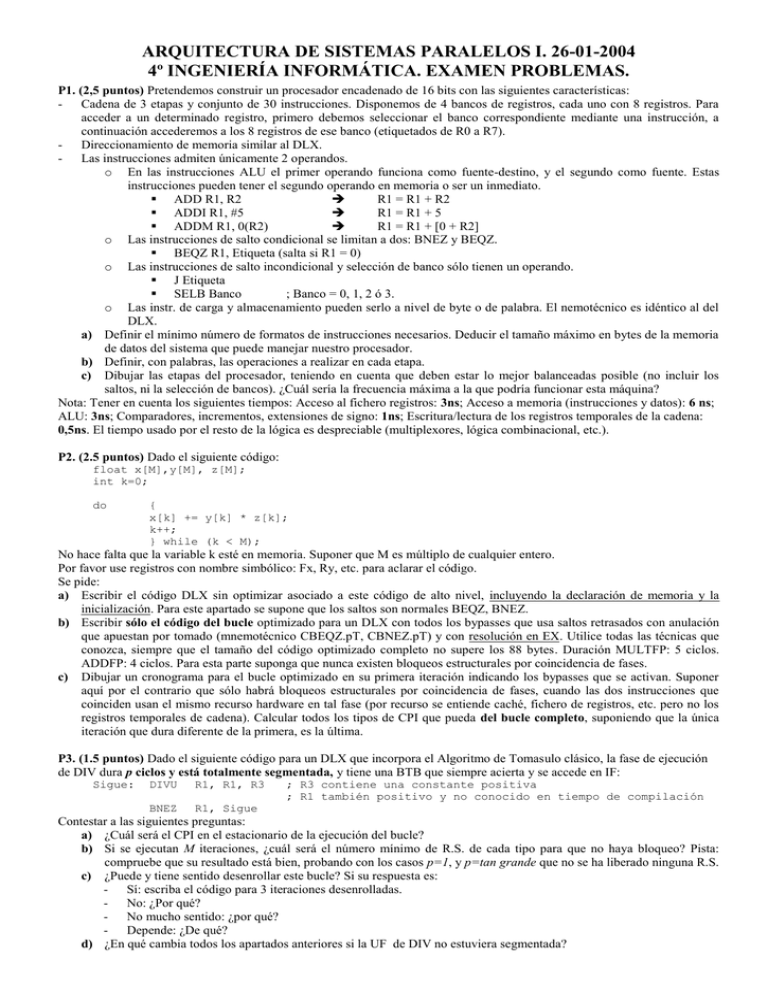

ARQUITECTURA DE SISTEMAS PARALELOS I. 26-01-2004 4º INGENIERÍA INFORMÁTICA. EXAMEN PROBLEMAS.

Anuncio

ARQUITECTURA DE SISTEMAS PARALELOS I. 26-01-2004

4º INGENIERÍA INFORMÁTICA. EXAMEN PROBLEMAS.

P1. (2,5 puntos) Pretendemos construir un procesador encadenado de 16 bits con las siguientes características:

- Cadena de 3 etapas y conjunto de 30 instrucciones. Disponemos de 4 bancos de registros, cada uno con 8 registros. Para

acceder a un determinado registro, primero debemos seleccionar el banco correspondiente mediante una instrucción, a

continuación accederemos a los 8 registros de ese banco (etiquetados de R0 a R7).

- Direccionamiento de memoria similar al DLX.

- Las instrucciones admiten únicamente 2 operandos.

o En las instrucciones ALU el primer operando funciona como fuente-destino, y el segundo como fuente. Estas

instrucciones pueden tener el segundo operando en memoria o ser un inmediato.

ADD R1, R2

R1 = R1 + R2

ADDI R1, #5

R1 = R1 + 5

ADDM R1, 0(R2)

R1 = R1 + [0 + R2]

o Las instrucciones de salto condicional se limitan a dos: BNEZ y BEQZ.

BEQZ R1, Etiqueta (salta si R1 = 0)

o Las instrucciones de salto incondicional y selección de banco sólo tienen un operando.

J Etiqueta

SELB Banco

; Banco = 0, 1, 2 ó 3.

o Las instr. de carga y almacenamiento pueden serlo a nivel de byte o de palabra. El nemotécnico es idéntico al del

DLX.

a) Definir el mínimo número de formatos de instrucciones necesarios. Deducir el tamaño máximo en bytes de la memoria

de datos del sistema que puede manejar nuestro procesador.

b) Definir, con palabras, las operaciones a realizar en cada etapa.

c) Dibujar las etapas del procesador, teniendo en cuenta que deben estar lo mejor balanceadas posible (no incluir los

saltos, ni la selección de bancos). ¿Cuál sería la frecuencia máxima a la que podría funcionar esta máquina?

Nota: Tener en cuenta los siguientes tiempos: Acceso al fichero registros: 3ns; Acceso a memoria (instrucciones y datos): 6 ns;

ALU: 3ns; Comparadores, incrementos, extensiones de signo: 1ns; Escritura/lectura de los registros temporales de la cadena:

0,5ns. El tiempo usado por el resto de la lógica es despreciable (multiplexores, lógica combinacional, etc.).

P2. (2.5 puntos) Dado el siguiente código:

float x[M],y[M], z[M];

int k=0;

do

{

x[k] += y[k] * z[k];

k++;

} while (k < M);

No hace falta que la variable k esté en memoria. Suponer que M es múltiplo de cualquier entero.

Por favor use registros con nombre simbólico: Fx, Ry, etc. para aclarar el código.

Se pide:

a) Escribir el código DLX sin optimizar asociado a este código de alto nivel, incluyendo la declaración de memoria y la

inicialización. Para este apartado se supone que los saltos son normales BEQZ, BNEZ.

b) Escribir sólo el código del bucle optimizado para un DLX con todos los bypasses que usa saltos retrasados con anulación

que apuestan por tomado (mnemotécnico CBEQZ.pT, CBNEZ.pT) y con resolución en EX. Utilice todas las técnicas que

conozca, siempre que el tamaño del código optimizado completo no supere los 88 bytes. Duración MULTFP: 5 ciclos.

ADDFP: 4 ciclos. Para esta parte suponga que nunca existen bloqueos estructurales por coincidencia de fases.

c) Dibujar un cronograma para el bucle optimizado en su primera iteración indicando los bypasses que se activan. Suponer

aquí por el contrario que sólo habrá bloqueos estructurales por coincidencia de fases, cuando las dos instrucciones que

coinciden usan el mismo recurso hardware en tal fase (por recurso se entiende caché, fichero de registros, etc. pero no los

registros temporales de cadena). Calcular todos los tipos de CPI que pueda del bucle completo, suponiendo que la única

iteración que dura diferente de la primera, es la última.

P3. (1.5 puntos) Dado el siguiente código para un DLX que incorpora el Algoritmo de Tomasulo clásico, la fase de ejecución

de DIV dura p ciclos y está totalmente segmentada, y tiene una BTB que siempre acierta y se accede en IF:

Sigue:

DIVU

R1, R1, R3

BNEZ

R1, Sigue

; R3 contiene una constante positiva

; R1 también positivo y no conocido en tiempo de compilación

Contestar a las siguientes preguntas:

a) ¿Cuál será el CPI en el estacionario de la ejecución del bucle?

b) Si se ejecutan M iteraciones, ¿cuál será el número mínimo de R.S. de cada tipo para que no haya bloqueo? Pista:

compruebe que su resultado está bien, probando con los casos p=1, y p=tan grande que no se ha liberado ninguna R.S.

c) ¿Puede y tiene sentido desenrollar este bucle? Si su respuesta es:

- Sí: escriba el código para 3 iteraciones desenrolladas.

- No: ¿Por qué?

- No mucho sentido: ¿por qué?

- Depende: ¿De qué?

d) ¿En qué cambia todos los apartados anteriores si la UF de DIV no estuviera segmentada?

ARQUITECTURA DE SISTEMAS PARALELOS I. 26-01-2004

4º INGENIERÍA INFORMÁTICA. EXAMEN PROBLEMAS.

Teoría: Las respuestas de verdadero/falso con una razón incorrecta se consideran inválidas.

a)

(0,3 puntos) En el DLX podríamos adelantar la resolución del salto a la etapa IF simplemente colocando un sumador para

calcular la dirección de salto y un comparador para evaluar la condición del salto.

V/F

Razón:

b) (0,3 puntos) Cuando utilizamos la medida MIPS para evaluar el rendimiento de una máquina, el valor obtenido puede

variar para distintos programas en un mismo computador

V/F

Razón:

c)

(0,3 puntos) Si añadimos un coprocesador conseguimos ejecutar las instrucciones de punto flotante 20 veces más rápido.

Si el porcentaje de este tipo de instrucciones es del 35%, ¿Cuál es la aceleración final obtenida?.

V/F

Razón:

d) (0,3 puntos) Si tenemos una máquina secuencial y la segmentamos en 5 etapas, el periodo de la máquina segmentada es

1/5 del periodo de la máquina secuencial.

V/F

Razón:

e)

(0,5 puntos) Dibuje en un esquemático simple los caminos de bypass que se activarán en el siguiente código para un DLX.

LW R1,(R1)4

ADD R2,R1,R1

f)

(0,3 puntos) Para un DLX encadenado que resuelve saltos completamente en ID (sin BTB), ¿Puede aumentar la razón de

fallos (Miss Rate) del caché de instrucciones, respecto de un DLX ideal que resolviera los saltos completamente en IF?

Si/No Razón por que no; o caso en que sí:

g) (0,3 puntos) En una máquina con planificación dinámica similar al algoritmo de Tomasulo, pero con piscina de etiquetas

independiente de las RS (estaciones de reserva), la máquina no se bloquea en el ciclo IS en que se va a emitir un salto

condicional o un Store, si las etiquetas están agotadas pero no las estaciones de reserva.

V/F Razón:

h) (0,3 puntos) El siguiente cronograma se ha capturado de un simulador de DLX con Algoritmo de Tomasulo clásico, que

funciona correctamente, claro está. ¿Por qué se producen los ciclos de espera en el primer LD y ninguno en el segundo LD

(se supone que antes de estas instrucciones no había ninguna otra dependencia real, y que el acceso al caché de datos dura

siempre 3 ciclos y permite encadenamiento).

SD

(R1)8, F0

IF IS S1 S2 S3 WB

LD

F4, (R3)100

IF IS o o L1 L2 L3 WB

LD

F6, (R3)0

IF IS L1 L2 L3 WB

Razón:

ARQUITECTURA DE SISTEMAS PARALELOS I. 26-01-2004

4º INGENIERÍA INFORMÁTICA. EXAMEN PROBLEMAS.

(0.5 puntos) La siguiente traza en hexadecimal se ejecuta en el Visual BTB. Señalar en las máquinas de estado del croquis de la

BPB(1,2) (1 bit correlación, dos bits historia), cada transición que se produce en el salto señalado con un número entre

paréntesis, usando el mismo número. Como ejemplo, se da la transición inicial (1). Señalar también el valor del reg. correlación

tras cada instrucción (criterio: 0 es NT; 1 es T). El estado inicial se ha señalado con subrayado en las máquinas y se ha dado

para el reg. correlación.

REG CORR:

Inicial: 1

2 100

2 104

2 108

2 110 (1)

2 100

2 104

2 108

2 10c

2 110 (2)

2 100

2 104

2 108

2 110 (3)

2 100

2 104

2 108

2 10c

2 110 (4)

2 100

2 104

2 108

2 110 (5)

2 100

2 104

2 108

2 10c

2 110 (6)

M1 (REG CORRELACIÓN=1)

T

M0 (REG CORRELACIÓN=0)

T

NT

A/T

B/T

NT

A/T

T

T

NT

NT

C/NT

D/NT

T

(1)

B/T

T

T

NT

NT

C/NT

NT

D/NT

T

NT

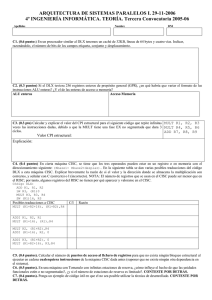

(0.4 puntos). Rellene la siguiente tabla con los números poniendo un 0 en la casilla del programa que tenga un valor inferior

típico para cada parámetro de la columna izquierda, un 9 para el que tenga un valor superior típico para tal parámetro, y un 5

para el que tenga un valor entre medio de los otros dos. Los tres programas se corresponden con traducciones de un mismo

bucle paralelizable en lenguaje de alto nivel que realiza una división entre elementos de dos vectores y el resultado lo almacena

en otro vector. Utilizar sólo los números 0, 5, 9. Cualquier contestación que utilice otros símbolos será incorrecta.

PARÁMETRO

Bucle original

Bucle desenrollado 3 iter. Prog. desenrolladas todas las iter.

Tamaño en bytes

CPIestructural

CPIdatos

Porcentaje de instr. overhead