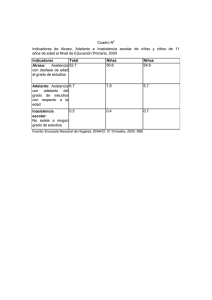

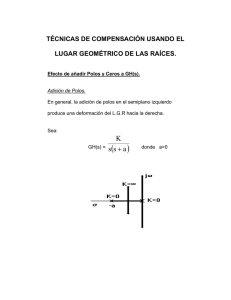

Diseño de Compensadores Mediante Lugar de Raíces

Anuncio

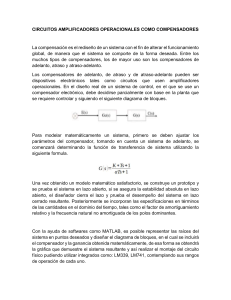

Diseño de Compensadores Mediante Lugar de Raíces Cátedras: - Control de Procesos - Control Avanzado y Automatismo Carrera: Bioingeniería Facultad de Ingeniería - UNER Tipos de compensadores y Atraso o retardo de Fase y Adelanto de Fase y Atraso - Adelanto Circuito de un Compensador T .s + 1 E ( s ) R 2.R 4 ( R1.C1.s + 1) = =Kβ β .T .s + 1 E ( s ) R1.R3 ( R 2.C 2.s + 1) o c i R 4.C1 R3.C 2 T = R1.C1 β .T = R 2.C 2 K = c R1.C1 < R 2.C 2 ⇒ Comp. ATRASO R1.C1 > R 2.C 2 ⇒ Comp. ADELANTO Cátedras de Control Facultad de Ingeniería - UNER 1 Introducción al Diseño de Compensadores mediante Lugar de Raíces (LR) y El diseño basado en el LR se emplea cuando las especificaciones vienen dadas en términos de la respuesta temporal: Tiempo de establecimiento, tiempo de subida, coeficiente de amortiguamiento, error en régimen permanente. y El objetivo general es fijar un punto sobre el plano complejo en base a las especificaciones para luego forzar a que las ramas del LdR pasen por él. Compensador en adelanto de fase G c (s) = K c .α 1 s+ (T .s + 1) T = Kc. 1 (α .T .s + 1) s+ αT con 0 < α < 1 y En serie con la planta, aporta un cero (-1/T) que es dominante con respecto al polo (-1/(αT)). y Efecto estabilizador: reducción de oscilaciones y mejora de los tiempos de respuesta. Pasos para el diseño del Comp. de ADELANTO mediante LR: 1. De las especificaciones de funcionamiento se determinan la ubicación deseada de los polos dominantes de lazo cerrado. 2. Ver si con el ajuste de la ganancia se logra los polos en lazo cerrado deseados. En caso negativo calcular la deficiencia angular que se compensara con la red de adelanto. Pd -180 = -αp1 -αp2 -αp3 -αpc +αcc Aporte ang. = αcc -αpc = αp1 +αp2 +αp3 -180 αpc αcc αp3 αp2 Cátedras de Control Facultad de Ingeniería - UNER αp1 2 Del compensador de Adelanto: alfa y T se determinan a partir de la deficiencia angular y Kc se determina a partir de la condición de módulo del LR. Primero ubicar el cero: 3. a) En la vertical de los polos deseados. b) Cancelando polo no dominante. Pd Pd c) Bisectriz. Pd 4. Calcular la ubicación del polo para cumplir con la condición de ángulo. Interesa un valor de alfa lo más grande posible. 5. Determinar Kc se determina a partir de la condición de módulo del LR. 6. Verificar las condiciones de diseño mediante la respuesta temporal en bucle cerrado Ejemplo: Considérese el siguiente sistema: G( s) = 4 s ( s + 2) Diseñar un controlador de ADELANTO que proporcione una respuesta en bucle cerrado con frecuencia natural no amortiguada (wn) de 4 rad/seg y coeficiente de amortiguamiento (zita) de 0.5. x(t) Gc(s) G(s) y(t) - Cátedras de Control Facultad de Ingeniería - UNER 3 Compensador en atraso de fase 1 s+ (T .s + 1) T = Kc G c (s) = K c . β . 1 ( β .T .s + 1) s+ βT con β > 1 y En serie con la planta, aporta un polo (-1/βT) que es dominante con respecto al cero (-1/T). y Efecto de reducción del error en régimen permanente. Pasos para el diseño del Comp. de ATRADO mediante LR 1. Trazar el lugar de las raíces e identificar los polos dominantes del sistema en bucle cerrado. Polos dominantes 2. Evaluar el coeficiente de error estático que se desea mejorar y calcular el valor de β necesario (Suponer Kc=1 con lo que el aporte lo hace todo beta). 3. Colocar el polo y cero del compensador en las proximidades del origen del plano s. Criterios: - Cero a 1/10 de la distancia al polo o cero del sistema en BA más cercano al origen. - Ángulo menor que 5º desde los polos dominantes. - Relación de módulos ≈1. Cátedras de Control Facultad de Ingeniería - UNER P.dom. 4 4. Calcular Kc para que los nuevos polos dominantes se sitúen lo más cerca posible de los antiguos. 5. Verificar el resultado. Mediante la respuesta temporal tanto del régimen permanente como del transitorio. Blanco: LdR antes de la compensación. Amarillo: LdR después de la compensación. Polos dominantes Ejemplo: Diseñar un compensador de ATRASO para incrementar la constante de error de velocidad del sistema tipo 1 que se indica hasta Kv=5 s−¹ sin afectar a su comportamiento dinámico. G(s) = x(t) 1.06 s (s + 1) (s + 2) Gc(s) G(s) y(t) - Compensador en atraso/adelanto de fase 1 ⎞ 1 ⎞⎛ ⎛ ⎟ ⎜ s+ ⎟⎜ s+ T T 1⎟⎜ 2 ⎟ ⎜ ,donde γ > 1, T 2 > T 1 y β > 1 Gc = K c ⎜ s+ γ ⎟⎜ s+ 1 ⎟ ⎟⎜ ⎜ ⎟ β T2 ⎠ T1 ⎠ ⎝ ⎝ y Combinación de factores en adelanto (cero en 1/´T1 y polo en -γ/T1) y atraso (polo en -1/βT2 y cero en -1/T2). Cátedras de Control Facultad de Ingeniería - UNER 5 Procedimiento de diseño por Lugar de Raíces: Pueden presentarse dos situaciones: A.- Si γ≠β: Se realizan dos diseños independientes, en adelanto con las especificaciones transitorias y en atraso con las permanentes. B.- Si γ=β: Diseño por aproximaciones debido a la falta de flexibilidad. Ejemplo: Diseñar un compensador de ATRASO - ADELANTO para tener un zita=0,5 un Wn=5 [rad/seg] e incrementar la constante de error de velocidad del sistema hasta Kv=80 s−¹. Obtener dos compensadores distintos para γ≠β y γ=β G(s) = x(t) Gc(s) 4 s (s + 0,5 ) G(s) y(t) - FIN !!!! Dudas …… Preguntas??? Cátedras de Control Facultad de Ingeniería - UNER 6