EXERCICIS D`ELECTRÒNICA DIGITAL

Anuncio

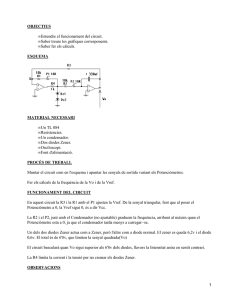

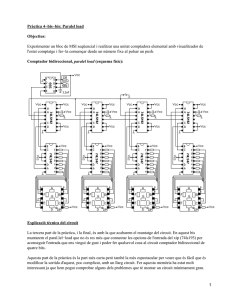

EXERCICIS D’ELECTRÒNICA DIGITAL – EXERCICI 5 Mínim 5 Aquests exercicis s’han de lliurar el dia 28 d’abril de 2008. 1 Es té un flip-flop J-K en el que J = K = 1, per a les entrades, i una senyal de rellotge de 10 kHz: a) Dibuixeu el cronograma de Q en funció del senyal de rellotge. Quina freqüència té Q? b) Dissenyeu un circuit amb flip-flops J-K, que obtingui un senyal de 2,5 kHz a partir d’un senyal de rellotge de 10 kHz (divisor de freqüència per quatre). c) Trobeu un exemple comercial de flip-flop J-K que permeti implementar el circuit de l’apartat b). d) Es vol implementar el rellotge que usa el circuit de l’apartat b) amb un LM555. Cerqueu el full de característiques d’aquest xip i indiqueu com el connectaríeu i quins valors de resistències i condensadors triaríeu per obtenir la freqüència desitjada. 2 a) Demostreu si el circuit següent es correspon amb algun latch RS, JK, D o T. 7406 A B 7402 Z C X2 D X1 b) Seria possible utilitzar-lo com a generador de trens de polsos? Què caldria fer? c) Per la situació demanada a l’apartat anterior i suposant que cada porta lògica té tPHL = tPLH = 5 ns, dibuixeu el cronograma dels senyals A, B, C, D i Z. Quina freqüència tindria Z? d) Implementeu el bloc latch de la figura anterior de manera directa a partir de la seva taula de veritat usant el mínim nombre possible de portes lògiques. 3 Demostrad que el circuito de la figura 1 es un “latch” RS con señal de Enable implementado con puertas NAND. Para ello resolved los siguientes apartados: a) Hallad las expresiones algebraicas de Q+ y Q_L+. Tratad las funciones Q+ y Q_L+ por separado, es decir, que en la expresión de Q+ sólo aparezcan R, S, E y Q y en la de Q_L+ aparezcan R, S, E y Q_L. (Nota: recordad que en este sistema asíncrono, la transición entre Q+ y Q se produce en el retardo de propagación del bucle de realimentación) b) Definid la tabla de transición de estados con entradas R, S, E y Q y salidas Q+ y Q_L+. (Nota: observad qué se produce cuando R = S = 1 y E = 1) c) Dibujad el cronograma de las salidas Q+ y Q_L+ cuando se introducen las señales RS dibujadas en la figura 2 (no hace falta tener en cuenta los retardos de las puertas). ¿En qué momento se produce el cambio de estado? Nota: Recordeu que _L correspon a la variable negada: A_L = Ā = A’ 4 Dissenyeu un circuit sumador de nombres de 4 bits : a) De manera combinacional, amb 4 sumadors complets d’un bit (el circuit tindrà 8 bits d’entrada i 4 de sortida) . b) De manera seqüencial, amb 1 sumador complet d’un bit i un flip-flop D (els bits de suma s’aniran introduint en sèrie (a0 i b0, a1 i b1,...) i el resultat de la suma anirà sortint seqüencialment per l’únic bit de sortida del sistema). El circuit tindrà dues entrades, cadascuna d’un bit, pels sumands, una sortida pel resultat i una entrada per indicar el inici de la suma. AJUT: el flip-flop s’haurà d’usar com a memòria on guardar el bit de “carry” entre suma i suma de cada parell de bits, és necessari posar a zero el Cin del sumador al principi de cada suma de quatre bits. c) Quins avantatges i inconvenients té cada disseny des del punt de vista de la velocitat i el nombre de portes que necessita cadascun? Hi ha algun disseny combinacional alternatiu als anteriors que incrementi la velocitat?