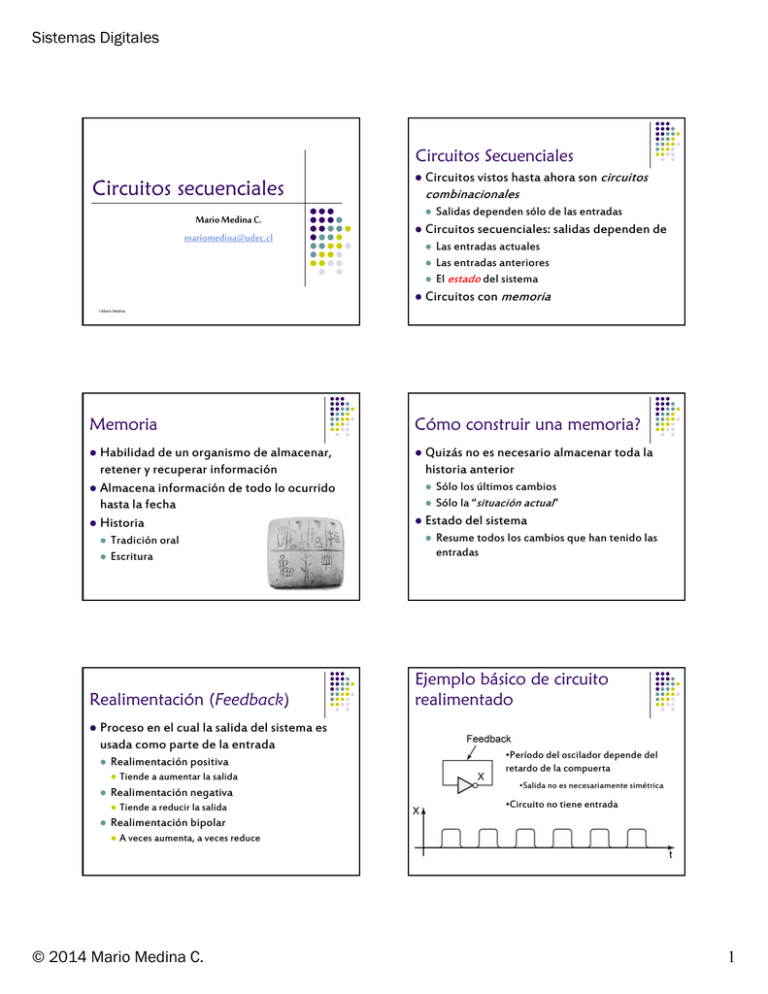

Circuitos secuenciales

Anuncio

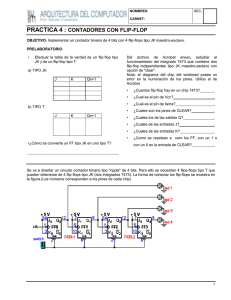

Sistemas Digitales Circuitos Secuenciales Circuitos secuenciales Mario Medina C. mariomedina@udec.cl Circuitos vistos hasta ahora son circuitos combinacionales Circuitos secuenciales: salidas dependen de Salidas dependen sólo de las entradas Las entradas actuales Las entradas anteriores El estado del sistema Circuitos con memoria Mario Medina Memoria Cómo construir una memoria? Habilidad de un organismo de almacenar, retener y recuperar información Almacena información de todo lo ocurrido hasta la fecha Historia Tradición oral Escritura Realimentación (Feedback) Proceso en el cual la salida del sistema es usada como parte de la entrada Realimentación positiva Realimentación negativa Tiende a aumentar la salida Tiende a reducir la salida Quizás no es necesario almacenar toda la historia anterior Sólo los últimos cambios Sólo la “situación actual” Estado del sistema Resume todos los cambios que han tenido las entradas Ejemplo básico de circuito realimentado •Período del oscilador depende del retardo de la compuerta •Salida no es necesariamente simétrica •Circuito no tiene entrada Realimentación bipolar A veces aumenta, a veces reduce © 2014 Mario Medina C. 1 Sistemas Digitales Oscilador de anillo en base a inversores Ejemplo de circuito realimentado A B C D E Inversores realimentados mantienen valor sin importar la entrada X Salida A B Valor de salida puede controlarse con un MUX C Realimentación Entrada Salida tiene período 10 (5 ciclos en 1 y 5 ciclos en 0) Elemento básico de memoria Puede construirse con compuertas NOR acopladas También pueden usarse compuertas NAND R Salida Latch básico Retentor o latch básico MUX D E Latch básico con NORs Entrada R: Reset Entrada S: Set Latch básico con NANDs Entradas negadas Q R S S Operación de Set y Reset Q’ Tabla de verdad circuito RS S R Q 0 0 Q anterior 0 1 0 1 0 1 1 1 Inestable •Entrada S (Set): salida es 1 •Entrada R (Reset): salida es 0 •Qué pasa si RS = 11? R S Q Q’ •Salida Q es 0 •Y cuánto vale Q’? © 2014 Mario Medina C. 2 Sistemas Digitales Comportamiento del circuito Si RS = 11, tanto Q como Q’ toman el valor 0 Comportamiento del circuito Entradas prohibidas Salida QQ’ = 00 No se cumple la condición (Q)’ = Q’ Si RS=11 y ambas entradas cambian al mismo tiempo a RS=00, las salidas oscilan QQ’ cambian a 11 y luego a 00 y luego a 11 y así Condición de carrera Se puede dar si los retardos de ambas compuertas son exactamente iguales Condición termina si una salida cambia antes que la otra Diagrama de estados operación Set y Reset. R S Q Q’ Q y Q’ tienen el mismo valor Comportamiento observado SR=00,01 SR=00,01 QQ’=01 QQ’=01 SR=01 SR=11 SR=01 SR=11 SR=10 SR=00 SR=00 SR=00, 11 SR=01 SR=10 SR=11 SR=11 QQ’=00 QQ’=10 SR=01 QQ’=10 SR=01 SR=00,10 SR=10 SR=00,10 SR=10 SR=11 QQ’=00 SR=00 SR=10 SR=11 Ante entrada SR=00, estado QQ’ puede transitar a cualquiera de los dos estados QQ’=11 Latch R-S Latch RS 74LS279 S(t) R(t) Q(t) Q(t + ∆t) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 X X 1 1 X X Ecuación Característica Q(t+ ∆t) = S(t) + R’(T)Q(t) SR S 00 01 11 10 0 0 0 X 1 1 1 0 X 1 Q( t ) R SR = 10 SR = -0 SR = 00 1 SR = 01 © 2014 Mario Medina C. 3 Sistemas Digitales Retentores (latches) Salidas de retentores (latches) cambian al cambiar sus entradas Retentores asincrónicos Circuito biestable no sincronizado Latch R-S activado por nivel Si EN es 0, salida Q no cambia Si EN es 1, Q reacciona ante cambios en R y S Mantiene el último estado No depende de señal de reloj Es la base para otros circuitos Alternativas Retentores activados por nivel Retentores activados por cambio de nivel Latch R-S activado por nivel Salida Q sólo cambia cuando entrada EN está activada Retentores y flip-flops Retentor ó latch: dispositivo secuencial que monitorea de forma continua todas sus entradas y cambia sus salidas en cualquier tiempo independientemente de la señal de reloj Flip-Flop: dispositivo secuencial que cambia sus salidas en tiempos determinados por una señal de reloj Flip-flop RS activado por canto de subida del reloj Salidas de flip-flops cambian dependiendo de señal de reloj Flip-flop maestro-esclavo Retentores y Flip-Flops Construidos en base a latches R-S Activados por Canto o flanco de subida Canto o flanco de bajada Indicado por triángulo Indicado por triángulo y burbuja © 2014 Mario Medina C. 4 Sistemas Digitales Flip-flop RS maestro-esclavo Flip-flop R-S maestro-esclavo Utiliza 2 latches RS Primer latch controlado por semiperíodo activo bajo del reloj Segundo latch controlado por semiperíodo activo alto del reloj Cuando reloj es 0, entradas RS se reflejan en variables intermedias P y P’ Cuando reloj es 1, P y P’ se reflejan en Q y Q’ Salidas Q y Q’ cambian sólo en el canto de subida del reloj Latch J-K Latch J-K J(t) K(t) Q(t) Q(t + ∆t) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0 Ecuación Característica •Evita estado inestable del latch R-S •Si JK=11, latch cambia de estado (Toggle) •Puede tener oscilaciones Q(t+ ∆t) = Q(t)K’(t) + Q’(T)J(t) JK J 00 01 11 10 0 0 0 1 1 1 1 0 0 1 Q( t ) K J R Q Latch R-S S Q’ K JK = 1JK = 00 1 JK = -1 JK = -0 Flip-flop JK maestro-esclavo Construcción similar a RS maestro-esclavo Un solo cambio de estado por cada ciclo de reloj Flip-flop J-K maestro-esclavo Entradas son muestreadas sólo si el reloj es 1 Cambios en entradas si reloj es 0 son ignoradas Salidas Q y Q’ cambian sólo en el canto de bajada o flanco de bajada del reloj © 2014 Mario Medina C. K J R S Q Latch R-S Q’ P P’ R S Q Latch R-S Q’ Reloj 5 Sistemas Digitales JK Maestro-Esclavo “1s catching” En ejemplo anterior, ciclo 3, J cambió brevemente de 0 a 1 a 0 mientras el reloj estaba en 1 Salida P cambia a 1, aun cuando J es 0 en el cambio de reloj siguiente Problema inherente a flip-flops maestro-esclavo Circuitos latch construidos con NAND sufren de “0 catching” Solución: reducir ciclo activo de primer latch Flip-flop J-K con detección de pulsos Flip-flop J-K con detección de pulsos Flip-flop J-K con detección de pulsos Comportamiento Comportamiento para JK=11 Flip-Flop D (Data) Símbolo Ecuación Característica D(t) Q(t) 0 0 0 1 1 0 1 1 Q(t+ 1) 0 0 1 1 Q(t+ 1) = D(t) D Q 0 1 0 0 1 1 0 1 D=1 D=0 0 1 D=1 D=0 © 2014 Mario Medina C. 6 Sistemas Digitales Latch D activado por nivel Latch D activado por nivel GDQ 000 001 010 011 100 101 110 111 Quad Latch D LS7475 Q+ 0 1 0 1 0 0 1 1 Retentores y flip-flops D Una sola entrada de datos D Salida refleja la entrada con el cambio de reloj Retentor ó latch D activado por nivel Flip-flop activado por cantos Flanco o canto de subida Flanco o canto de bajada Q Q’ Flip-flop D construido usando latches D Flip-Flop D 100 D Clk Q Q' Q Q' © 2014 Mario Medina C. Canto de Subida Canto de Bajada 7 Sistemas Digitales Flip-flop D activado por canto de subida Flip-flop T (Toggle) Este circuito usa 3 latches R-S para construir un flip-flop D activado por flanco de subida Una sola entrada de datos T Activado por canto Puede invertir el estado actual No sufre de “1s catching” T Q T Q Clock Q’ Clock Q’ Subida del reloj Flip-Flop T (Toggle) T(t) Q(t) Q(t+ 1) 0 0 0 0 1 1 1 0 1 1 1 •Generalmente se construye uniendo las entradas de un flip-flop JK Tiempos de conmutación Ecuación Característica Q(t+ 1) = Q(t) XOR T(t) D 0 Q 0 0 0 1 1 1 0 W(H) Clock T=0 Mínimo tiempo que las señales de entradas deben permanecer constantes Tiempo de mantención (th). Mínimo tiempo que las señales de entrada deben permanecer constantes después de aparecer el flanco de activación del reloj. 0 1 T=0 tPLH 50% th Clock Entrada tW(H) Flip-flops pueden implementarse en términos de otros flip-flops Dato válido Entrada de reloj en alto. tPHL : tiempo de estabilidad. tPLH : tiempo de mantención. Implementando flip-flops ts tPHL A T=1 Violación ts Entrada © 2014 Mario Medina C. Entradas deben estar estables antes y después del reloj 50% t : Ancho de pulso T=1 Tiempos de estabilidad (ts). Necesarios para salidas y estados estables 1 Tiempos de conmutación Bajada del reloj Violación th T con JK D con JK JK con RS T con RS T con D Etc. 8 Sistemas Digitales Implementando flip-flops Señales CLEAR y PRESET Permiten dar valores iniciales al flip-flop Implementando flip-flops Flip-flop D activado por canto de subida con señales CLEAR y PRESET activas bajas CLEAR da valor inicial 0 PRESET da valor inicial 1 Activas altas o bajas Actúan asincrónicamente Dan valor inicial al flip-flop en forma independiente del clock Flip-Flop J-K con entradas de control Flip-Flop J-K con entradas de control LS74HC112 Dual flip-flop J-K activado por canto de bajada © 2014 Mario Medina C. Símbolo Comportamiento LS74HC112 Dual flip-flop J-K activado por canto de bajada 9 Sistemas Digitales LS7474 Dual flip-flop D activado por canto de subida Flip-flops en cascada Salida de un flip-flop es entrada al siguiente flip-flop Salida Q1 cambiará 2 ciclos de reloj después que entrada IN IN D Q Q0 CQ D Q Q1 CQ CLK Flip-flop como divisor de frecuencia Flip-flops en cascada Cambios en la entrada se reflejan 2 ciclos de reloj después Diagrama supone FF con canto de subida 100 Flip-flop actúa como flop-flop T Salida es un reloj cuya frecuencia es la mitad del reloj de entrada In Q0 Q1 Clk Flip-flop como divisor de frecuencia Flip-flops actúan como flip-flop T Salida QA se conecta a reloj del flip-flop B Frecuencia de salida es un 1/4 de la frecuencia del reloj © 2014 Mario Medina C. Almacenamiento de datos 4 Flip-flips D en paralelo Almacenan palabra de 4 bits en forma simultánea Reloj común 10 Sistemas Digitales Flip-flops como generadores de secuencias Circuito genera secuencia 00, 01, 10, 11, 00 © 2014 Mario Medina C. 11