Sistema de memoria - Exabyte Informática

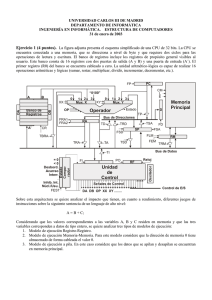

Anuncio