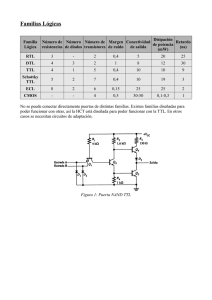

Familias Lógicas

Anuncio

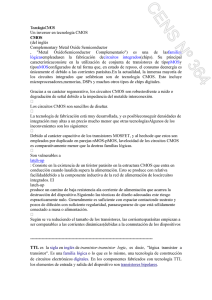

1 Electrónica Básica Familias Lógicas Electrónica Digital José Ramón Sendra Sendra Dpto. de Ingeniería Electrónica y Automática ULPGC Familias lógicas Basadas en transistores de efecto de campo CMOS: Complementary Metal-Oxide-Semiconductor Field Effect Transistor Basadas en transistores bipolares TTL: Transistor-Transistor logic ECL: Emiter-coupled logic El diseño lógico de un circuito combinacional es independiente de la tecnología usada, sin embargo la realización física de este circuito si debe tenerla en cuenta, por factores como: -Márgenes de ruido -Entorno de trabajo del circuito -Fanout -Necesidad de: -Velocidad -Salidas en colector abierto -Consumo -Salidas Three-state -Alimentación disponible 2 3 Familias lógicas: CMOS Inversor Veamos la configuración básica de un inversor (circuito más simple) para analizar sus características VDD =+5.0V G S D V IN V OUT D G Transistor p-MOS cerrado cuando VIN -VDD < VILmax-VDD ÞV IN <V ILmax Transistor n-MOS cerrado cuando V IN -0>VIHmin S Gnd 4 Familias lógicas: CMOS comportamiento eléctrico estático Niveles lógicos y margen de ruido Parámetros característicos V OHmin :Es la tensión de salida mínima que se garantiza en nivel alto. V IHmin :Es la mínima tensión de entrada que se garantiza será reconocida como nivel alto. VOLmax :Es la tensión de salida máxima que se garantiza en nivel bajo. V ILmax :Es la máxima tensión de entrada que se garantiza será reconocida como nivel bajo. 5 Familias lógicas: CMOS Los elementos lógicos abstractos procesan 0's y 1's. Los circuitos reales procesan señales eléctricas, en este caso niveles de tensión VDD Niveles lógicos para para puertas CMOS Nivel alto, 1 VOHmin VIHmin VILmax Gnd Nivel bajo, 0 VOLmax 6 Familias lógicas: CMOS Inversor VDD =+5.0V VDD =+5.0V Cerrado 0V VOH ~ 5V Abierto Abierto 5V VOL~0V Cerrado 7 Familias lógicas: CMOS comportamiento eléctrico estático Niveles lógicos y margen de ruido Los parámetros relacionados con los niveles lógicos nos dan información acerca de los niveles de ruido que será capaz de aceptar nuestra lógica sin que se corrompa la información. Estos parámetros pueden venir dados como valores absolutos o como relativos a la alimentación. Ejemplo: Serie HC atacando puertas CMOS VOHmin =4.9V VOLmax =0.1V VIHmin =3.5V VILmax =1.5V El margen de ruido será: Nivel alto 4.9V-3.5V=1.4V Nivel bajo 1.5V-0.1V=1.4V 8 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con cargas resistivas. 1.-En régimen estático cualquier carga es resistiva, por tanto este estudio es totalmente generalizable. 2.-Cualquier carga puede representarse por su equivalente de Thevenin VDD RThev VIN + V Thev - Gnd 9 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con cargas resistivas. Ejemplo VDD R 5V pOFF VOUT V VOUT= RThev + RnON V Thev - Gnd Thev ·R RThev+ RnON nON Si VOUT>VOLmax no podremos cargar nuestro inversor con ese circuito. 10 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con cargas resistivas. Ejemplo 2 VDD R 0V pON VOUT VOUT= ·R + V Thev RThev+ RpON Thev RThev + RnOFF VDD -V Thev V Thev - Gnd Si VOUT<VOHmin no podremos cargar nuestro inversor con ese circuito. 11 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con cargas resistivas. Desafortunadamente no conocemos las impedancias de los transistores, sólo conocemos los siguientes parámetros. I OLmax Máxima corriente que la salida puede absorber en estado bajo manteniendo una tensión de salida inferior a VOLmax I OHmax Máxima corriente que la salida puede generar en estado alto manteniendo una tensión de salida superior a VOHmin 12 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con cargas resistivas. Ω , VThev=3.5V Ejemplo: RThev=1KΩ Si consideramos RpON≈0Ω Ω VDD R 0V pON VOUT I OH = RThev 5-VThev RThev =1.5mA I OH debe ser < I OHmax + RnOFF V Thev - Gnd 13 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con cargas resistivas. Ω , VThev=3.5V Continuación del Ejemplo: RThev=1KΩ Si consideramos RnON≈0Ω Ω VDD R 5V pOFF VOUT I OH = RThev + RnON Gnd RThev Si I OH< IOHmax V Thev - VThev y Si I OL< IOLmax =3.5mA la puerta funcionará correctamente con esta carga 14 Familias lógicas: CMOS comportamiento eléctrico estático Fanout Definición: Es el número máximo de entradas con las que se puede cargar la salida de nuestra puerta lógica. IImax Es la máxima corriente de entrada que se necesita en la puerta de los transistores que forman la puerta lógica. Fanout=Min( I OLmax IILmax , I OHmax IIHmax Para puertas CMOS IILmax = I IHmax ) 15 Familias lógicas: CMOS comportamiento eléctrico estático Comportamiento con entradas no ideales VDD R VIN p(VIN-VDD) VOUT= RnVIN RnVIN ·VDD RnVIN +Rp(VIN-VDD) Si las entradas no son cercanas a las tensiones de alimentación y tierra, los transistores no están ni completamente abiertos, ni totalmente cerrados, de forma que los transistores en ON presentan una resistencia mayor de la ideal y los transistores en OFF menor. La potencia consumida es no nula, incluso sin carga y la salida no es la ideal Gnd 16 Familias lógicas: CMOS Puertas NAND, NOR NAND A NOR B A B Salida Salida A A B B 17 Familias lógicas: CMOS Puertas NAND, NOR Entradas sin usar. Ejemplo: Puerta AND de cuatro entradas, sólo tenemos tres literales. F=A·B·C=1·A·B·C VDD 1KΩ Ω 1 A B C F A B F C Nunca dejar una entrada sin conectar. (al aire) 18 Familias lógicas: CMOS comportamiento eléctrico dinámico Tiempo de transición: Es el tiempo que un circuito tarda en cambiar de estado. Es debido a que un cambio de estado requiere la carga de una serie de capacidades, entre las que cabe incluir: -La puerta de los transistores a la salida -Las capacidades del cableado -Los circuitos de entrada, el encapsulado,etc.... Transición ideal Transición real Nivel alto Nivel bajo tr tf Los tiempos tanto de subida como de bajada dependerán de la capacidad de carga así como de la resistencia en ON de los transistores y del cableado. 19 Familias lógicas: CMOS comportamiento eléctrico dinámico Análisis de los tiempos de transición VDD VIN Circuito equivalente de carga RL Rp CL Rn + - Gnd VL 20 Familias lógicas: CMOS comportamiento eléctrico dinámico Análisis de los tiempos de transición Carga de otra puerta CMOSÞ ÞRL =∞ ∞ ,V , L=0V VDD VIN VDD Circuito equivalente de carga RL Rp CL Rn - Gnd → + VL VIN Rp CL Rn Gnd 21 Familias lógicas: CMOS comportamiento eléctrico dinámico Análisis de los tiempos de transición VDD VIN Rp Rn Tiempo de subida − t RpONCL ö ÷ Vout = VDD • æçè 1 − e ø VOUT CL Ejemplo numérico Datos: VOLmax =1.5V VOHmin =3.5V R nON =200Ω Ω CL =100pF Gnd t r = t 3.5 V − t 1.5 V = −20 • 10 −9 • (ln(3.5 5) − ln(1.5 5)) = 17ns 22 Familias lógicas: CMOS comportamiento eléctrico dinámico Análisis de los tiempos de transición VDD VIN Rp Rn Tiempo de bajada Vout = VDD • e − t RnONCL VOUT CL Ejemplo numérico Datos: VOLmax=1.5V VOHmin =3.5V RnON =100Ω Ω C L =100pF Gnd t f = t 1.5 V − t 3.5 V = −10 • 10 −9 • (ln(3.5 / 5) − ln(1.5 5)) = 8.5ns 23 Familias lógicas: CMOS comportamiento eléctrico dinámico Retardo de propagación Se define como el tiempo que transcurre desde que se produce un cambio en la señal de entrada hasta que éste se refleja en la salida Se suele dar desde el punto medio del flanco de subida o bajada de forma que se eliminan en lo posible los tiempos de transición En caso de que se cargue una puerta en exceso los tiempos de transición harán incrementar el retardo de propagación. tpHL Retardo de propagación cuando la salida pasa de nivel alto a nivel bajo tpLH Retardo de propagación cuando la salida pasa de nivel bajo a nivel alto 24 Familias lógicas: CMOS comportamiento eléctrico dinámico Retardo de propagación tpHL t pHL tpLH tpLH 25 Familias lógicas: CMOS comportamiento eléctrico dinámico 1.-Se consume potencia cuando hay paso de corriente desde alimentación a tierra cuando la tensión de entrada está lejos de la alimentación y la tierra, es decir en las transiciones. 2 PT = C PD • VDD •f Tiene magnitud de capacidad aunque no lo es. Viene dado por el fabricante Tensión de alimentación Frecuencia de las transiciones Esta fórmula deja de ser correcta cuando las transiciones son muy lentas. Los fabricantes dan un tiempo máximo para estas de forma que si se excede, el valor de C PD no es correcto 26 Familias lógicas: CMOS comportamiento eléctrico dinámico 2.-Se consume potencia cuando cargamos la carga capacitiva a la salida. Esta capacidad es debida a las conexiones y a la impedancia de carga. 2 PL = C L • VDD •f Capacidad que carga la salida de la puerta lógica. Tensión de alimentación Frecuencia de las transiciones Potencia total 2 PD = (C PD + C L ) • VDD •f 27 Familias lógicas: CMOS Dispositivos con entrada Schmitt-Trigger VOUT Función de Transferencia 5.0 Símbolo de un inversor Schmitt-Trigger 0.0 VIN 2.1 2.9 5.0 Este tipo de dispositivos son más inmunes al ruido y son usadas ordinariamente para señales en líneas de transmisión. 28 Familias lógicas: CMOS Dispositivos con salida Three-State Símbolo de una puerta NAND con Enable A B Enable Salida Enable A B Puerta NOR Enable A B Z 29 Familias lógicas: CMOS Dispositivos con salida Three-State Tabla de verdad A B Enable Salida Enable A B Puerta NOR Enable 0 0 0 0 1 1 1 1 A 0 0 1 1 0 0 1 1 B 0 1 0 1 0 1 0 1 Salida Z Z Z Z 1 0 0 0 Z significa Alta Impedancia 30 Familias lógicas: CMOS Salidas en colector abierto VDD Símbolo de una puerta NAND con salida en colector abierto A B Z VOUT Tabla de verdad A B Gnd NAND A 0 0 1 1 B 0 1 0 1 Salida Abierta Abierta Abierta 0 31 Familias lógicas: CMOS Salidas en colector abierto VDD Para el funcionamiento de estas puertas debe conectarse una resistencia de pull-up VOUT A Su valor máximo vendrá fijado por: I OLmax =VDD/R B pull-up Gnd NAND El valor de la resistencia que pongamos va a fijar: I OHmax=(VDD -VOHmin )/Rpull-up Rpull-up·Ccarga Þt pLH 32 Familias lógicas: TTL Características diferenciadoras respecto a CMOS Los transistores usados son bipolares, esto implica: corrientes de entrada mucho mayores consumo de potencia en estática ¿mayor velocidad? Podemos apreciar en los niveles lógicos, que no son simétricos VDD Niveles lógicos indicativos para puertas TTL Nivel alto, 1 VOHmin (2.7V) VIHmin (2.0V) VILmax (0.8V) Gnd Nivel bajo, 0 VOLmax (0.5V) 33 Compatibilidad entre CMOS y TTL -Hay una diferencia apreciable entre los niveles lógicos de ambos tipos de dispositivos. -Cuando cargamos una puerta CMOS con una TTL estamos exigiendo mayor corriente y por lo tanto los niveles lógicos de salida disminuyen -Las características que ofrecen los fabricantes, tanto para IOLmax y IOHmax como para VOLmax y VOHmin dependen del tipo de puerta con que estemos cargando. Ejemplo: Familia HC con VDD=5.0V Carga CMOS Carga TTL IOLmaxC VOLmaxC IOHmaxC VOHminC 4 mA 0.33 V -4 mA 4.3 V 0.02 mA 0.1 V -0.02 mA 4.9 V IOLmaxT VOLmaxT IOHmaxT VOHminT 34 Compatibilidad entre CMOS y TTL VDD Nivel alto, 1 TTL VOHmin (2.7V) VIHmin (2.0V) VILmax (0.8V) Nivel bajo, 0 VOLmax (0.5V) Nivel alto, 1 VOHmin(4.3V) Gnd VDD CMOS VIHmin(3.5V) VILmax(1.5V) Gnd Nivel bajo, 0 VOLmax(0.33V) 35 Compatibilidad entre CMOS y TTL Familias CMOS actuales 4000 Son las primeras pero están en desuso, admiten gran rango de alimentaciones y son muy robustas pero muy lentas. HC y HCT Las siglas significan High-speed CMOS y High-speed CMOS TTL-compatible AC y ACT Son mucho más rápidas que las anteriores y eliminan el problema de la poca cantidad de corriente a la salida que eran capaces de suministrar HC y HCT sus siglas significan Advanced CMOS y Advanced CMOS TTL-compatible La única diferencia de los dispositivos TTL compatibles con los que no lo son radica en los niveles lógicos a la entrada. 36 Compatibilidad entre CMOS y TTL Familias CMOS actuales FCT y FCT-T Salió a principios de esta década reduce el consumo de potencia y disminuye los retardos. Ambas son TTL compatibles, la diferencia radica en que la segunda reduce el nivel de salida a nivel alto (como las TTL), reduciendo así más el consumo de potencia. Importante FCT, FCT-T Prestaciones AC, ACT HC, HCT - Velocidad ↑ - Consumo ↓ Precio ↑ 37 Compatibilidad entre CMOS y TTL Familias TTL actuales S Shottky TTL LS Low-power Shottky TTL AS Advanced Shottky TTL ALS Advanced Low-power Shottky TTL F Fast TTL 38 Compatibilidad entre CMOS y TTL Salidas Entradas 5.0V HC, HCT 3.98 Nivel alto AC, ACT 3.94 3.15 HC, AC VOHmin Margen de ruido V ILmax a nivel alto LS, S , ALS, AS 2.7 Zona no válida V OLmax LS, S , ALS, AS 0.5 AC, ACT 0.37 HC, HCT 0.33 2.0 LS, S, ALS, AS, HCT, ACT 1.35 HC, AC 0.8 LS, S, ALS, AS, HCT, ACT Nivel bajo Margen de ruido a nivel bajo VIHmin 39 Familias lógicas: ECL Produce diferencias de tensión pequeñas, menores de 1 voltio, entre los niveles alto y bajo. Sus niveles de alimentación son 0V y entre -4.5 y -5.2V VIHmax -0.810 VIHmin -1.105 VILmax -1.475 VILmin -1.850 -0.810 VOHmax -0.980 VOHmin -1.630 VOLmax -1.850 VOLmin Las potencias consumidas son altas >20mW por puerta Los retardos y tiempos de transición son muy bajos ≈ 1ns 40 Familias lógicas: Generalidades Modelo de caja negra: Los parámetros descritos anteriormente van a ser útiles para cualquier familia lógica, no necesitamos saber como está estructurado internamente un dispositivo sino cuales son sus parámetros de funcionamiento. Alimentación VIHmin VILmax IIHmax IILmax CINtyp VOHmin VOLmax IOLmax IOHmax . .. tPLH tPHL Fanout Entradas Salidas Alimentación