Familias Lógicas

Anuncio

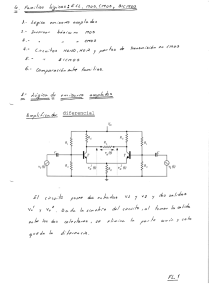

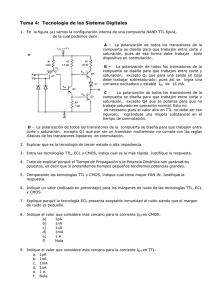

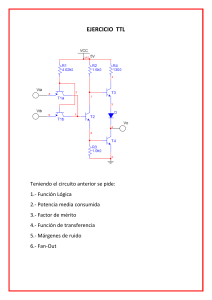

Familias Lógicas Familia Lógica Disipación Número de Número Número de Margen Conectividad Retardo de potencia resistencias de diodos transistores de ruido de salida (ns) (mW) RTL 3 - 2 0,4 5 20 25 DTL 4 3 2 1 8 12 30 TTL 4 1 5 0,4 10 10 9 Schottky TTL 5 2 7 0,4 10 19 3 ECL 8 2 6 0,15 25 25 2 CMOS - - 4 0,5 30-50 0,1-0,3 1 No se puede conectar directamente puertas de distintas familias. Existen familias diseñadas para poder funcionar con otras, así la HCT está diseñada para poder funcionar con la TTL. En otros casos se necesitan circuitos de adaptación. Figura 1: Puerta NAND TTL Salidas Las salidas normales no pueden conectarse entre sí. Ejemplo dos inversores conectados. Drenador Abierto Entrada A Entrada B Q3 Q4 Salida L L Off Off open L H Off On open H L On Off open H H On On L Figura 2: Puerta NAND con drenador abierto Requiere de una resistencia (llamada resistencia de pull-up) externa para su correcto funcionamiento Alta impedancia Figura 3: a) Inversor CMOS triestado Posibilita la conexión a un bus. b) NAND CMOS triestado