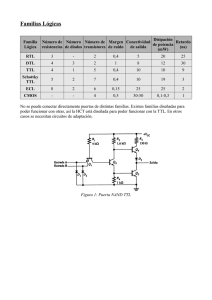

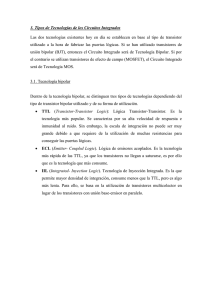

Tema 4: Tecnología de los Sistema Digitales

Anuncio

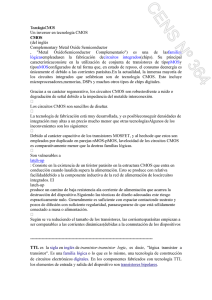

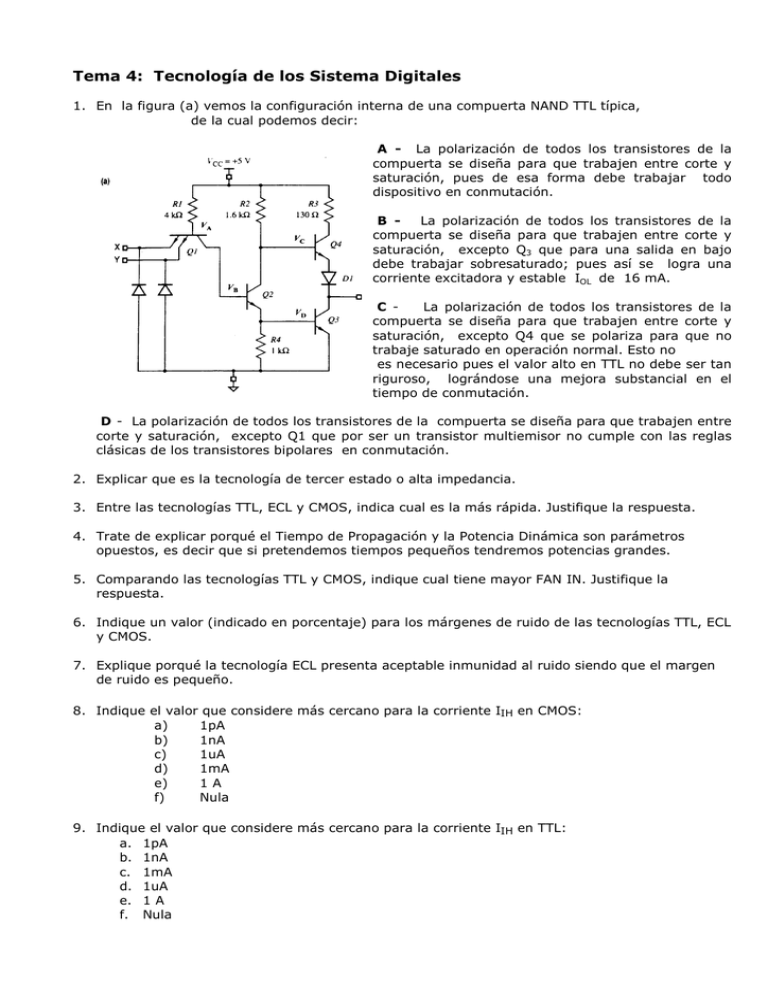

Tema 4: Tecnología de los Sistema Digitales 1. En la figura (a) vemos la configuración interna de una compuerta NAND TTL típica, de la cual podemos decir: A - La polarización de todos los transistores de la compuerta se diseña para que trabajen entre corte y saturación, pues de esa forma debe trabajar todo dispositivo en conmutación. B La polarización de todos los transistores de la compuerta se diseña para que trabajen entre corte y saturación, excepto Q3 que para una salida en bajo debe trabajar sobresaturado; pues así se logra una corriente excitadora y estable IOL de 16 mA. C La polarización de todos los transistores de la compuerta se diseña para que trabajen entre corte y saturación, excepto Q4 que se polariza para que no trabaje saturado en operación normal. Esto no es necesario pues el valor alto en TTL no debe ser tan riguroso, lográndose una mejora substancial en el tiempo de conmutación. D - La polarización de todos los transistores de la compuerta se diseña para que trabajen entre corte y saturación, excepto Q1 que por ser un transistor multiemisor no cumple con las reglas clásicas de los transistores bipolares en conmutación. 2. Explicar que es la tecnología de tercer estado o alta impedancia. 3. Entre las tecnologías TTL, ECL y CMOS, indica cual es la más rápida. Justifique la respuesta. 4. Trate de explicar porqué el Tiempo de Propagación y la Potencia Dinámica son parámetros opuestos, es decir que si pretendemos tiempos pequeños tendremos potencias grandes. 5. Comparando las tecnologías TTL y CMOS, indique cual tiene mayor FAN IN. Justifique la respuesta. 6. Indique un valor (indicado en porcentaje) para los márgenes de ruido de las tecnologías TTL, ECL y CMOS. 7. Explique porqué la tecnología ECL presenta aceptable inmunidad al ruido siendo que el margen de ruido es pequeño. 8. Indique el valor que considere más cercano para la corriente IIH en CMOS: a) 1pA b) 1nA c) 1uA d) 1mA e) 1A f) Nula 9. Indique el valor que considere más cercano para la corriente IIH en TTL: a. 1pA b. 1nA c. 1mA d. 1uA e. 1 A f. Nula 10. Las familias lógicas han evolucionado respondiendo a la demanda del mercado, tratando de mejorar su arquitectura interna ó sus parámetros tecnológicos. Uno de estos adelantos se muestra en la sig. figura , de la cual podemos decir: A. Se trata de la familia HTL ó de alta inmunidad al ruido. Esta característica está dada por el transistor Q7 y el diodo D2. . Pues si las entradas x, y, z están conectadas a la salida de compuertas en cero, es decir a valores de Vce(sat) de los transistores de salida, para que un ruido presente en cualquiera de ellas haga cambiar el estado lógico de la salida, es necesario superar el valor de tensión de D2.. B. Se trata de la la familia TTL standard con salida en tercer estado, donde la entrada z es en realidad un control de habilitación (Enable)de alta impedancia (HI-Z) llevando al corte a Q3 y Q 4 a través de la correcta polarización de Q5 , Q6 , Q7 y el diodo D2. C. Se trata de la familia TTL standard, pero como con las mejoras tecnológicas desarrolladas se pueden llegar a realizar compuertas con mayor cantidad de entradas, como esta NAND de tres entradas. Además se incluye una innovación en la entrada protegidas con diodos polarizados inversos, de manera que si se aplica un voltaje negativo se evita el deterioro de la compuerta. D. Se trata de la la familia TTL de alta velocidad, donde la entrada z es en realidad un control de aceleración de conmutación, pues al colocar a cero la misma, impide que el transistor multiemisor Q1 y el divisor de fase Q 2 llequen a saturarse y por lo tanto conmuten al corte más rápidamente desalojando el exceso de cargas almacenadas en la base a través del transistor Q7 . 11. En CMOS se prefiere utilizar NAND en vez de NOR, sobretodo cuando el FAN IN es alto, explique porque. 12. Cuando la frecuencia es alta, es cierto que CMOS disipa más potencia que TTL?. Justifique la respuesta. 13. Porque no se puede realizar la estructura llamada “Y por conexión” con compuertas en tecnología TTL, con salida Totem Pole ? Graficar. 14. Si hablamos de cualquier tecnología, cuales son los efectos que se producen al sobrecargar una salida más allá del FAN OUT típico ¿? 15. Las familias lógicas MOS han evolucionado notablemente, para concluir con una de las familias lógicas más populares, como es la MOS complemetaria , COS/MOS ó simplemente CMOS. De la cual podemos decir: A. Se obtiene a través de la combinación de transistores MOS canal P, uno de enriquecimiento y uno de empobrecimiento, lográndose así alta velocidad y disminución de la potencia consumida. B. Se obtiene a través de la combinación de transistores canal P y de canal N en un mismo montaje, uno de enriquecimiento y el otro de empobrecimiento, lográndose así alta integrabilidad y disminución de a potencia consumida, entre otras características. C. Se obtiene a través de la combinación de transistores MOS canal N, uno de enriquecimiento y uno de empobrecimiento, lográndose así alta velocidad debido a la movilidad de los electrones en ambos tipos de transistores. D. Se obtiene a través de la combinación de transistores canal P y de canal N en un mismo montaje, ambos con la misma técnica de fabricación del cristal, ambos de enriquecimiento ó de empobrecimiento, lográndose así alta integrabilidad y disminución de la potencia consumida entre otras características. 16. Si necesita cargar una salida TTL con un relay de 50 mA, utiliza: A. B. C. D. Salida TTL estándar Salida TTL colector abierto Salida TTL Totem Pole Cualquiera pero coloca un transistor excitador. 17. Entre las tecnologías TTL, ECL y CMOS, indique cual es la más rápida. Justifique la respuesta. 18. Comparando las tecnologías Justifique la respuesta. TTL y CMOS, indique cual tiene mayor FAN 19. Trate de explicar porqué el Tiempo de Propagación y la Potencia Dinámica son parámetros opuestos, es decir que si pretendemos tiempos pequeños tendremos potencias grandes. 21. En el circuito de la figura indicar cuando la salida de la compuerta TTL es un “1” lógico las tensiones medidas entre: a) unión salida compuerta Nand TTL/emisor Q1 y masa (V1) . b) Union anodo de D1 / R2 y masa (V2), y c) colector , Q1 /R3 /entrada compuerta CMOS y masa (V3) IN. 23. En el circuito de la figura indicar cuando la salida de la compuerta TTL es un “0” logico las tensiones medidas entre: a) union salida compuerta Nand TTL/emisor 2n2222 y masa (V1) b) Union anodo de D1 / R2 y masa (V2), y c) colector , Q1 /R3/entrada compuerta CMOS y masa (V3)