Flip-Flops sincronizado por reloj

Anuncio

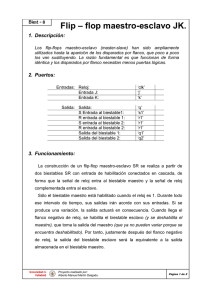

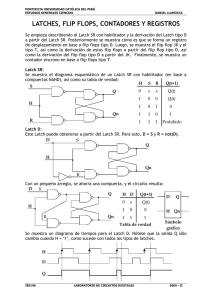

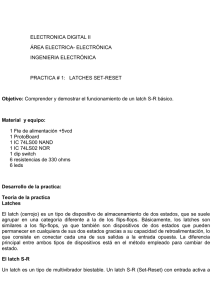

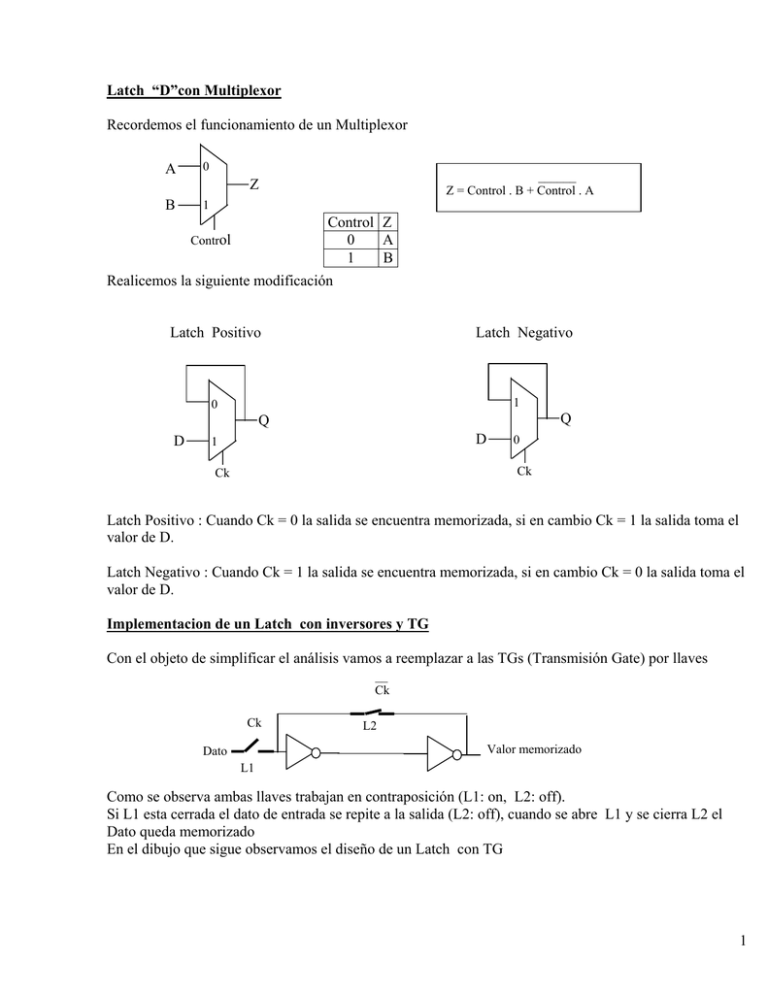

Latch “D”con Multiplexor Recordemos el funcionamiento de un Multiplexor A 0 ______ Z = Control . B + Control . A Z B 1 Control Z 0 A 1 B Control Realicemos la siguiente modificación Latch Positivo Latch Negativo 1 0 Q Q D D 1 0 Ck Ck Latch Positivo : Cuando Ck = 0 la salida se encuentra memorizada, si en cambio Ck = 1 la salida toma el valor de D. Latch Negativo : Cuando Ck = 1 la salida se encuentra memorizada, si en cambio Ck = 0 la salida toma el valor de D. Implementacion de un Latch con inversores y TG Con el objeto de simplificar el análisis vamos a reemplazar a las TGs (Transmisión Gate) por llaves __ Ck Ck L2 Valor memorizado Dato L1 Como se observa ambas llaves trabajan en contraposición (L1: on, L2: off). Si L1 esta cerrada el dato de entrada se repite a la salida (L2: off), cuando se abre L1 y se cierra L2 el Dato queda memorizado En el dibujo que sigue observamos el diseño de un Latch con TG 1 Las siguientes configuraciones nos muestran un Latch que memoriza cuando el pulso de reloj esta en alto (biestable negativo) o cuando el pulso de reloj esta en bajo (biestable positivo) 2 Latch vs FF disparado por flanco. Supongamos el siguiente diagrama temporal a la entrada de ambos dispositivos y observemos las Diferencias a las salidas Qo D Q1 Ck ---- Qo FF disparado por Flanco D Ck ---- Q1 Biestable Latch 3 Flip-Flops sincronizado por reloj La mayoria dispara por flanco (borde) y el símbolo que los identifica es Entradas Sincronas Q Entradas Sincronas Q Ck Ck --- --- Q Q Flanco Positivo Flanco Negativo Tiempos de establecimiento y retención (Setup, Hold Time) Entrada síncrona Ck ts Establecimiento tH Retención Los fabricantes establecen un tiempo mínimo, que de no cumplirse no se asegura el correcto funcionamiento del FF Valores típicos : ts : 5 a 20 nseg tH : 0 a 5 nseg 4 Biestable SR disparado por flanco (Edge Triggered) S Q Ck CONFORMADOR DETECTOR DE FLANCOS C’k _ Q R Circuito conformador/detector de flancos __ Ck Ck __ Ck Ck C’k C’k Ck __ Ck Ck __ Ck tpd C’k C’k FLANCO POSITIVO FLANCO NEGATIVO Para facilitar el análisis hemos supuesto que las compuertas AND y NOR son ideales por lo que tpd = 0. No así para el INVERSOR Toggle Flip Flop El funcionamiento de un FF en el modo toggle indica que su salida se complementa cada vez que ingresa un pulso de reloj. Tomemos por ejemplo el Biestable disparado por flanco y realicemos la siguiente modificacion: Conectemos la entra S a la salida Q negada y la entrada R a la salida Q S Q C’k Ck DT _ Q Salida Salida Presente Futura Qt Qt+1 0 1 1 0 R DT: Detector de Flanco 5 Ck 1 2 3 4 5 6 7 8 9 10 11 12 Q Diagrama temporal Toggle FF Flip Flop D Se obtiene un Flip Flop tipo D realizando la siguiente modificación al Biestable S R D Q C’k Ck DT _ Q Entrada Salida Presente Futura D Qt+1 0 0 1 1 Flip Flop JK Se obtiene un Flip Flop tipo JK realizando la siguiente modificación al Toggle Flip Flop. J Q C’k Ck DT _ Q Entrada Salida Presente Futura J K Qt+1 0 0 Qt 0 1 0 1 0 1 1 1 Qt (negado) K Entradas Asíncronas Las entradas asíncronas son mandatorias, no requieren el concurso del pulso de reloj para actuar sobre el circuito. Cuando se activa una entrada asíncrona la salida Q se posiciona según sea la entrada activada. Si se activa la entrada Set (S) la salida Q va a uno (Q=1). Si en cambio activamos la entrada Reset (R), la salida Q va a cero (Q=0). Veamos la aplicación en un FFJK 6 _ S J Entradas Asincronas S R 1 1 1 1 1 1 1 1 0 1 1 0 0 0 Q C’k Ck DT _ Q K Entrada Salida Presente Futura J K Qt+1 0 0 Qt 0 1 0 1 0 1 1 1 Qt (negado) x x 1 x x 0 x x No permitido _ R Flip-Flops conectados en cascada Supongamos la siguiente configuración de FFs disparados por flanco 1 J1 Q1 J2 Ck 1 Ck --- K1 Q2 --- Q1 Condiciones Iniciales: CI: Q1 = 1 ; K2 Q2 Q2 = 0 El funcionamiento correcto es el indicado en la siguiente figura CK Q1 (J2) Q2 tpHL (Q1) tpLH (Q2) Para que ello ocurra tpHL debe ser mayor a tH (tpHL > tH ) de Q2, cosa que ciertamente se cumple, si ello no ocurriera la respuesta de Q2 seria incierta. Los FFs actuales tienen un tH < 5 nseg., tendiendo a 0 nseg Flip-Flops Maestro Esclavo (Master-Slave) Actualmente el FF Maestro Esclavo es obsoleto y su configuración se muestra a continuación 7