Descarga

Anuncio

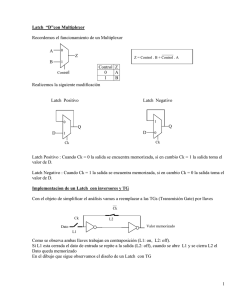

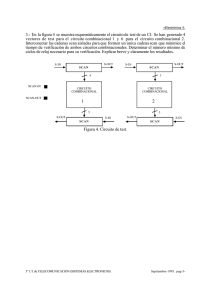

Tema Tema 4 4 Introducción Introducción aa los los Sistemas Sistemas yy Circuitos Circuitos Secuenciales Secuenciales 1 Tema 4: Introducción a los Sistemas y Circuitos Secuenciales 4.1. Sistemas secuenciales síncronos y asíncronos. 4.2. Elementos básicos de memoria: Biestables 4.3. Registros 4.4. Contadores 4.5. Memorias de acceso aleatorio (RAM). 2 4.1. Sistema Secuencial Modelo general E N x1 T x2 R A xm D A S . . . CIRCUITO COMBINACIONAL ESTADOS y1 B1 .. .. z1 z2 zm S A L I D A S ESTADOS Y1 PRÓXIMOS y2 B2 Y2 . . . yn Bn Una misma combinación de entradas puede generar distinta salida ya que el estado puede ser distinto dependiendo de la historia de las entradas La historia pasada de las entradas está representada en el estado que posea el circuito Yn 3 4.1. Sistema Secuencial E N x1 T x2 R A xm D A S ESTADOS . . . CIRCUITO COMBINACIONAL y1 B1 Y1 .. .. z1 z2 zm S A L I D A S ESTADOS PRÓXIMOS y2 B2 Y2 . . . yn Bn Yn •El valor de las salidas zi depende, a través de la función de salida que implementa el circuito combinacional, no sólo de los valores actuales de las entradas xi, sino también del contenido actual de los elementos de memoria •En estos elementos, lo que se almacena es el llamado estado actual del sistema secuencial (registro histórico). •El paso desde el estado actual del sistema a un estado siguiente, viene a su vez definido por la llamada función de transición de estados [que depende de los valores actuales de las entradas y del estado actual]. 4 Sistema Secuencial Síncrono Los Lossistemas sistemassecuenciales secuencialespueden puedenser: ser: síncronos síncronosyyasíncronos asíncronos S z1 A L z2 I zm D A S E •Sistema Secuencial N x1 T x2 Síncrono: es aquel R sistema secuencial en A xm el que los cambios de D A estado se producen S cuando se recibe una señal de activación a través de una entrada ESTADOS especial del sistema, PRESENTES denominada “entrada de reloj”. . . . CIRCUITO COMBINACIONAL .. .. ESTADOS . . . Elementos de memoria . . . PRÓXIMOS 5 RELOJ Sistema Secuencial Síncrono: Señal de Reloj Tiempo de bajada RELOJ POSITIVO: Reloj tr tf tA tI t T Tiempo de subida Tiempo de actividad Periodo del reloj: tiempo que transcurre entre dos pulsaciones del reloj Tiempo de inactividad 6 Sistema Secuencial Síncrono: Señal de Reloj R eloj tr tf tA tI t T •Sistemas Activados por Nivel: es necesario que su señal de activación alcance el nivel alto para que se produzcan los cambios de estado en el sistema. RELOJ S.S. Síncrono activo a nivel alto RELOJ S.S. Síncrono activo a nivel bajo 7 Sistema Secuencial Síncrono: Señal de Reloj R eloj tr tf tA tI t T •Sistemas Activados por Flanco (de subida o bajada): los cambios de estado se producen únicamente durante los flancos de subida o de bajada de la señal de activación del sistema RELOJ S.S. Síncrono activo por flanco de subida RELOJ S.S. Síncrono activo por flanco de bajada 8 4.1. Sistema Secuencial •Sistema Secuencial Asíncrono: es aquel sistema secuencial en el que los cambios de estado se producen cuando cambia alguna de sus entradas, sin necesidad de que se active por una señal de reloj. De esta forma, el cambio en las salidas se produce de forma inmediata en respuesta al cambio en las entradas. 9 4.2. Biestables ¾Latch ¾Latch (cerrojo) (cerrojo) con con inversores inversores ¾Latch ¾Latch SR SR Asíncrono Asíncrono ¾Con ¾Con puertas puertas NOR NOR ¾Con ¾Con puertas puertas NAND NAND ¾Latch ¾Latch SR SR Síncrono Síncrono ¾Con ¾Con entradas entradas Asíncronas Asíncronas ¾Latch ¾Latch D D Síncrono Síncrono ¾Flip-Flop ¾Flip-Flop D D Master-Slave Master-Slave ¾Flip-Flop ¾Flip-Flop J-K J-K ¾Flip-Flop ¾Flip-Flop TT 10 4.2. Biestables • Circuito secuencial con dos estados estables (salida a 0 y salida a 1) en los que se pueden mantener indefinidamente. • Objetivo: almacenar un bit (memoria). ¿Cómo almacenar un bit en un circuito? 11 Latch (cerrojo) con inversores ¡Haciendo que de vueltas y vueltas sin encontrar la salida! Q 1 0 Q No podemos modificar el estado de forma fiable: no existen terminales separados de lectura y 12 escritura Latch SR (NOR) ¿Cómo cambiar el estado del biestable? = 0 Q Q 0 = Q Q 0 13 Latch SR (NOR) • Latch SR con puertas NOR S Q R Q Símbolo lógico R 0 (puesta a 0) S (puesta a 1) 0 Q El estado se mantiene Q Diagrama lógico 14 Latch SR (NOR) • Latch SR con puertas NOR S Q R Q Símbolo lógico 1 R Q (puesta a 0) 0 1Q 0 S (puesta a 1) 15 Diagrama lógico Latch SR (NOR) • Latch SR con puertas NOR S Q R Q Símbolo lógico R 0 (puesta a 0) S (puesta a 1) Q 1 1 0Q Diagrama lógico 16 Latch SR (NOR) • Latch SR con puertas NOR S Q R Q Símbolo lógico 1 R Q (puesta a 0) 0Q 1 S (puesta a 1) SITUACION NO DESEADA 0 17 Diagrama lógico Latch SR (NOR) S Q R Q Símbolo lógico S 0 0 0 0 1 1 1 1 R 0 0 1 1 0 0 1 1 Q(t) 0 1 0 1 0 1 0 1 Q(t+1) 0 1 0 0 1 1 * * /Q(t+1) 1 0 1 1 0 0 * * Tabla de transición expandida. * indica situación no deseada S 0 0 1 1 R Q(t+1) /Q(t+1) 0 Q(t) /Q(t) 1 0 1 0 1 0 1 * * Tabla de transiciones comprimida. * indica situación no deseada 18 Latch SR (NOR) CRONOGRAMA S R Q /Q S 0 0 1 1 R Q(t+1) /Q(t+1) 0 Q(t) /Q(t) 1 0 1 0 1 0 1 * * 19 Tabla de transiciones comprimida. * indica situación no deseada Latch SR (NAND) Latch S-R con puertas NAND: las entradas S y R se activan ahora por nivel bajo S Q R Q Símbolo lógico /S 0 0 1 1 /S Q En tecnología TTL las puertas NAND se prefieren a las NOR /R Q Diagrama lógico /R Q (t+1) /Q (t+1) 0 * * 1 1 0 0 0 1 1 Q (t) /Q (t) Tabla de transición comprimida. * indica situación no deseada Cronograma de funcionamiento 20 Latch SR (NAND) LATCH SR (NAND) S Q R Q Q=/Q=1 No deseado 21 Latch SR Síncrono Los Latches-SR vistos hasta ahora son: • Activos por nivel (‘latches’) • Asíncronos Vamos a añadir una señal de reloj al Latch-SR anterior RELOJ S C R Q Q Símbolo lógico 22 Latch SR Síncrono S S C R C Q (Reloj) R Símbolo lógico C 1 1 1 1 0 S 0 0 1 1 X Q Q Q Diagrama lógico R Q(t+1) /Q(t+1) 0 Q(t) /Q(t) 1 0 1 0 1 0 1 * * X Q(t) /Q(t) Tabla de transición comprimida. * indica situación no deseada Cronograma de funcionamiento ¿Y con el LatchRS NOR? 23 Latch SR Síncrono con Entradas Asíncronas • Biestable S-R síncrono con entradas asíncronas – CLEAR: puesta a cero asíncrona y – PRESET: puesta a uno asíncrona • Tienen prioridad sobre las señales de reloj y permiten poner el estado a uno o a cero /CLEAR S PR Q S C R CL Q Q C (Reloj) Símbolo lógico Latch SR Síncrono activo por nivel alto de reloj, con entradas asíncronas PRESET y CLEAR activas por nivel bajo Q R /PRESET Diagrama lógico 24 Latch D Síncrono • Biestable D activado por nivel Se utilizan para la implementación de elementos de memoria, cuya única finalidad es almacenar el valor de una línea de información (un bit) D C Q Q Símbolo lógico C 0 1 1 D C S C R Q Q Diagrama lógico D Q(t+1) /Q(t+1) X Q(t) /Q(t) 1 1 0 0 0 1 Tabla de transición Cronograma (activado por nivel alto) 25 FLIP-FLOPS Los Latches son biestables activos por nivel: Problema: si hay un pulso no deseado en la entrada de datos Ö el pulso no deseado se trasladará a la salida. Necesitamos un elemento de almacenamiento que no pueda cambiar su estado más de una vez durante un ciclo de reloj Solución: biestables activos por flanco 26 Flip-Flop D Maestro-Esclavo • Biestable D activado por flanco de bajada – Para implementar biestables que se activen por flanco se utiliza con frecuencia la configuración MASTER-SLAVE (o maestro - esclavo) D D Q CLK Q D X X 1 0 Q Qm D Q maestro esclavo C C Q Q CLK Símbolo lógico CLK 0 1 ↓ ↓ D Q(t+1) Q(t) Q(t) 1 0 /Q(t+1) /Q(t) /Q(t) 0 1 Diagrama lógico 27 Tabla de transición Flip-Flop D Maestro-Esclavo D D Q D Q C Q C Q CLK Diagrama lógico 28 Cronograma (activado por flanco de bajada) Flip-Flop D Maestro-Esclavo Flip-Flop D M-S activado por flanco de subida D Q D D Q D Q C Q C Q CLK Q Símbolo lógico CLK Diagrama lógico CLK 0 1 ↑ ↑ D X X 1 0 Q(t+1) Q(t) Q(t) 1 0 /Q(t+1) /Q(t) /Q(t) 0 1 Tabla de verdad 29 Biestable J-K • Problema del Biestable S-R: – Situación indeseada cuando S=R=1 • Solución: – Determinar un estado cuando se dé esta situación, por ejemplo que el biestable cambie de estado (Q(t+1)=Q(t)) J va a actuar como la S del biestable RS K va a actuar como la R del biestable RS 30 FlipFlop J-K a partir del FF D FF JK activado por flanco de subida CLK 0 1 ↑ ↑ ↑ ↑ J X X 0 0 1 1 J K K Q(t+1) /Q(t+1) X Q(t) /Q(t) X Q(t) /Q(t) 0 Q(t) /Q(t) 1 0 1 0 1 0 1 /Q(t) Q(t) Circuito combinacional D Q CLK Q D = QJ + QK Q\JK 0 1 00 0 1 01 0 0 11 1 0 10 1 1 Tabla de verdad K J D Q CLK Q 31 FlipFlop J-K a partir del FF D J Q CLK Q K Símbolo lógico K J D Q CLK Q 32 Cronograma (activado por flanco de subida) FlipFlop J-K a partir del FF D • Biestable JK activado por flanco de bajada – Utilizaríamos un biestable D activado por flanco de bajada – Las puertas lógicas añadidas y las conexiones realizadas serían las mismas que en el caso anterior – Igual que en los biestables D, los biestables J-K comerciales disponen de entradas asíncronas J Q CLK Q K Símbolo lógico 33 FlipFlop T a partir del FF J-K • Mantiene el estado o lo cambia (dependiendo del valor de T) cada vez que se activa • No se construye comercialmente, se puede implementar utilizando un biestable J-K : T Q CLK Q Símbolo lógico T J Q CLK Q K Diagrama lógico CLK 0 1 ↑ ↑ T Q(t+1) /Q(t+1) X Q(t) /Q(t) X Q(t) /Q(t) 1 /Q(t) Q(t) 0 Q(t) /Q(t) Tabla de verdad 34