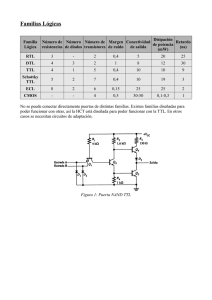

Familia lógica CMOS

Anuncio